基于FPGA的数字扩频接收机的设计与实现

2015-09-09张阿宁高冲霄

张阿宁 高冲霄

摘要:随着数字化时代的飞速发展,对于具有良好性能指标的数字直接扩频系统在各个通信领域有着广泛的应用,该文介绍一种基于FPGA的数字化直扩接收机的设计与实现,它采用优化的数字匹配滤波器来实现扩频序列的同步捕获,大大减小了系统的资源;通过在跟踪环路中加入特殊的环路滤波器使得接收机跟踪的性能得到提高;同时由于接收机中关键模块采用了参数化设计,这使得系统有非常大的灵活性。

关键词:扩频系统;接收机;数字匹配滤波器;差分解调;FPGA

中图分类号:TN851 文献标识码:A 文章编号:1009-3044(2015)03-0252-03

Design and Implementation of Spread Spectrum Digital Receiver Based on FPGA

ZHANG A-ning, GAO Chong-xiao

(Department of Electronic Engineering, Xian University of Posts & Telecommunications,XIan 710121,China)

Abstract: With the rapid development of the digital age, to have good performance of digital direct spread spectrum system has been widely used in various communication domain, this paper introduces a digital spread spectrum receiver based on FPGA, the design and implementation of its optimization of digital matched filter is used to realize in acquisition of spread spectrum sequence, greatly reduces the system's resources;By adding special loop filter makes the receiver tracking loop tracking performance was improved;At the same time due to key in the receiver module uses the parametric design, which makes the system has great flexibility.

Key words: spread spectrum system; receiver; digital matched filter; differential demodulation; FPGA

1 概述

随着数字化时代的飞速发展,数字化的直接扩频接收机以其优良的性能、小型的体积和较小的功耗已经逐步取代传统的模拟直接扩频接收机,数字接收机通常的实现方法可归纳为三种:1)基于专用芯片的数字化接收机;2)基于DSP处理的软件无线电接收机[1];3)基于FPGA的全数字化接收机[2]。基于专用芯片的数字化接收机设计开发的周期短,集成度高,可以获得较高的性价比,但工作方式受专用芯片的限制,灵活性较小。基于DSP处理的软件无线电接收机,以高速的数据处理能力,先进的组织体系结构,在通信等领域得到了较广泛的应用,缺点是DSP数据吞吐率较低,DSP掌握起来比较困难,开发周期较长。而对于基于FPGA的全数字化接收机,其以可编程门阵列(FPGA, Field Programmable Gate Array)为核心,而FPGA的编程方式简便先进、高速,且有高可靠性、开发简捷、开发周期短的诸多特点。因此,在数字接收机的设计中得到越来越广泛的应用。

2 直扩数字接收机的数学模型

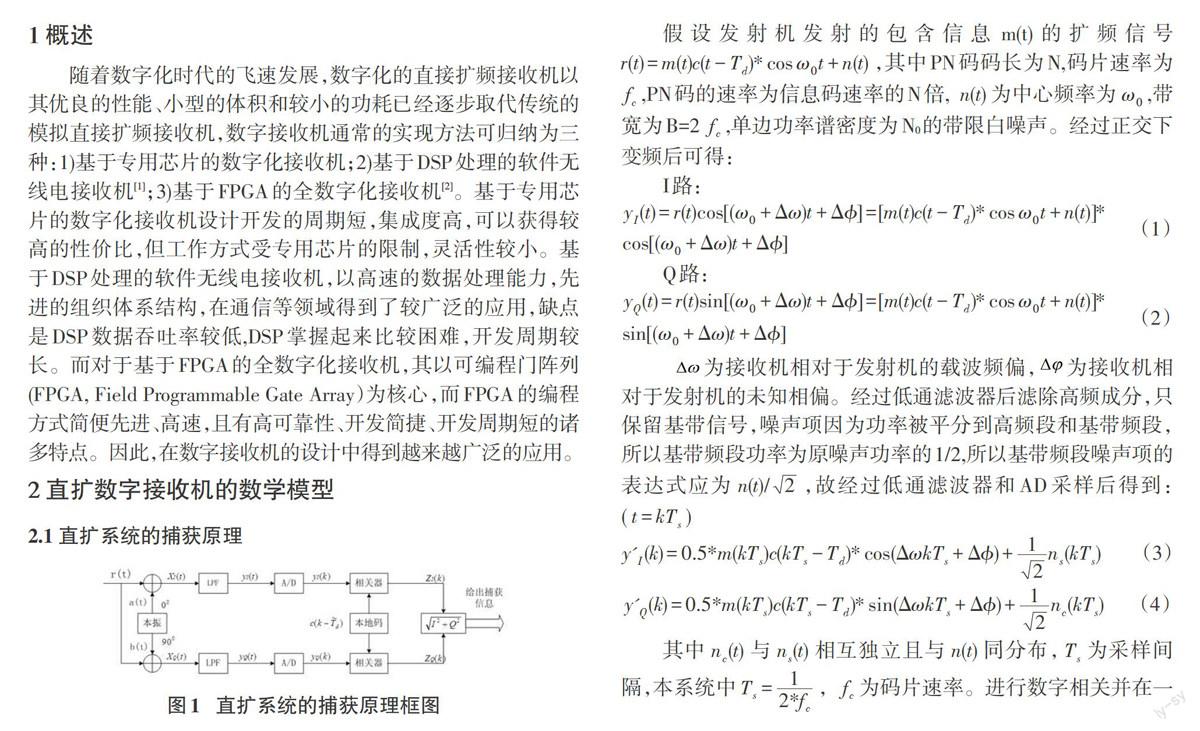

2.1 直扩系统的捕获原理

图1 直扩系统的捕获原理框图

假设发射机发射的包含信息m(t)的扩频信号[r(t)=m(t)c(t-Td)*cosω0t+n(t)],其中PN码码长为N,码片速率为[fc],PN码的速率为信息码速率的N倍, [n(t)]为中心频率为[ω0],带宽为B=2[fc],单边功率谱密度为N0的带限白噪声。经过正交下变频后可得:

I路:

[yI(t)=r(t)cos[(ω0+Δω)t+Δ?]=[m(t)c(t-Td)*cosω0t+n(t)]*cos[(ω0+Δω)t+Δ?]] (1)

Q路:

[yQ(t)=r(t)sin[(ω0+Δω)t+Δ?]=[m(t)c(t-Td)*cosω0t+n(t)]*sin[(ω0+Δω)t+Δ?]] (2)

[y'I(k)=0.5*m(kTs)c(kTs-Td)*cos(ΔωkTs+Δ?)+12ns(kTs)] (3)

[y'Q(k)=0.5*m(kTs)c(kTs-Td)*sin(ΔωkTs+Δ?)+12nc(kTs)] (4)

其中[nc(t)]与[ns(t)]相互独立且与[n(t)]同分布,[Ts]为采样间隔,本系统中[Ts=12*fc], [fc]为码片速率。进行数字相关并在一个数据码元内分别对I,Q支路进行累加求和且求平均可得:

[ZI(k)=12Nk=ii+2N-1[0.5*m(kTs)*c(kTs-Td)*c(kTs-Td)*cos(ΔωkTs+Δ?)+12ns(kTs)*c(kTs-Td)]] (5)

[ZQ(k)=12Nk=ii+2N-1[0.5*m(kTs)*c(kTs-Nd)*c(kTs-Td)*sin(ΔωkTs+Δ?)+12nc(kTs)*c(kTs-Td)]] (6)

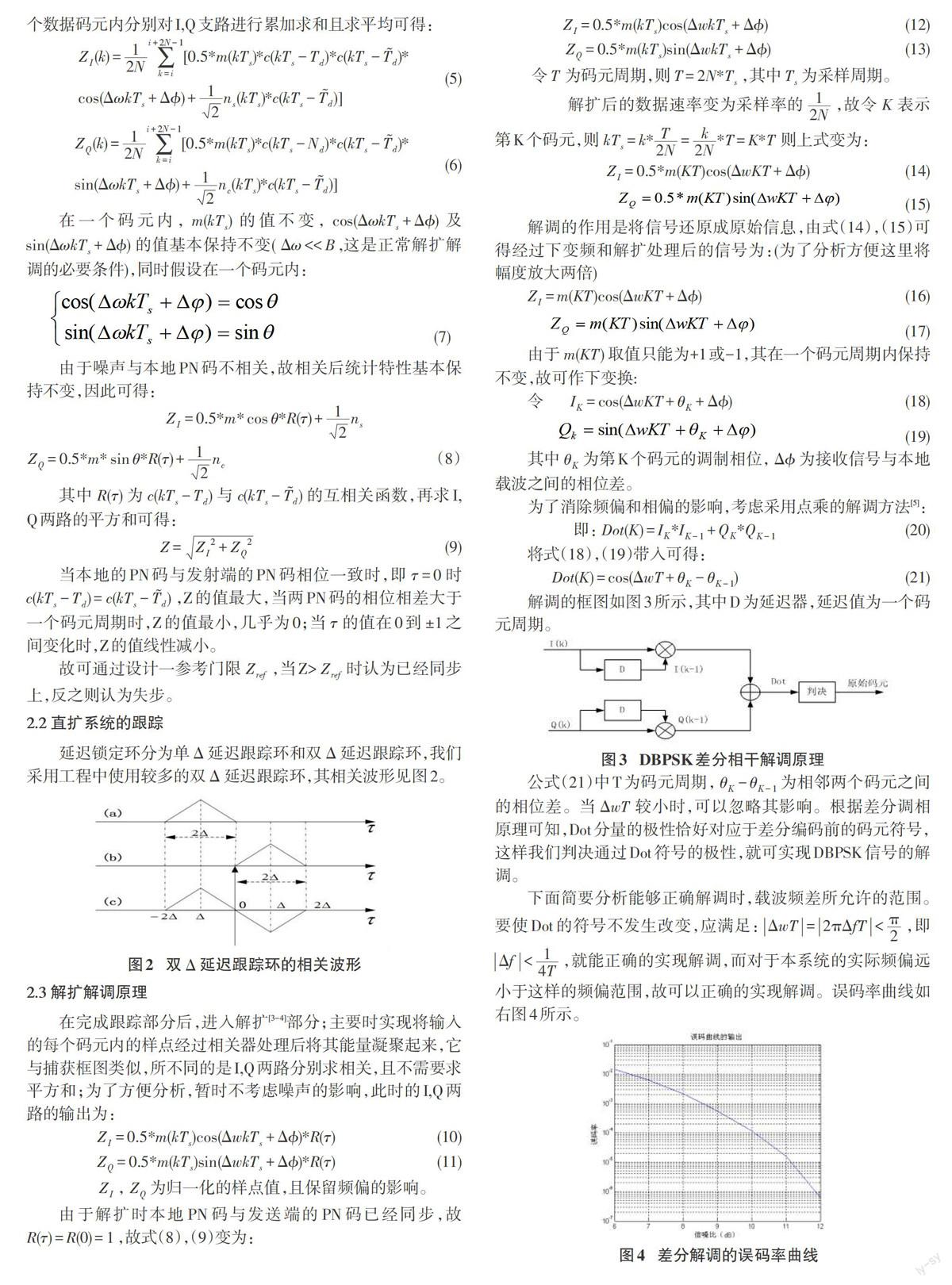

在一个码元内,[m(kTs)]的值不变,[cos(ΔωkTs+Δ?)]及[sin(ΔωkTs+Δ?)]的值基本保持不变([Δω< [] 由于噪声与本地PN码不相关,故相关后统计特性基本保持不变,因此可得: [][ZI=0.5*m*cosθ*R(τ)+12ns][ZQ=0.5*m*sinθ*R(τ)+12nc] (8) 其中[R(τ)]为[c(kTs-Td)]与[c(kTs-Td)]的互相关函数,再求I,Q两路的平方和可得: [Z=ZI2+ZQ2] (9) 当本地的PN码与发射端的PN码相位一致时,即[τ=0]时[c(kTs-Td)=][c(kTs-Td)],Z的值最大,当两PN码的相位相差大于一个码元周期时,Z的值最小,几乎为0;当[τ]的值在0到[±1]之间变化时,Z的值线性减小。 故可通过设计一参考门限[Zref],当Z>[Zref]时认为已经同步上,反之则认为失步。 2.2 直扩系统的跟踪 延迟锁定环分为单[Δ]延迟跟踪环和双[Δ]延迟跟踪环,我们采用工程中使用较多的双[Δ]延迟跟踪环,其相关波形见图2。 图2 双[Δ]延迟跟踪环的相关波形 2.3 解扩解调原理 在完成跟踪部分后,进入解扩[3-4]部分;主要时实现将输入的每个码元内的样点经过相关器处理后将其能量凝聚起来,它与捕获框图类似,所不同的是I,Q两路分别求相关,且不需要求平方和;为了方便分析,暂时不考虑噪声的影响,此时的I,Q两路的输出为: [ZI=0.5*m(kTs)cos(ΔwkTs+Δ?)*R(τ)] (10) [ZQ=0.5*m(kTs)sin(ΔwkTs+Δ?)*R(τ)] (11) [][ZI],[ZQ]为归一化的样点值,且保留频偏的影响。 由于解扩时本地PN码与发送端的PN码已经同步,故[R(τ)=R(0)=1],故式(8),(9)变为: [ZI=0.5*m(kTs)cos(ΔwkTs+Δ?)] (12) [ZQ=0.5*m(kTs)sin(ΔwkTs+Δ?)] (13) 令[T]为码元周期,则[T=2N*Ts],其中[Ts]为采样周期。 []解扩后的数据速率变为采样率的[12N],故令[K]表示第K个码元,则[kTs=k*T2N=k2N*T=K*T]则上式变为: [ZI=0.5*m(KT)cos(ΔwKT+Δ?)] (14) 解调的作用是将信号还原成原始信息,由式(14),(15)可得经过下变频和解扩处理后的信号为:(为了分析方便这里将幅度放大两倍) [ZI=m(KT)cos(ΔwKT+Δ?)] (16) 由于[m(KT)]取值只能为+1或-1,其在一个码元周期内保持不变,故可作下变换: 令[IK=cos(ΔwKT+θK+Δ?)] (18) 其中[θK]为第K个码元的调制相位,[Δ?]为接收信号与本地载波之间的相位差。 为了消除频偏和相偏的影响,考虑采用点乘的解调方法[5]: 即:[Dot(K)=IK*IK-1+QK*QK-1] (20) 将式(18),(19)带入可得: [Dot(K)=cos(ΔwT+θK-θK-1)] (21) 解调的框图如图3所示,其中D为延迟器,延迟值为一个码元周期。 图3 DBPSK差分相干解调原理 公式(21)中T为码元周期,[θK-θK-1]为相邻两个码元之间的相位差。当[ΔwT]较小时,可以忽略其影响。根据差分调相原理可知,Dot分量的极性恰好对应于差分编码前的码元符号,这样我们判决通过Dot符号的极性,就可实现DBPSK信号的解调。 下面简要分析能够正确解调时,载波频差所允许的范围。要使Dot的符号不发生改变,应满足:[ΔwT=2πΔfT<π2],即[Δf<14T],就能正确的实现解调,而对于本系统的实际频偏远小于这样的频偏范围,故可以正确的实现解调。误码率曲线如右图4所示。

3 直扩数字接收机的设计方案

3.1 直扩数字接收机的结构框图

图5 直扩数字接收机的结构框图

其中接收机的主要处理单元包括数字匹配滤波器、功率检测器、跟踪环路、频偏估计与校正和解扩解调器

3.2 直扩数字接收机的各个处理单元

3.2.1 FEP前后项预处理模块

实现原理如图6所示。由文献[6]中可知,在信噪比比较低时,量化取3bit时已经足够,故将接收到信号先经过截断得到3bit位宽的信号,这3bit数据先经过FEP处理后得到4bit。经过FEP的处理使得输入得I路信号和Q路信号在每个切普内的强度平均化了,即:[FEPout=FEPin(1+Z-1)]

这样处理的主要目的是为了实现基带采样速率和接收信号的伪随机码速率异步工作。即使移位时钟和基带信号之间有较大的相位差,两个相关峰中总有一个主导地位。这种方法回避了扩频通信中需要精确的伪码同步这一难题。但需要指出的是,基带采样速率的二分频和伪码速率之间不能有大的频差,一般应该控制在晶体振荡频率稳定度的精度以内。

3.2.2 数字匹配滤波器

数字匹配滤波器是扩频码捕获电路的核心单元,它也是电路资源消耗最大的模块,故其速度和功耗是其设计主要考虑的因素。常用的匹配滤波有一般型简单的匹配滤波器、倒置型FIR滤波器、折叠型匹配滤波器和并行的匹配滤波器,文献[7-8]中对这几种滤波器的实现原理进行了详尽的分析,其中并行匹配滤波器所消耗的资源较小,实现的复杂度也较低,结合本设计的目的,选用并行匹配滤波器。原理框图如图7所示。

图7 并行的匹配滤波器实现原理框图

仿真波形:

1) 未加FEP时,且信号含有50Hz频偏时的测试结果如图8所示。

图8 未加FEP时数字匹配滤波器的仿真输出

由以上仿真波形可以看出,两路匹配滤波器的输出均表现出了正确地结果(在I_mf_result为两个-448处)同时可以看出由于频偏的影响,I,Q两路相关峰值不同步。

2) 加FEP时,且信号含有50Hz频偏时的测试结果如图9所示。

图9 加FEP时数字匹配滤波器的仿真输出

由以上仿真波形可以看出,两路匹配滤波器的输出也均表现出了正确地结果(在I_mf_result为-896处,即将一个码片内两个样点的能量凝聚起来了)。同时可以看出由于频偏的影响,I,Q两路相关峰值不同步。

上面的数字滤波器在设计时,可以对PN码进行参数化实际,这样系统在调用该匹配滤波器时,可以灵活的配置相关的PN码参数。

3.2.3 跟踪模块

系统搜索到同步后,即进入跟踪环节,跟踪环路的实现原理框图如下图10。

图10 跟踪环路的实现原理框图

跟踪电路的核心是一对超前-滞后相关器组成。接收端的相关器同时工作,计算相关值。本地产生的PN码先经过一个三级的移位寄存器,这样即可得到超前、当前和滞后三个状态,而跟踪电路模块利用超前和滞后的PN码和数据进行相关处理,然后通过误差放大电路和环路滤波器,得到的误差信号若超过调整门限则通过改变可控分频器的分频比从而加速或减慢本地的PN码的时钟频率。

环路滤波器使用LPF数字滤波器,可以有效的降低噪声系统对跟踪系统的影响。

3.2.4 解扩解调器

在进行准确的同步和较稳定的跟踪环路后,信号进入解扩解调器,最终完成信号的解扩解调。解扩解调器的主要模块为相关器和差分解调单元,图11给出其原理框图。

解扩解调端用跟踪环路得到较准确的PN码相位来对I,Q两路数据分别求相关值,得到的每一个码元的相关值不进行判决,直接送给差分解调单元,在解调后再进行判决,从而恢复原始信息码元。

图11 解扩解调器的原理框图

3.2.5 系统联调结果

图12 差分解调模块的输出波形

从上图中可以看出从读入数据,到最终解调数据的输出,共有三个时钟周期的处理时延,同时也可以看出,解调出的数据与信源发出的数据相同(信号源产生的原始码元为方波)。

同时经过长时间的验证测试,所得到的误码率曲线与图4基本一致。

4 总结

本文经过系统级的算法推导,给出了整个数字扩频接收机实现原理;结合系统设计要求,给出了基于FPGA芯片的直接扩频数字接收机的设计与实现,详细设计和描述了各个关键模块的实现原理,通过FPGA的设计仿真,经过对接收数据的同步、跟踪、解扩、解调,最终实现了原始信息码元的恢复。

参考文献:

[1] 楼才义,徐建良,杨小牛. 软件无线电原理与应用[M]. 2版. 北京:电子工业出版社,2014.

[2] 郭黎利,李北明,窦峥. 扩频通信系统的FPAG设计[M]. 北京:国防工业出版社,2013.

[3] 托列里. 扩展频谱通信系统原理[M]. 牛英滔, 译. 北京:国防工业出版社,2014.

[4] 徐威, 郑小保. BPSK直扩接收的多相关解扩方法研究[J]. 无线电通信技术,2014(10).

[5] Stephen G Wilson. Digital Modulation and Coding[M]. 北京:电子工业出版社,1998.

[6] 徐欣, 林畅. 利用Matlab分析量化比特数对采样信号波形的影响[J].信息系统工程,2011(9).

[7] 杜慧敏,赵全良. 基于Verilog的FPGA设计基础[M]. 西安:西安电子科技大学出版社,2006.

[8] 何在民, 胡永辉, 魏敬法, 等. 基于FPGA的数字匹配滤波器的实现[J]. 时间频率学报, 2008(2).