标准数字CMOS工艺正交压控振荡器设计

2015-09-06潘达杉等

潘达杉等

摘要:正交压控振荡器是高速链路中的一个关键部件.片上集成高质量品质的电感电容等无源器件是影响压控振荡器性能的关键因素.为了兼容传统的数字工艺,采用超深亚微米的数字CMOS工艺进行片上电感电容的集成,并基于此无源器件实现了基于电容耦合的正交压控振荡器,实现中心频率16.12 GHz,频率调节范围为10 %,1M频偏处的相位噪声为-112 dBc,相位误差小于0.39°.

关键词:QVCO; phase noise;CMOS工艺

中图分类号:TP302 文献标识码:A

Design of Quadrature VCO Based on Standard CMOS Process

PAN Dashan1, HUANG Jinming2, FENG Yong2,MIN Hao1

(1.State Key Laboratory of ASIC and System, Fudan Univ, Shanghai200433, China;

2.Shanghai High Performance IC Design Center, Shanghai201204, China)

Abstract:Quadrature VCO is one of the key components in high speed data link. High Q onchip inductance and capacitance integration is a key fact, which highly affects the performance of Voltage Controlled Oscillator. In order to fully compact the traditional digital CMOS process, we have designed onchip inductance and capacitance with ultradeep submicron digital CMOS process, based on which a capacitive coupling quadrature VCO is implemented. According to the simulation, the center frequency of QVCO is 16.12GHz, with 10% frequency tuning range, 112dBc@ 1MHz phase noise and 0.39°phase error.

Key words:quadrature voltagecontrolled oscillator;phase noise; CMOS technology

超级计算机的研究者们越来越多的将研究重点聚焦在系统的高能效而不单单是系统的峰值性能.因此,单芯片集成多核心的发展方向取代了追求单芯片单核心频率提升的发展方向.单芯片可以集成的核心数量随着工艺特征尺寸的下降而增多,核心间的数据通信逐渐成为制约芯片整体性能的关键因素,提高处理器核心间数据通路的聚合带宽成为设计者的一个研究重点.高传输率的通信接口必将成为多核处理器的关键部件.UCLA的Frank等人在2007年左右提出了射频互连(RFI)该方案可以进行单芯片集成,达到单数据通路>10 Gbps的传输率[1].该方案的原理是将基带数据调制到更高频带的载波上,通过数字频带数字基带同时传输来提高单数据链路的聚合带宽.该射频互连系统的一个重要模块是生成载波的振荡源.

为了避免单数据链路各频带间的干扰,通常需要将载波间的频率间隔设计为远远高于基带频率.对于差分传输系统来说,一个相位误差小的正交压控振荡器(以下简称QVCO)有利于提高系统的信噪比,因而改善其信噪比.

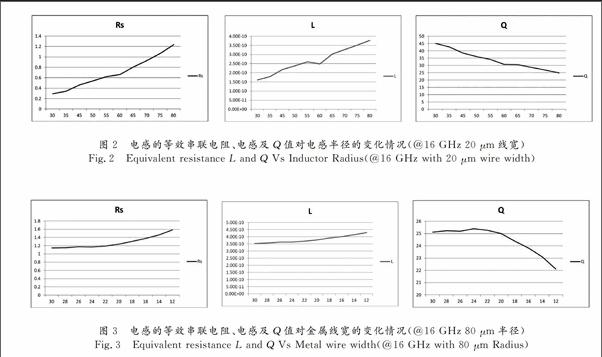

一般来说,高频压控振荡器采用电感电容谐振来实现.电感电容压控振荡器(以下简称LCVCO)的性能由电感电容谐振腔的品质因数来决定.因此单芯片集成LCVCO的设计难点在于高品质片上电感电容的设计.通常Foundry提供的RF CMOS工艺会对金属互连进行优化比如提高高层金属的厚度等.因此为了实现高品质因数的无源器件,设计者都会采用RF COMS工艺.对于数模芯片来说需要在单芯片上采用多种工艺,生产成本非常高.随着数模混合的需求的增长,很多射频模块有了数字实现的方案,因此采用标准的数字CMOS工艺来实现射频模块必将大大降低生产成本.本文采用超深亚微米标准数字CMOS工艺进行了片上电容电感的集成,并设计实现了中心频率为16 GHz,低相位噪声,低相位误差的QVCO.

本文的主要内容安排如下:第二节介绍QVCO的结构;第三节介绍片上无源器件的设计和QVCO的电路设计;第四节介绍QVCO的仿真结果;第五节为总结.

正交信号的产生有多种方式,比如RCRC相移网络、正交分频器等等.对于QVCO的实现,目前最有吸引力的实现方式是通过两个对称LCVCO的耦合来实现[6-8].传统的基于MOS管耦合的QVCO其相位误差因受到耦合管不对称的影响变大,并且需要消耗更多的功耗[9-10].为了降低功耗同时保证低相位噪声,采用硅体耦合技术[11],采用这种方式来降低相位误差.Sanjeev Jain[12]采用背栅耦合进一步降低了AMPM的转换噪声,通过采用PMOS耦合避免了谐振腔Q值降低.

考虑到相位噪声、功耗和面积约束,本设计采用通过共源点电容直接耦合的方式,既实现了耦合又成为2倍频滤波电路的一部分,降低了相噪,同时保证了正交相位的精确性.其结构如下图1所示.

2QVCO的设计

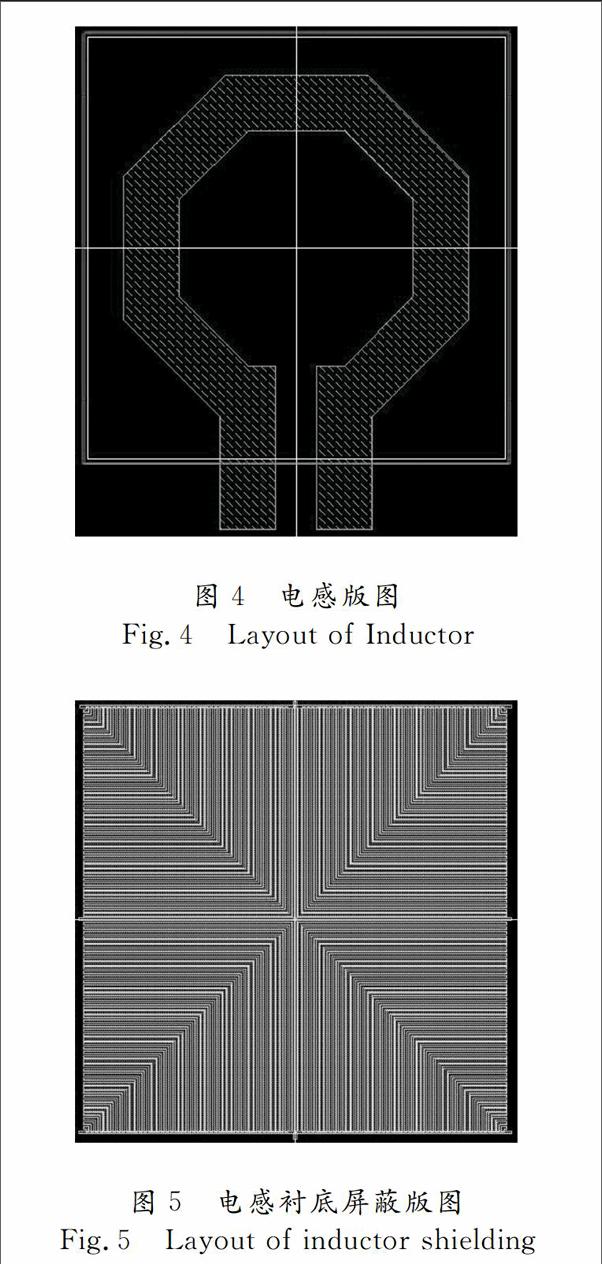

QVCO的设计主要是片上电感电容设计、互补交叉对管设计等.