EDMA传输机制与系统实时性的教学设计

2015-07-05程云鹏

江 汉,程云鹏,沈 良

(解放军理工大学通信工程学院国家短波通信技术工程中心,江苏南京210007)

0 引言

随着新的数字信号处理理论和算法的不断涌现以及现代微电子技术的长足进步,使得实时数字信号处理成为可能。实时处理一般是指在规定的时间间隔内必须完成相应的处理运算,如果超出规定的处理周期,系统将不能正常工作[1]。

基于数据存储方式的算法性能分析和离线仿真一般很少考虑系统的实时性,但在基于实际信号采样的硬件系统中实时性就显得非常重要,是设计中必须考虑的指标。提高系统实时性的途径除了优化算法本身,减少运算量之外;另外一条有效措施是合理设计数据流搬移与处理的机制,其中涉及到的关键技术之一是采用直接内存访问DMA(Direct Memory Access)机制的数据存取方式,它可以在没有处理器参与的情况下自动完成不同存储空间的数据搬移[2]。深刻理解DMA机制对系统实时性的影响对于设计合理的实时数据流处理结构和优化系统实时性非常重要。但依据以往教学经验,学生掌握这部分知识需要扎实的理论基础和较强的系统分析能力;纯粹的理论教学很难把DMA流程阐述清楚。

本文针对研究生课程“实时数字信号处理”教学中存在的难题,着重讨论了增强型直接内存访问EDMA(Enhanced Direct Memory Access)机制对于系统实时性的影响,提出了一种基于乒乓双缓存的数据流结构;在基于DSK6416硬件实验板上给出了一种系统实时性定量测量方法,通过测量结果给出了满足实时性的最佳参数组合。

1 实时性与数据传输结构

1.1 系统实时性

基于实时采样数据流处理要求所支持的算法在时间上是实时的,如果按照单个样点的处理方式,即在两采样点之间必须完成运算过程,此时处理器完成一些复杂算法将变得异常困难,特别是一些高采样率的应用,将几乎不可能。

图1给出了基于单个采样点(Sample by Sample)处理和基于块(Block by Block)处理方式的区别,其中tp是算法的处理时间,ts是采样周期(样点间隔时间)。在图1(a)中基于采样点处理系统要满足实时性,必须在接收到下一采样点前完成处理过程并输出当前样点的处理结果,即满足tp<ts,因为留给处理器信号处理时间只有ts这么长,当采样率高而信号处理算法复杂时,基于单个采样点处理机制很难满足实时性要求。基于单个采样点处理机制还有一个明显的缺点:在给定的时间段内,只有一个采样点需要处理,高采样率将频繁中断处理器DSP的流水线操作,产生额外的指令开销,损失了处理时间,降低了处理器效率。

图1 两种数据处理方式示意图

增加信号处理时间tp的有效措施之一就是采用乒乓双缓存(Ping-Pong Buffer)结构,如图1(b)所示。系统输入采样点首先被缓存在Ping缓冲区,Ping缓冲区存满后,输入样点被缓存到Pong缓冲区,同时DSP开始处理Ping缓冲区的数据,处理完毕后输出样本点被缓存在相应的发送缓冲区。当Pong缓冲区存满后,输入样点被切换缓存到Ping缓冲区,DSP开始处理Pong缓冲区的数据,如此循环切换连续工作。

此时留给DSP的处理时间变为tB=NB*ts,其中NB为缓冲器的大小,选择合适的缓存大小NB可以有效地提高系统实时性。以上就是基于块处理方式的基本思想,基于块处理的方式在实时性方面要优于基于采样点处理的方式,而且有些数字信号处理算法本身就是基于块处理结构的,如FFT算法。而对于大多数其他算法利用DSP的单指令周期和无循环开销特性也可优化成基于块处理的方式。

1.2 实时数据传输结构

EDMA是DSP的一种重要数据访问方式。它可以在没有DSP参与的情况下,由EDMA控制器完成DSP存储空间的数据搬移,满足实时处理中高速数据传输的要求。数据搬移的源地址和目的地址可以是片内存储器、片内外设或外部器件[3]。

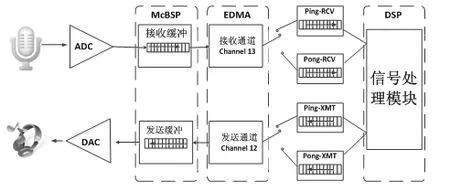

多通道缓冲串口McBSP(Multi-Channel Buffer Serial Port)可以实现与外部信号采样器件的无缝连接,支持多种传输接口,可编程度高,是DSP与外部器件传输数据最常用的片上资源[4]。因此,基于上述EDMA乒乓缓存数据传输方式,本文设计了DMA和McBSP相结合的实时数据传输解决方案,框架如图2所示。

图2 EDMA和McBSP相结合的实时数据传输结构

接收数据时,ADC采样器件的采样数据通过第0号McBSP传到DSP的DRR寄存器中,产生McBSP接收同步事件,触发一次EDMA传输,该事件(REVT0)对应EDMA的通道13,EDMA传输将数据搬入DSP乒乓缓存中。

发送数据时,EDMA从DSP内存中的乒乓缓存中将数据搬入DSP的DXR寄存器,同时利用McBSP发送同步事件,触发一次EDMA传输,该事件(XEVT0)对应EDMA的通道12,将数据通过McBSP传输给DAC器件。

EDMA完成传输时产生EDMA中断,DSP响应该中断,在中断服务程序里重新装载EDMA配置参数PaRAM,触发下一次EDMA传输。

数据传输过程中,为避免数据阻塞和先前采样数据被新来样点覆盖,设计中采用了乒乓缓存技术[5,6]。以接收缓冲区为例,DSP 完成初始化后在其片内存储器(L2 SRAM)中分配 Ping-RCV和Pong-RCV两个接收缓冲区,McBSP接收同步事件触发EDMA传输的目的地址首先设为Ping-RCV缓冲区的首地址,传输完成后在中断服务函数中重载EDMA的参数,使得下次触发EDMA传输时,采样数据搬移的目的地址设为Pong-RCV的首地址;同样在Pong-RCV缓冲区传输完成后,在中断服务函数中重载通道参数,目的地址设为Ping-RCV;利用EDMA的通道参数链接功能,如此反复交替进行。

1.3 EDMA的参数配置

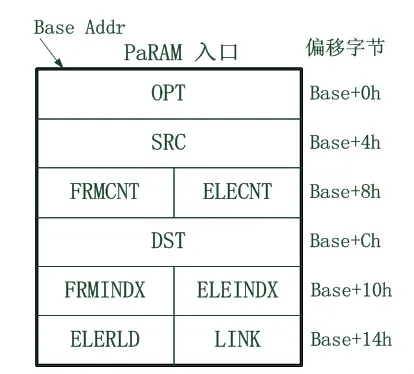

C64x的EDMA控制器基于RAM的结构,每个通道有各自的参数PaRAM(共6个字,24字节),另外有21个重载/链接参数组供链接传输用,共同组成85个可重配的参数RAM组。PaRAM参数的结构如图3所示。

图3 PaRAM参数结构

当参数表中LINK=1时,可以将不同的传输参数组链接起来,形成链接EDMA通道(Chaining EDMA Channel),链接起来的参数组为同一个通道服务,当EDMA一次数据传输完成时,自动根据链接地址重载下一次传输时的配置参数,这种机制通常用于乒乓缓冲、循环缓冲等复杂的数据传输[7]。

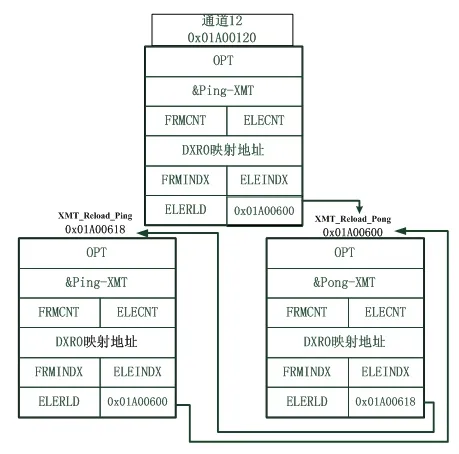

本文设计中采用一维单帧传输模式,通道12完成发送缓冲区(XMT Buffer)到McBSP0的DXR0寄存器之间的数据搬移,其EDMA参数配置与重载链接如图4所示。通道12的EDMA初始配置PaRAM参数(参数组地址0x01A00120h)中的SRC域的值为Ping-XMT缓存的首地址,并按照一个单元长度递增,使能链接功能,目的地址保持为DXR0不变,链接地址(LINK)指向0x01A00600h(用户可以在21个可用重新加载参数组中任意选取处于闲置状态的),该重载参数组(XMT_Reload_Pong)的参数配置与通道12的初始参数配置相似,唯一区别是其SRC域的值改为Pong-XMT缓存的首地址了,其链接地址(LINK)指向通道参数配置组x01A00618(XMT_Reload_Ping),其SRC域的值为Ping-XMT缓存的首地址,链接地址(LINK)指向参数组0x01A00600h(XMT_Reload_Pong)。经过如此配置,当一次EDMA传输完成后,在中断服务函数中实现通道参数的自动重载配置,可交替搬移乒乓缓冲区的数据。

通道13完成McBSP0的DRR0寄存器到接收缓冲器(RCV Buffer)的数据搬移,其参数配置与上述过程基本类似,不再赘述。

图4 PaRAM重载链接配置图

2 系统实时性测试

2.1 测试平台

测试硬件平台是基于DSK6416硬件实验板,实验板上有音频Codec芯片AIC23B,可实现音频信号的采集和回放[8]。测试仪器包括音频信号分析仪U8903A和MSO-X403示波器,其中音频信号分析仪U8903A主要用来测试信号的失真度(THD+N),示波器主要用来测试EDMA机制的传输时延,测试平台如图5所示。

图5 EDMA数据传输机制实时性测试平台

2.2 测试方法

实时性测试的目的是考察EDMA数据传输机制对系统的实时性影响,对于信号处理模块而言,衡量实时性的定量化指标即为留给算法的运算时间。为了测量的方便,在EDMA的中断服务函数中增加负载(Load)函数,通过负载函数运算消耗DSP的时间来比较系统的实时性。负载函数被设计成带参数的空循环运算,函数的参数值代表消耗DSP的运算时间,以微秒为单位。如果系统保持输出信号不失真的条件下能忍耐的Load值越大,说明系统的实时性越好。

另外一个需要测量的指标是EDMA的传输时延Tl,它反映了引入块处理机制后带来的系统时延。在程序启动EDMA传输的起始时刻,把测试管脚(GPIO)置为高电平,在EDMA传输完成后的中断服务函数中把测试管脚置为低电平,使用示波器监测管脚跳变电平的持续时间即为EDMA的传输时间。单次传输测量结果会存在误差,可取多次传输测量的平均值作为测量结果。

2.3 测试流程

使用音频信号分析仪U8903A产生1kHz的正弦波作为测试信号源,经 DSK6416实验板上的AIC23B采集后,采用设计的EDMA乒乓缓冲机制将采集的音频数据搬移到DSP的信号处理模块。C6416的主频配置成720MHz,乒乓缓存区指定在片内存储器(L2 SRAM)上。为简化起见,不对采集的信号做任何运算处理,仅仅拷贝到发送缓冲区(直通操作),通过McBSP的发送通道经过DA变换后输出到音频信号分析仪U8903A的信号分析接口,进行波形失真度测试。

波形失真一般表现为多种形式:谐波失真、互调失真和相位失真等。通常所说的波形失真度为总谐波失真THD(Total Harmonic Distortion)。在实际的测量中还应考虑实际系统引入的噪声N(Noise),所以一般用失真+噪声(THD+N)表示波形失真度,THD+N自然是越小越好。

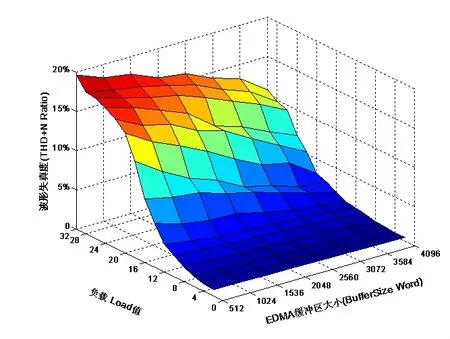

本文重点考虑影响波形失真度的两个重要因素:模拟处理算法运算量大小的负载函数(Load)值和乒乓缓冲区的大小。随着Load值的增加,DSP承受的运算量增加,当Load值超过一定门限后,实际系统输出的信号将会产生失真,可通过测量输出信号的波形失真度来反映Load值对系统实时性的影响。而当Load值一定时,增大乒乓缓冲区的大小即等效于留给DSP的运算时间增长,系统输出信号失真的可能性降低。因此,负载函数(Load)值和缓冲区的大小将共同影响系统的实时性,对于特定的硬件系统,必然存在两种因素最佳的组合值。本文将通过对每一维参数进行多次测量,绘制输出波形失真度随负载函数Load值和缓冲区大小变化的二维曲面图,从而找出最佳组合值。

2.4 测试结果分析

按照上述的测试流程,负载函数的负载值(Load)取值范围为[0:32],步进为4,乒乓缓冲区的大小取值范围为[512,4096],步进为 512个字(32bit)。分别对每一维参数条件下的输出波形进行失真度测量,依据测量结果绘制二维曲面如图6所示。

图6 波形失真度变化曲线图

从图6可看出:波形失真度(THD+N)与负载值(Load)和缓冲区大小两个参数的关系为一个二维曲面,并且存在谷底,与谷底最低值相对应的Load值和缓冲区大小的值即为两者的最佳参数组合值。表1是EDMA的传输时延随乒乓缓冲大小的变化情况,可以看出基本呈线性增长,因此在时延比较敏感的系统设计中,传输时延也是必须考虑的一个重要因素。

表1 传输时延VS乒乓缓冲区大小

3 结语

实时数字信号处理已经成为一门发展迅速的交叉学科,并且成为现代电子技术的核心技术之一。然而,在实际硬件平台上实现这些算法并不是一件容易的事情。本文所提出的基于DSK6416硬件实验板的系统实时性定量测量方法,操作方便,过程清晰,实际教学效果良好。

[1]曹洪龙,胡剑凌,邵雷等.DSP技术课程教学探索与实践[J].南京:电气电子教学学报,2013,35(4):46-51.

[2]郭强,张斌.基于DMA的DSP-Cache优化[J].南京:电气电子教学学报,2009,31(2):50-54.

[3]Texas Instruments Incorporated.TMS320C6000 DSP Enhanced Direct Memory Access(EDMA)Controller Reference Guide[EB/OL].[2004-03].http://focus.ti.com/lit/ug/spru234a/spru234a.pdf.

[4]Texas Instruments Incorporated.TMS320C6000 DSP Multi-channel Buffered Serial Port(McBSP)Reference Guide[EB/OL].[2006-12].http://focus.ti.com/lit/ug/spru580g/spru580g.pdf.

[5]张炜,胡云龙,吴镇扬.DM642的性能极其在视频处理实验中的应用[J].南京:电气电子教学学报,2005,27(5):82-87.

[6]李国锁,杨博,林嘉宇.McBSP和EDMA在实时数据流传输中的配置[J],北京:单片机与嵌入式系统应用2006,4:31-33.

[7]张金昌,李博,詹建华.基于EDMA和MCBSP的实时数据通信设计与应用[J],兰州:化工自动化及仪表,2012,39(3):343-346

[8]Spectrum Digital Incorporated.DSK6416T Technical Reference Rev.A[EB/OL].[2006-12].http://c6000.spectrumdigital.com/dsk6416/