一种级联锁相环频率合成器的设计与实现

2015-06-27简晨王梓宇

简晨,王梓宇

(国家无线电监测中心陕西监测站,陕西西安710299)

一种级联锁相环频率合成器的设计与实现

简晨,王梓宇

(国家无线电监测中心陕西监测站,陕西西安710299)

介绍了锁相环的组成结构,详细分析了锁相环系统各部分产生的相位噪声,结合分析结果给出了一种以双锁相环集成芯片LMK04031为核心实现125 MHz时钟源的频率合成器的设计方法,并给出关键电路的设计。通过调试,产生高性能的频率源,为锁相频率合成的工程应用提供参考。

LMK04031;锁相环;频率合成器;相位噪声

0 引言

频率合成器为现代电子通信系统提供高稳定高性能的频率源,其好坏直接影响通信系统的质量。产生频率源的频率合成技术包括直接频率合成、直接数字频率合成、锁相环频率合成和混合频率合成。本文介绍锁相环系统,对其进行线性相位噪声分析,给出某系统中采用级联锁相环芯片LMK04031产生125 MHz时钟源的设计方法及测试结果。

1 锁相环介绍

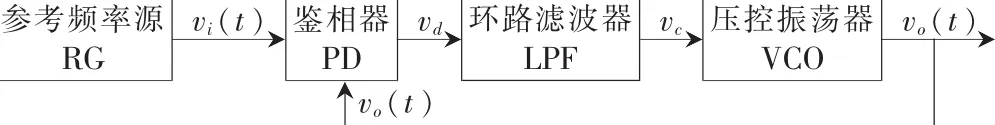

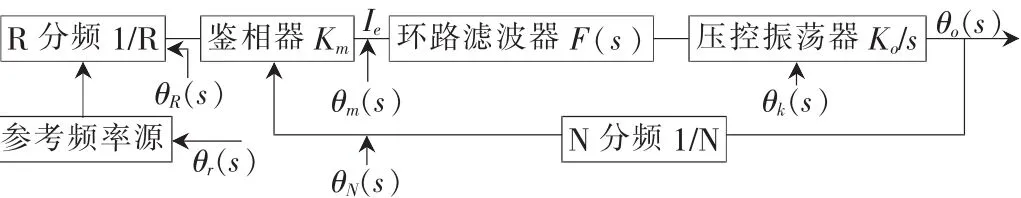

锁相环(PLL)是一个闭环控制系统。主要包括参考频率(RG)、鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)几个部分,如图1所示。通过将参考频率源产生的信号vi(t)与压控振荡器输出反馈回来的信号vo(t)在鉴相器中进行相位比较,产生一个相关的电压信号vd,经过环路滤波滤除毛刺和噪声后变为vc,控制压控振荡器输出频率的变化,形成一个负反馈过程。设参考频率为ωi,输出频率为ωo,在环路锁定时,进入鉴相器中的两个信号频率相等,即ωi=ωo。一般的锁相环电路中,为了得到更高的输出频率,将参考频率R分频,输出频率N分频后送入鉴相器中进行相位比较,则有:

图1 锁相环的基本结构

即输出频率为参考频率的N/R倍。当今市场上的锁相环芯片通常集成N分频器、R分频器、鉴相器和VCO等部分。通过选择合适的参考频率、控制N和R的值便可以得到所需要的输出频率。为了获得较高性能的频率源,也可以采用分立的鉴相器、VCO和分频器等器件。

锁相环可以分为模拟锁相环、数字锁相环和数模混合锁相环。数模锁相环又称电荷泵锁相环,与模拟锁相环相比具有跟踪范围广、捕获时间短和成本低的优点,现今集成锁相环芯片通常采用电荷泵锁相环。通常内部集成鉴相器、分频器和压控振荡器。

2 相位噪声分析

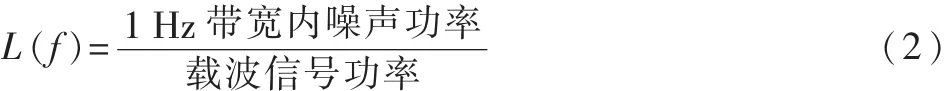

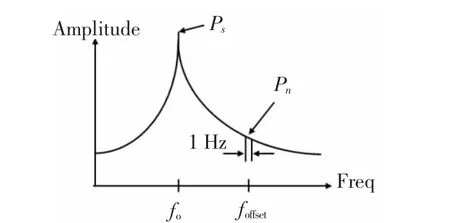

在偏离载波foffset处相位噪声定义为在该频率处1 Hz带宽内的信号功率与载波信号的功率比值,可以用式(2)表示:

如图2所示,载波信号功率为Ps(dBm),偏移载波foffset处1 Hz内信号功率为Pn(dBc/Hz),那么根据式(2),相位噪声可以表示为:

图2 信号的相位噪声

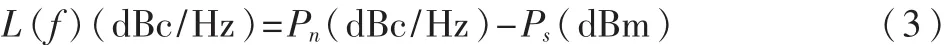

锁相环的相位噪声来源于各个组成部分,包括参考源、鉴相器、压控振荡器及其电路等。锁定条件下,当环路带宽小于鉴相频率的十分之一时,锁相环系统可以看成一个线性系统。对锁相环路进行线性分析,可以得到各部分对输出相位噪声的影响。鉴相器通过比较输入信号与反馈信号,产生一个相位差,与鉴相增益Km相乘,得到误差电流Ie:

再经过环路滤波器转化为直流控制电压Vc:

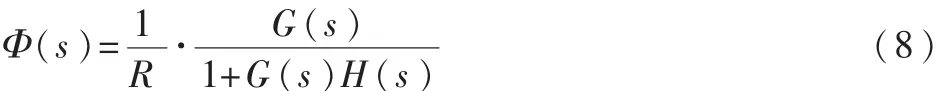

锁相环路线性化模型如图3所示。根据图中各模块的传递函数,可以得到系统的前向增益:

图3 锁相环路线性相位模型

反馈增益:

系统闭环传递函数可以写为:

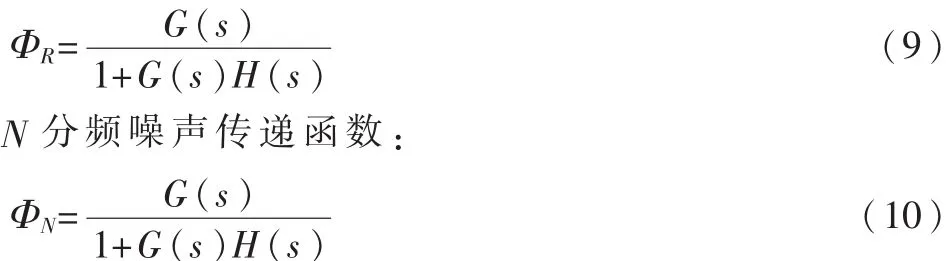

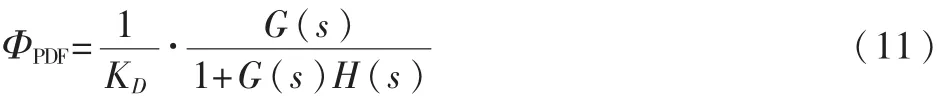

式(8)也可以表示参考频率源部分的噪声对输出噪声产生影响的传递函数。利用传递函数对系统进行噪声分析,可以得到R分频、N分频、鉴相器和VCO对系统输出噪声的影响。

R分频噪声传递函数:

鉴相器噪声传递函数:

VCO噪声传递函数:

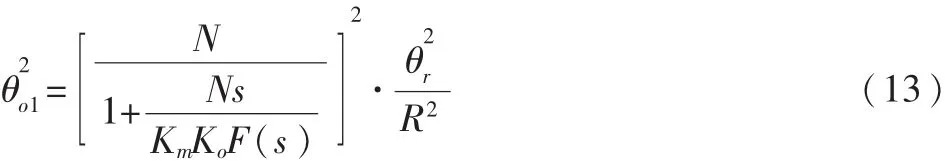

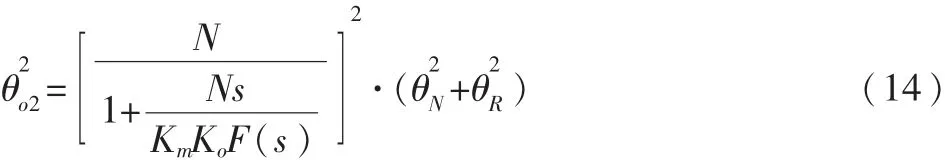

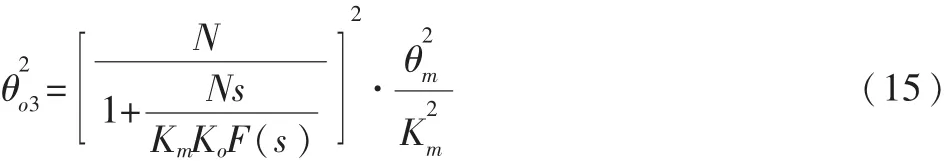

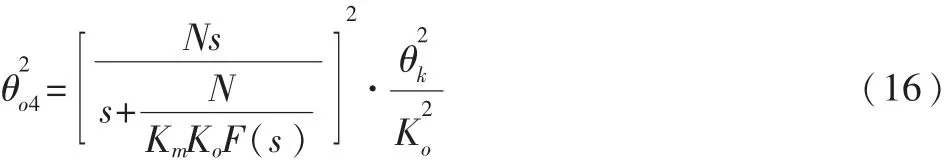

根据式(8),可以得到参考频率源相位噪声对系统输出相位噪声的影响:

分频器R和N产生的相位噪声对系统的影响:

鉴相器产生的相位噪声对系统的影响:

压控振荡器产生的相位噪声对系统的影响:

系统各部分相位噪声对输出相噪的影响:

公共因子对N的变化表现为随N的增大而增大,因此分频器N应选择较小的数,等价于应选择较大的鉴相频率。同样,参数Km和Ko的增大都会导致输出相噪的增大,因此应选调谐系数较小的VCO。鉴相器通常用乘法器代替,选择鉴相增益较小的器件会减小系统相位噪声,通过环路滤波器抑制相位噪声。一般地,环路滤波器的带宽选为鉴相频率的

3 锁相环电路设计

频率源的质量直接影响通信系统的好坏。评价频率源的指标包括相位噪声、杂散、稳定度等。因此设计过程中应从器件选型、环路滤波、电路布局、分频器配置多个方面进行考虑。项目要求获得125 MHz高稳定、低噪声、低杂散的信号。锁相环芯片选择TI公司的LMK04031,参考频率源选择项目中GPS高稳定时钟模块输出的10 MHz信号。

3.1 参考频率源选择

参考频率源为锁相环路提供一个标准,因此它的好坏直接影响输出频率的准确性、稳定度等指标。一般采用晶体振荡器作为参考源。晶振可以分为普通晶振、温补晶振(TCXO)、电压控制晶振(VCXO)、恒温晶振(OCXO)等几种类型。普通晶振价格低、稳定度较差;电压控制晶振输出频率可以随着电压变化而微小变化,通过电压调节输出频率的偏移,解决晶振输出频率随时间而变化的问题;温补晶振和恒温晶振都解决了晶振稳定度随温度变化而产生变化的问题,其中恒温晶振输出频率随温度变化最小,稳定度最高,价格也最昂贵。锁相环频率合成实质上是对参考频率进行倍频,倍频过程会对相位噪声产生影响,见式(13)。因此选择高稳定低相噪的参考源可以改善系统的输出相位噪声。应根据工程指标选择合适的参考时钟。结合成本与指标考虑,本设计采用一款TCXO作为参考时钟。

3.2 LMK04031介绍

LMK04031是TI公司生产的具有级联PLL的低噪声时钟抖动清洁器。它内部集成两个锁相环:锁相环1通过接收外接参考频率源的信号,进行R1分频后,与反馈回鉴相器的外接VCO或VCXO的N1分频信号进行相位比较,锁定后输出的稳定频率信号进入锁相环2中作为参考,再进行R2分频,与内部集成的VCO的N2分频信号进行相位比较。VCO可输出五路差分信号,并且可以进行以2为步进的2~510分频,因而可以输出5路不同频率信号,同时每个通道可以进行以150为步进的0~2 250 ps时延。芯片封装采用48脚WQFN封装,尺寸小,功耗低,使用方便。

寄存器的值可以通过TI公司软件CODELOADER确定。在CODELOADER中输入一系列需要设置的参数,便可得到相应的寄存器值。管脚PLL_MUX可以配置成不同的内容来获得芯片内部的状态。例如配置为PLL1锁定高电平输出,那么此管脚便在PLL1锁定时输出高电平,没有锁定时为低电平。也可以配置为PLL2锁定指示、N分频输出、R分频输出等状态。在调试的过程中通过配置此管脚来确定芯片是否处于正常工作状态。本设计采用FPGA对寄存器进行配置。

3.3 环路滤波器设计

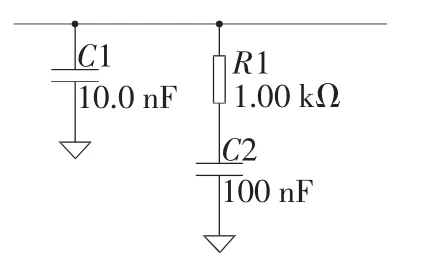

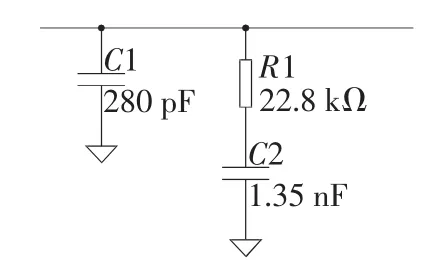

为了获得较好的相噪性能,环路滤波选择无源环路滤波器,因为不含有源器件,因此引入的噪声较有源环路滤波少。锁相环路1的参考频率源为TCXO,噪声较小,因此在锁相环路1中采用较大的环路带宽。而在锁相环路2中,参考频率源为VCXO的锁定输出,根据上述讨论,各部分相位噪声叠加对整体输出有影响,因此环路2中的带宽选择较小一些。采用ADI公司的环路设计软件ADISIMPLL进行环路设计,可以根据环路带宽、鉴相频率、相位裕度这三个参数确定环路滤波器。环路1中,参考频率为10 MHz OCXO,R1分频和N1分频分别为20和50,输出选择25 MHz VCXO,鉴相频率为500 kHz,环路带宽选为鉴相频率的1/10。因此环路滤波器带宽选定为50 kHz,设计电路图见图4。LMK04031内部VCO频率为1 430~1 570 MHz,将输出设为1 500 MHz,经过VCO DIVIDER进行3分频,再进入多通道输出进行4分频便可得到125 MHz输出。环路2中的参考输入为环路1中VCXO的25 MHz输出,VCO输出定1 500 MHz,R2分频和N2分频分别为200 Hz和4 000 Hz,鉴相频率为125 kHz,环路滤波器2的带宽为12.5 kHz,设计电路图见图5。

3.4 电路设计

锁相环系统对噪声十分敏感,因此对芯片的供电采

图4 环路滤波器1设计电路

图5 环路滤波器2设计电路

用线性稳压电源芯片。电路的布局应注意模拟部分与数字部分隔离开来,减小数字部分对模拟部分的影响。环路的布线应尽可能短,高频线要注意阻抗控制。

4 电路调试及结果

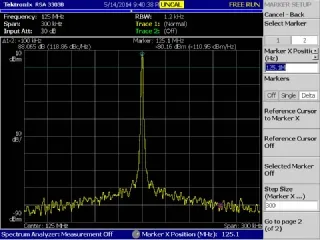

级联锁相环的调试可以分别进行。测试中,通过更改不同寄存器的数据,使得PLL_MUX引脚输出R分频或N分频的结果,利用示波器测试输出的频率是否为设定的鉴相频率,便可得知寄存器是否被正确赋值。通过PLL_MUX输出锁定指示状态可以判断环路是否锁定。两级锁相环可分别调试。设计要求输出125 MHz,在偏离100 kHz处测量其相位噪声,为-110.95 dBc/Hz,如图6所示,达到了设计的要求。

图6 偏离100 kHz的输出相噪

5 结束语

本文首先介绍了锁相环的结构组成,之后通过对系统各部分模块噪声的线性分析,得出锁相环电路设计过程中减小相位噪声的手段:选择性能良好的参考源、选择合适的环路带宽和良好的电路布局布线,最后通过基于LMK04031芯片设计电路的实例给出了锁相环设计的一般性方法。

[1]张厥盛.锁相与频率合成技术[M].成都:电子科技大学出版社,1995.

[2]庄卉,黄苏华,袁国春.锁相与频率合成技术[M].北京:气象出版社,1996.

[3]Texas Instruments Inc.LMK04000 family low-noise clock jitter cleaner with Cascaded PLLs,Technical Datasheet[Z]. 2011.

[4]张涛.锁相环频率合成器建模、设计与实现[D].武汉:华中科技大学,2006.

[5]CAST.锁相环常见问题解答[Z].Analog Devices Inc,2013.

Design and implementation of a cascaded PLLs frequency synthesizer

Jian Chen,Wang Ziyu

(Shannxi Station of State Radio Monitoring Center,Xi′an 710299,China)

The composition structure of the phase-locked loop(PLL)is introduced,and a detailed analysis of the output phase noise generated by the various parts of the system is shown.Based on the results,a 125 MHz clock source is designed with a cascade PLLs integrated chip LMK04031,and the circuits of the loop filters are given.By debugging,the high-performance frequency source is generated.This article can provide a reference for the engineering applications of PLL frequency synthesizer.

LMK04031;PLL;frequency synthesizer;phase noise

TN742.2

:A

:1674-7720(2015)07-0039-03

2014-12-02)

简晨(1987-),男,硕士,助理工程师,主要研究方向:频率合成技术。

王梓宇(1982-),男,硕士,工程师,主要研究方向:无线电监测、测向和定位,软件无线电设计和系统集成。