基于FPGA和ARM的线阵CCD信号采集器的设计

2015-05-21苗长云杨彦利李现国

董 杰,苗长云,杨彦利,李现国

(天津工业大学电子与信息工程学院,天津 300387)

0 引言

线阵CCD以其视场大、分辨率高、价格低廉的特点,已被广泛应用于工业上动态、非接触测量和监测[1]。CCD正常工作需要特定的、精确的驱动脉冲。传统的驱动方法一般采用分立式器件实现,调试困难、灵活性差,而单片机驱动方式虽然编程较为灵活,但驱动频率较低,往往不能满足实际要求[2]。

由于工业现场环境的差异,需要调节CCD的某些特定参数。以单个FPGA作为核心处理器的CCD信号采集系统往往不能满足较为复杂的人机交互需求。现场采集的CCD数据需要远距离传输,而目前大多数线阵CCD信号采集系统多采用USB接口传输,不能组成网络,实现数据的远距离传输[1]。

本设计研制了一种基于FPGA和ARM的线阵CCD信号采集器,实现了线阵CCD信号的采集、存储、处理,以及通过以太网传输到上位机的功能,具有采集信号质量好、可靠性高、传输速率高、人机交互好、组网方便等优点。

1 线阵CCD信号采集器的设计方案

采用以FPGA和ARM联合作为中央处理器的方案。FPGA选用的是XC3S500E,内部含有10476个逻辑单元、1164个可配置逻辑模块、73Kb分布式RAM、360Kb块RAM、20个可选择的18*18的乘法器、232个用户接口和92对差分接口[3]。ARM选用S3C2440芯片,这是一款低功耗、低成本、高性能的精简指令集微处理器。通过ARM强大的片内功能和良好的人机交互能力,可实现数据的高速传输和复杂指令的接收处理。

线阵CCD信号采集器是由线阵CCD,电平匹配模块,模拟前端处理模块、FPGA采集存储模块、ARM处理传输模块和网络接口组成,其组成框图如图1所示。

图1 采集器组成框图

选用TCD1209D线阵CCD为本采集器的图像传感器,FPGA采集存储模块为其提供驱动脉冲时序。CCD输出信号进入模拟前端处理模块,由此输出的数字信号按照奇偶帧,分别写入FPGA的2个双口RAM中。ARM处理传输模块通过由FPGA采集存储模块产生的2个中断信号分别读取2个双口RAM中的数据,并通过网络接口将数据发送至上位机。

2 采集器硬件电路设计

2.1 线阵 CCD

采集器选用TCD1209D线阵CCD。它具有2 048个有效像素,最高驱动频率可达20 MHz[4]。正常工作时,需要外部为其提供准确、特定、严格的驱动时序,分别为转移脉冲SH、相位脉冲Q1、Q2和Q2B、复位脉冲RS和钳位脉冲CP等6路脉冲信号。

采用现场可编程门阵列和外部电平匹配电路驱动线阵CCD工作。通过XC3S500E芯片的通用输入输出管脚为CCD提供驱动脉冲信号。这种通过FPGA为线阵CCD提供驱动脉冲信号方法在硬件上连接简单,在软件上调试容易、灵活性高、移植方便。

2.2 电平匹配电路设计

FPGA的I/O提供的是LVCMOS电平信号,而TCD1209D需要5 V的驱动脉冲,因此需要在两者之间加一级电平匹配。本设计选用的电平匹配芯片是74VHCT04A。

74VHCT04A是一款融合了亚微米硅栅与双层金属布线C2MOS技术的高速CMOS反相器。芯片提供了6路反向输出,可将LVCMOS电平转化为CMOS电平,恰好满足本设计中线阵CCD所需的6路驱动信号。信号在芯片中的传播时延典型值(1 MHz频率下)为4.7 ns,可以满足TCD1209D的驱动信号频率要求。

2.3 模拟前端处理电路设计

TCD1209D输出的是模拟图像信号,目前一般采用集成的模拟前端处理芯片对线阵CCD的输出信号做相应处理。采集器所选的芯片为AD9945。

AD9945是一款应用于电荷耦合器件的模拟信号处理芯片,最高采样频率为40MHz。芯片内部主要由相关双采样(CDS)、10位可调增益放大器(VGA)、低噪声黑电平钳位电路和12位A/D转换器组成[5]。通过为AD9945提供驱动信号可完成芯片的配置,其主要的驱动时序包括:串行数字接口(SCK、SDATA、SL),用于配置操作寄存器、控制寄存器、电平钳位寄存器、可调增益放大寄存器和启动寄存器;相关双采样信号SHP、SHD,数据锁存信号DATACLK;暗电平钳位脉冲CLPOB、预置零脉冲PBLK。

2.4 网络接口电路设计

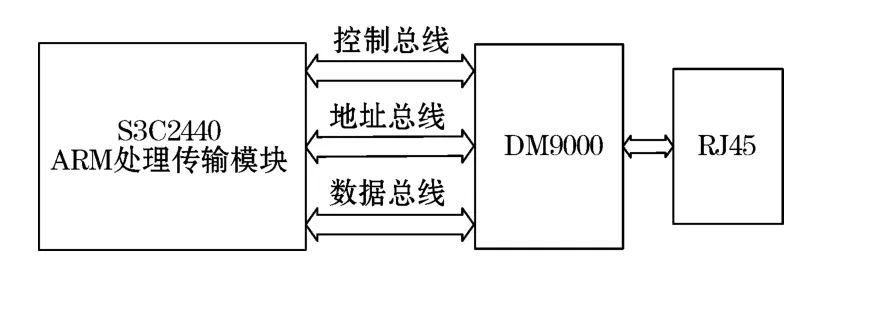

为了通过以太网实现数据的远距离传输,本设计选用的网络接口芯片是DM9000。这是一款拥有通用处理器接口、10/100M自适应功能和4K双字节SRAM的以太网控制器芯片,支持8位、16位、32位不同方式访问。

硬件上DM9000与S3C2440 ARM处理传输模块的控制总线、地址总线、数据总线相连,同时需要连接以太网接头RJ45。连接示意图如图2所示。

3 采集器软件设计

3.1 FPGA软件功能实现

FPGA是采集器中核心处理器之一,主要功能包含驱动线阵CCD工作,配置模拟前端处理芯片,完成数据“乒乓”存储。

图2 DM9000连接示意图[6]

3.1.1 线阵CCD驱动设计

采集器中FPGA所用外部晶振频率为50 MHz,通过内部锁相环将其倍频到80 MHz。CCD所需脉冲信号全部通过80 MHz时钟脉冲计数器CNT得到。由CNT控制时钟脉冲信号周期得到SH脉冲信号。将80 MHz的信号八分频为10 MHz,同时由CNT控制与SH周期关系就可得到Q1脉冲信号。将Q1反向得到Q2和Q2B。通过另一计数器控制占空比,同时由CNT控制周期,得到满足要求的RS与CP脉冲信号。

需要注意的是,在2 048个有效像元输出之前会有32个哑元输出,有效像元输出之后会有8个哑元输出。这一现象不仅会影响以后相关双采样信号与CCD输出信号的关系,而且会对双口RAM存储信号造成影响。

3.1.2 模拟前端处理芯片配置

FPGA需要为模拟前端处理芯片AD9945提供8路配置信号。

内部寄存器配置:对80 MHz基准信号8分频可以得到SCK;当SL为低电平时,应对SDATA写入配置数据,配置数据可通过数据手册得到。

采样信号及时钟配置:数据锁存时钟DATACLK必须与TCD1209D像素输出严格同步,调试时可通过修改FPGA中的代码,同时观察示波器中CCD输出信号完成配置。SHP、SHD占空比为3∶1,利用8分频器中0~7的不同组合得到SHP和SHD。

CLPOB和PBLK主要用于消除CCD输出信号中无效像元的影响,可在TCD1209D输出32个哑元时将CLPOB和PBLK同时置为低电平,PBLK在芯片配置时是可选的。具体调试时,可根据实际情况缩短CLPOB低电平时间,或者不用PBLK功能。

需要注意的是:(1)串行数字时钟SCK的最高频率不得超过10 MHz[7];(2)SHP、SHD的信号频率应与TCD1209D输出信号频率相同,并且应在输出32个哑元之后进行相关双采样;(3)输出的12位数字信号会比信号输入时延迟10个像元输入时间,因此往双口RAM中写数据的使能信号要推迟10个像元时间。

3.1.3 FPGA中数据存储的实现

由于CCD输出信号频率较高,ARM不能对FPGA采集到的数据同时读取。因此,本设计利用FPGA的内部资源,开辟2块宽度为16 bit,深度为2 048的双口RAM,分别存储CCD输出信号的奇数帧与偶数帧数据。

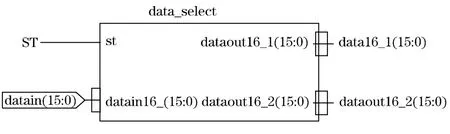

如图3所示,通过data_select模块实现输入数据的奇偶帧分离。其中ST为数据选择信号,由TCD1209D的转移脉冲SH上升沿判断得到;datain为输入的16位数据信号,高四位补为0;data16_1、data16_2分别为奇数帧数据、偶数帧数据。

图3 数据选择模块

采用乒乓操作,对双口RAM1存储奇数帧数据的同时,发送中断2信号通知ARM对存储在双口RAM2中的偶数帧数据进行读取;对双口RAM2存储偶数帧数据的同时,发送中断1信号通知ARM对存储在双口RAM1中的奇数帧数据进行读取。

3.2 FPGA与ARM接口设计

FPGA与ARM总线接口模块如图4所示,arm_hclk为ARM的读时钟信号,arm_nOE为ARM的读使能信号,arm_nGCS为ARM的片选信号,arm_addr_bus为ARM的11位读地址总线。ram_clk、ram_addr分别连接双口RAM1的读时钟与读地址总线,ram_data连接双口RAM1的数据输出,arm_data_bus输出奇数帧数据,为之后与偶数帧数据合并做准备。waddr11_generator模块用于产生写地址信号。偶数帧数据读取模块连接方式与奇数帧相同。

由于ARM计算地址是按8位方式,而此时连接的FPGA是作为一个16位的外部存储器挂载到ARM的总线上[8],因此要将ARM高一位地址线依次连接到FPGA低一位地址线上,否则输出的数据会间隔一个地址输出,造成数据不能正确读取。

图4 FPGA与ARM总线接口模块(奇数帧部分)

3.3 ARM系统及网络功能的实现

为实现工业现场设备组成以太网进行通信的需求,本设计采用ARM嵌入式系统。ARM嵌入式系统具有良好的人机交互功能,方便扩展参数控制接口,而且容易实现网络通信功能。设备可通过网络接口完成网络互联,既可组成局域网,也可连接至互联网,实现指令和数据传输。

从ARM的角度看,FPGA是一段地址连续的16位储存设备。在硬件上,FPGA挂载到了 ARM的 BANK3上,因此,在ARM的0X18000000-0X18003FFFF上分别先后存储了CCD输出信号的奇数帧与偶数帧数据。通过编写ARM裸机程序完成系统初始化、对FPGA总线控制和数据读取,并经过DM9000网络接口芯片,实现数据的以太网传输。

设计所采用的网络通信协议为UDP协议,其优点是[9]:(1)面向无连接的协议,速度快;(2)可使用广播方式多地址发送数据;(3)所占传输网络带宽小。

由于每一帧数据是2 048个像素,每个像素是16 bit,因此一帧数据的大小为4 kB。而UDP数据报的长度最大为1 500 B,因此必须将一帧数据拆分成4部分,即512像素点为一包,一共4包,进行数据传输。同时在数据最后加入2 B的数据标识,1B用作识别是第几帧数据;1 B用作是一帧中的第几包。需要注意的是,每一个像素是16位,在对高8位、低8位拆分并发送时,大小端格式应与网络中的格式相匹配。

4 线阵CCD信号采集系统及实验

4.1 线阵CCD信号采集系统搭建

线阵CCD信号采集系统由线阵CCD信号采集器和上位机测试平台组成。

上位机测试平台由Ethereal软件和基于LABVIEW编写的上位机两部分构成。Ethereal是一种数据包嗅探软件,可以完成对采集器发送的UDP数据包的抓取。基于LABVIEW编写的上位机主要完成将高低8位数据重组为原16位数据并显示的任务。通过将Ethereal抓取到的数据导入基于LABVIEW编写的上位机中,可以完成数据的显示和采集器的测试。

4.2 FPGA程序仿真

XILINX ISE14.1是本采集器中FPGA的开发环境,各模块仿真时序如下所示。图5为FPGA输出到反向器的信号,即TCD1209D所需的各个驱动脉冲的反向信号,其中CLK为系统时钟,SH为反向转移脉冲,Q1、Q2和Q2B是反向相位脉冲,RS是反向复位脉冲,CP是反向钳位脉冲。图6为AD9945所需的驱动脉冲信号。图7为双口RAM所需的时钟信号,其中ST为奇数帧与偶数帧分离信号,WECLK为双口RAM写时钟信号,FRAME_SYN为帧同步信号,WE1、WE2分别为双口RAM1、双口RAM2的写使能信号,RE1、RE2为通知ARM读取数据的中断信号。

图5 TCD1209D反向驱动时序

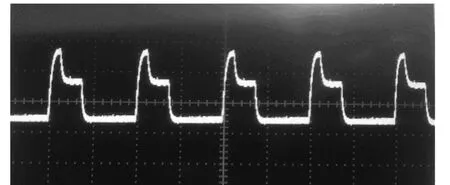

4.3 线阵CCD输出信号实验

为了验证 FPGA产生脉冲信号是否正确,需要测试TCD1209D输出端信号。图8为TCD1209D输出的模拟信号,说明了采集器提供的CCD驱动信号的正确性。

4.4 线阵CCD信号采集系统实验

图6 AD9945驱动时序

图7 读写双口RAM所需的信号

图8 CCD信号输出

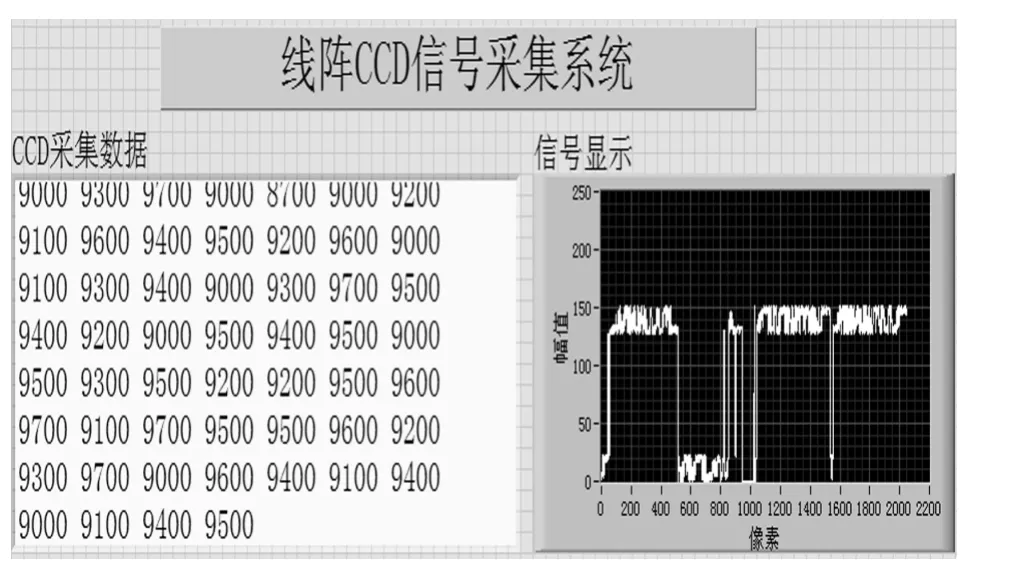

通过对线阵CCD信号采集系统进行实验,可验证线阵CCD信号采集器能否正常工作。实验方法是将线阵CCD部分遮挡,观察传输到上位机数据的显示结果。图9为基于LABVIEW编写的上位机的显示结果。通过显示结果说明,采集器完成了信号的正确采集、存储、处理及通过以太网传输等功能。

5 结束语

图9 上位机显示结果

本设计采用了以FPGA和ARM联合作为中央处理器的设计方案。分析了TCD1209D线阵CCD的驱动时序要求,介绍了使用FPGA产生驱动的方法和过程。讨论了模拟前端处理芯片AD9945的配置方法,阐述了FPGA对信号采集、存储的实现,FPGA和ARM总线接口的实现、ARM系统及网络通信功能的实现。结合网络接口技术,采集器实现了人机交互好、组网方便等优点,在工业生产监测中有广阔的应用前景。但采集器不能通过环境的变化,自动调节某些CCD参数,完成数据的自适应采集,需要以后进一步的研究与完善。

[1]何云龙,彭章君,李众立.基于网络的线阵CCD信号采集系统的设计.仪表技术与传感器,2012(4):85-87.

[2]喻依虎,孟丽娅,岳陈平.基于FPGA的高速线阵CCD的驱动设计.微型机与应用,2013,32(10):26 -28.

[3]孙鑫明.基于以太网的大型锻件多路超声检测器的研究:[学位论文].天津:天津工业大学,2013.

[4]王庆友.图像传感器应用技术.北京:电子工业出版社,2003.

[5]洪冰心,郑力新.一种基于FPGA的AD9945驱动设计.微型机与应用,2011,30(18):23 -25.

[6]李剑雄,张策,杨军.基于ARM和DM9000的网卡接口设计与实现.微计算机信息,2008,24(14):123 -124;138.

[7]ANALOG DEVICES Corp.AD9945 DATASHEET,2013.

[8]陈曦.基于ARM9和FPGA的高速便携式数据采集前端的设计:[学位论文].南京:南京航空航天大学,2010.

[9]孙鑫明,苗长云,白华,等.基于ARM和FPGA的高扩展性超声波检测模块设计与实现.电子技术应用,2012,38(10):26-29.