FPGA/DSP高速稳定雷达发射机设计

2015-05-15张春杰王鹏谭振伟

张春杰,王鹏,谭振伟

哈尔滨工程大学信息与通信工程学院,黑龙江哈尔滨 150001

FPGA/DSP高速稳定雷达发射机设计

张春杰,王鹏,谭振伟

哈尔滨工程大学信息与通信工程学院,黑龙江哈尔滨 150001

针对采用直接数字式频率合成(DDS)芯片无法直接产生多种信号波形的情况,提出基于现场可编程门阵列(FP-GA)和数字信号处理器(DSP)控制DDS来实现高速稳定雷达发射机的设计方案。首先,介绍了直接数字式频率合成的结构和原理。其次,设计了雷达发射机的硬件电路和软件编程,其中为提高雷达系统工作稳定性,保证DSP控制DDS产生稳定的波形信号,特别加入了对DSP工作状态进行监测和控制的模块电路。测试结果表明,设计的雷达发射机能够通过示波器输出稳定、实时的普通连续波、FSK信号、单频脉冲信号等多种波形,信号频率的范围在0~100 MHz,频率稳定度达到1%。

直接数字式频率合成;数字信号处理器;可编程门阵列;高速稳定性;雷达发射机

自从相控阵雷达问世以来,由于其具有测量精度高、观察空域宽、可处理多目标的特点,被广泛应用于预警、制导、搜索等战术场合。而T/R组件是相控阵雷达的核心部件,其技术指标、结构工艺以及成本等因素直接关系到雷达系统的成败[1]。

随着数字技术的不断发展,将直接数字频率合成(DDS)技术引入相控阵雷达系统中,并以其为核心组成全数字T/R模块代替原来由移相器、微波衰减器、不等功率分配器等构成的模拟T/R模块,实现T/R组件的全数字化,从而进一步简化雷达系统结构、缩小雷达整机的体积[2-4]。

文中雷达发射机通过DSP与FPGA联合控制3片DDS芯片高速稳定地产生多种所需的雷达波形,通过串口模块与PC机相连,在上位机界面自由设定参数,增强了系统的实时性和可操作性。经过实际测试,雷达发射机达到了预期目标。

1 DDS的结构与原理

DDS技术是根据奈奎斯特采样定理,从正弦信号相位出发,将该正弦信号采样、量化、编码形成一个正弦函数表存在查询表ROM中。其工作过程为根据时钟脉冲fc,N位相位累加器将频率控制字K循环累加,把相加后的结果通过相位寄存器输出作为取样地址送入波形表存储器。波形表存储器根据这个地址值输出相应的波形数据。最后,经D/A转换和滤波将波形数据转换成所需要的模拟波形输出。

图1 DDS原理框图

普通的正弦波信号S(t)可写成:

当振幅A与初始相位φ不随时间变化时,其频率就由相位唯一确定,即有

式中:Δφ为一个采样周期Δt之间的相位增量,Δφ=K2π/2N,Δt=1/fc。

故系统输出频率即为

式中:fc为系统工作频率,fout为输出频率,K为用户编程的频率控制字,N为累加器的寄存器位数[5-8]。

2 系统设计方案

发射机设计是基于Altera公司的cyclone系列FPGA器件EP2C8Q208C8,配合以TI公司DSP器件TMS320C6416为主处理器的电路模块来控制3片DDS芯片AD9854实现设计要求。首先通过DSP给DDS传送控制字,输入DDS产生波形所需要的参数,送到DDS的I/O口寄存器,等待更新脉冲;而FPGA则控制整个电路的时序;最后给出更新脉冲,通过DSP与FPGA的联合工作完成雷达信号波形的产生。本设计的硬件结构主要有DSP电路、FP-GA电路、串口模块等。发射机硬件结构框图如图2所示。

图2 发射机硬件结构框图

2.1 DSP电路

DSP是本系统中核心控制部分,它的工作状态直接影响到整个系统工作的好坏。为保证DSP工作稳定,特别加入了DSP监控模块,模块设计如图3所示。当监控模块检测出DSP输出的检测信号异常时,检测模块向DSP发送复位信号将其复位为正常工作状态。当DDS芯片输出的信号偏离正常工作频率范围时,DDS检测模块会发出命令,使DSP运行中断程序,进而对DDS进行复位和重新配置。这样就可以使雷达发射机工作可靠性提高,输出更加稳定波形信号。

图3 DSP监控模块

DSP芯片的内部含有锁相环模块,可以通过对锁相环设置来控制时钟倍频,通过倍频可以在输入时钟比较低的情况下,得到高速的系统工作时钟。DSP的倍频设置由CLKMODE1与CLKMODE0共同决定,可通过把开关接到CLKMODE1与CLKMODE0端口来手动调整倍频数。这样就可以自由控制DSP工作频率,进而控制雷达发射机的工作速度。本系统中,利用50 MHz晶振给DSP提供时钟,把倍频系数设置为20时,DSP的工作频率可以达到1 GHz[9]。

表1 DSP倍频模式设置

2.2 FPGA电路

FPGA是现场可编程的高密度数字集成电路。它具有应用快速、使用方便、经济实用以及数字化的特点。发射机利用FPGA芯片EP2C8Q208C8进行译码,形成3片AD9854使能控制信号,分别控制3片AD9854芯片的更新脉冲与复位等信号,从而可以实现对不同芯片的控制[10]。利用FPGA控制整个电路的时序使3片DDS同步工作,这样系统就可以输出满足设计的要求。

图4 FPGA配置框图

2.3 串口电路

串口包括多种类型如RS-232-C、RS-485、RS-422等。其中最常见的是RS-232-C,它的结构比较简单,连接器由9针组成,通信时只要3根线就能完成信号发送和接收,但是由于它通信距离短、速度低的原因限制了它的应用。由于RS-422是差分通信接口,其抗干扰能力强,且传输速度达到10Mbit/s,传输距离也比RS-232远[11]。发射机为了使通信信号更加稳定,所以采用了RS-422和RS-232联合的方式。

图5 串口发送接收

在DSP内部完成SC16C550的芯片配置,SC16C550可以进行串行和并行数据相互转换,它最高速度可达3 Mbit/s,完全满足本设计中低功耗和高速率的需求,并且它的内部包含一个16位FIFO发送和接收器,通过利用内部的FIFO可以使数据传输更加准确快捷。该模块中DS8921作用是进行232电平与422电平的转化,当SC16C550发送信号时,DS8921将发送过来232电平信号转换成422电平信号传送出给上位机;当上位机把信号传送给处理板时,DS8921将传送过来的422电平信号转换成232电平信号传送给串口处理芯片。

2.4 软件设计

雷达发射机软件设计采用QuartusII和CCStud-iov3.3开发软件。并在Microsoft VC++6.0环境下开发上位机界面。本文的研究对象是实现连续波、单频脉冲信号、FSK等信号。软件调试之前必须进行初始化,初始化后需要等待上位机的命令,当上位机指令到达,通过串口传送给DSP,再经由DSP写给DDS,把参数送到DDS寄存器中,等待更新脉冲,最后由FPGA给出更新脉冲实现波形输出。

图6 软件设计流程

3 整机性能测试

首先利用上位机发送不同的频率值,通过频谱仪(Agilent E4402B)观测硬件产生的波形并记录连续波在不同时刻频点的测量值,具体值见表2。

表2 频率测试结果

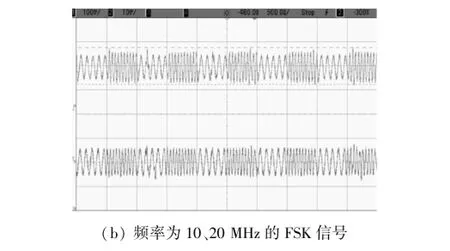

在上位机界面发出产生连续波、单频脉冲、FSK等信号指令,通过示波器(Agilent DSO6054A)截取输出信号的波形图用来分析系统的性能(如图7~9),可以清晰看到波形频率等参数。

图7 连续波信号

图8 FSK信号

图9 单频脉冲信号

从实验结果分析可得到,雷达发射机通过示波器输出连续波,FSK信号和单频脉冲信号等波形曲线光滑,频谱图主谱良好,当信号为100 MHz时没有出现衰减,频率稳定性高,满足指标的需求。

4 结论

综上所述,本文研制成功的雷达发射机之所以具有高速稳定实时的优良性能,是由于采用了基于FPGA/DSP控制DDS技术。与以往设计发射机方案相比较,在整机性能上有3点优点。

1)高速性。同以往用单片机控制DDS芯片相比,DSP芯片TMS320C6416最高时钟速度可达到1 GHz,解决了控制芯片速度不够的缺点,并且DSP芯片具有强大的运算处理能力,可以快速的控制DDS芯片产生多种实际需要的波形。

2)稳定性。同以往用晶体振荡器产生雷达信号的方案相比,通过DDS技术解决了雷达发射机输出信号频率不稳定、频谱纯度不高的问题以及不能改变的缺点。加入了DSP工作监控电路,保证了发射机工作的稳定性。与未添加监控模块的信号发生器相比,在强干扰环境下输出的信号更加稳定,系统正常工作时间也更长。

3)实时性。利用C语言编写上位机软件与串口通信程序,实现了可视化的人机操作界面,可以在上位机界面上自由更改信号参数,由DSP把相应的参数写入DDS芯片,实现实时控制不同信号输出的目的。

由于DDS技术产生的杂散分量比较大,且DDS芯片功耗大、散热性能不好,这些问题都影响着雷达仿真器产生信号的准确性,接下来需要进一步改善DDS芯片的杂散、功耗和散热等问题。

[1]吴曼青,靳学明,谭剑美.相控阵雷达数字T/R组件研究[J].现代雷达,2001,23(2):57-60.

[2]裴英.雷达数字T/R组件自动测试系统设计[J].现代雷达,2013,35(6):73-76.

[3]翟丽君,穆贺强.一种高效雷达信号模拟器[J].现代电子技术,2012,35(12):126-129.

[4]于淑萍,张幸儿.基于FPGA/MCU多功能信号发生器的设计与实现[J].电力自动化设备,2009,12(29):106-108.

[5]邓耀华,吴黎明,张力锴,等.基于FPGA的双DDS任意波发生器设计与杂散噪声抑制方法[J].仪器仪表学报,2009,11(30):2255-2261.

[6]李正周,郑微.基于DSP的脉冲雷达基带信号发生器设计[J].弹箭与制导学报,2011,31(4):240-242.

[7]刘哲,韩焱,姚金杰.基于DDS的多模信号发生器设计[J].计算机测量与控制,2010,18(3):731-733.

[8]杨加一,王海峰,樊来恩.新型雷达信号目标模拟系统的研究[J].航空兵器,2012,12(6):46-48.

[9]任建国.DSP开发技术实例与技巧[M].北京:国防工业出版社,2007:125-129.

[10]褚振勇,翁木云.FPGA设计及应用[M].西安:西安电子科技大学出版社,2002:202-208.

[11]王中训,徐超,王德法.基于VC++6.0的多串口通信方法[J].计算机应用,2008,28(6):254-256.

Design of high-speed stability radar transm itter based on FPGA/DSP

ZHANG Chunjie,WANG Peng,TAN Zhenwei

College of Information and Communication Engineering,Harbin Engineering University,Harbin 150001,China

For using a direct digital frequency synthesis(DDS)chip can not directly produce a variety of signal waveforms,this paper proposes a radar transmitter with high-speed stability,which controls DDS based on field programmable gate array(FPGA)and digital signal processor(DSP).Firstly the paper presents the structure and principle of the direct digital frequency synthesis.Then the hardware circuit and the software programming are de-signed,in which amonitoringmodule is specially added tomonitor and control the DSP working state,so as to en-sure that DSP may control DDS to produce stable waveform signals.Finally,the test result shows that the radar transmittermay output stable,real-time continuous ordinary waves through oscilloscope,FSK signal,single-fre-quency pulse signal and other waveforms.The frequency of the signal is within the range of 0~100MHz,and the frequency stability reaches 1%.

digital frequency synthesis;digital signal processor;field programmable gate array;high-speed stabili-ty;radar transmitter

TN914.2

:A

:1009-671X(2015)01-006-05

10.3969/j.issn.1009-671X.201403003

http://www.cnki.net/kcms/detail/23.1191.U.20150112.1530.006.htm l

2014-03-06.

日期:2015-01-12.

国家自然科学基金资助项目(61301199).

张春杰(1975-),女,副教授,博士;王鹏(1989-),男,硕士研究生.

张春杰,E-mail:chun_jie_zhang@163.com.