基于SOPC及USB键盘的简易电子琴综合设计实验

2015-05-08田淑珍全成斌董代洁

田淑珍,全成斌,董代洁

(清华大学 计算机科学与技术系,北京 100084)

基于SOPC及USB键盘的简易电子琴综合设计实验

田淑珍,全成斌,董代洁

(清华大学 计算机科学与技术系,北京 100084)

介绍了基于SOPC及USB键盘的简易电子琴设计和实现。利用ML402多功能接口板作为实现平台,在ML402接口板上的FPGA片内实现一个带有CPU、数据、指令存储器和内部总线的简单片上系统,并且增加USB接口、音频接口等接口控制器,将USB键盘连到USB接口上作为电子琴琴键,以USB主设备的方式使用ML402接口板,通过编写ML402上的FPGA片内CPU指令代码,控制USB键盘值的读入和键盘音符的播放。

片上可编程系统;USB接口;音频接口;USB键盘

目前,市场上的电子产品设计越来越精密和复杂,大多数电子产品都集成了CPU、各种接口以及系统和应用软件,这种系统级的设计一般都是采用当前流行的片上系统(Soc)或片上可编程系统(SOPC)来设计。SOPC系统设计是在FPGA片内集成包括CPU、总线、数据、指令存储以及输入/输出接口的综合设计,需要设计人员具有底层软硬件开发的综合能力[1]。

xilinx公司的ISE Design Suite /EDK(embedded development ket)嵌入式开发平台用于FPGA 的SOPC开发,开发平台包括了硬件设计和集成、仿真、固件设计与调试、下载等子平台,具有软硬件协同工作的功能[2]。

对于计算机硬件实验课程,利用学过的微机及各种接口原理,结合SOPC设计技术,做一些应用方面的实验,特别是设计一些多接口的综合性实验,能够很好地训练学生的实际工作能力。综合设计能力越强越能适应目前社会对计算机硬软件工程师的要求。

USB接口是PC机外设的主要接口,使PC机的外设接口统一了标准。USB协议代表了计算机外部接口的发展趋势,接口体积变小,串行传输代替并行传输,速度不断提高,USB协议具有层次结构。音频接口是人机交互的主要接口之一,目前的音频播放技术可以采用多通道时分复用技术,并且在利用各种编/解码技术的情况下,可以用较少量的数据播放出更逼真的音质。

下面将介绍一个基于SOPC的USB键盘电子琴综合设计实验。

1 实验设计总体方案

实验涉及的技术包括USB键盘控制,声音数据的存储与读出,播放声音,FPGA可编程和SOPC技术。实验硬件平台采用xilinx公司生产的ML402开发板,开发板的主芯片采用xilinx的FPGA器件,型号是VIRTEX-4系列的XC4VSX35,板上还包含了与FPGA相连的各种外部接口器件,其中USB器件采用CY7C67300,声音器件采用LM4550,存储器为Flash。软件设计平台采用Xilinx公司的ISE Design Suite /EDK。

整个实验呈现出的效果是:当按下USB键盘上指定的按键时,能播放出事先定义好的音符的声音。按这个效果的设计,系统需要:(1)完成对ML402上CY7C67300的操作(读写),以完成接收USB键盘输入的操作;(2)完成对ML402上LM4550的操作(读写),以完成声音的播放和录制;(3)完成对板上至少一个非易失性的存储介质的读写操作,以存放预先定义好的声音播放数据。

设计方案是以USB主设备的方式使用ML402开发板,用一个USB接口键盘作为电子琴的琴键,事先将各个琴键对应的声音数据存入Flash,当有键盘输入时,通过FPGA的控制读入键盘数据,再根据键盘值到Flash查找声音数据,最后通过LM4550完成键盘音符的播放。

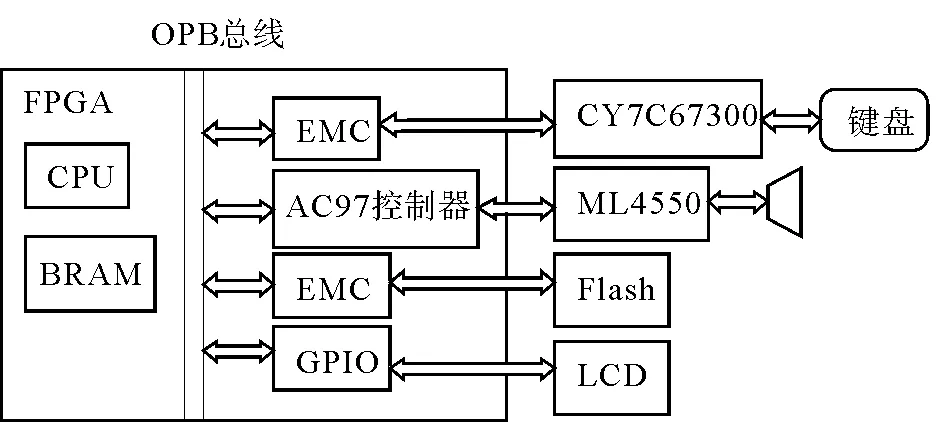

FPGA片内硬件设计选用一个CPU软核MicroBlaze,通过片内总线配上对应的外设控制器IP和外部接口器件配合工作。由于有了CPU,FPGA片内需要设计固件,Xilinx公司的ISE Design Suite /EDK提供了C语言的编译环境,因此,就可以采用C语言编程,使应用程序的开发更为方便。图1是USB键盘电子琴设计框图。

图1 硬件设计框图

2 硬件接口设计及实现

2.1 USB接口

在ML402开发板上使用的USB外部芯片是CY7C67300嵌入式控制芯片。该芯片具有宽泛的硬软件功能,内部具有一个RISC架构的16位处理器CY-16;两个串行接口引擎SIE1和SIE2,每个SIE有两个USB接口:Port A和Port B,可以分别将其设置成主USB或从USB;还有几个外部接口:RS232、I2C、HPI等;器件内部ROM包含EZ-Host BIOS,内部RAM能够被用作存储程序代码和数据[3]。

USB协议的实现基本上是在处理器的软件层面上进行的。CY7C67300的软件结构包含三个层次:BIOS、Framework、应用程序。该BIOS的结构专门针对USB,底层BIOS提供了启动和一个等待硬软件中断的Idle环境;BIOS的上层是一个Framework,包括了一系列的子Framework,每个子Framework负责一个USB功能,为应用层提供了软件接口;应用层通过调用Framework的接口函数来实现需要的USB功能[4],应用程序需要设计人员来编写。

CY7C67300有四种工作模式,在本实验中使用的是HPI模式。在该模式下,内部CPU被当作协处理器,并通过四个端口(地址寄存器、数据寄存器、状态寄存器、双向邮箱)与外部设备通信。同时将USB键盘连接到SIE1上的Part A,并将其设置为主USB模式。

FPGA内部通过一个系统提供的IP Core:EMC与外部CY7C67300的HPI端口连接,EMC是一个通用的存储控制器,同样也可用于对寄存器端口的访问。在应用EMC模块时,需要对信号端口和一系列参数进行设置,设置参数需要以HPI端口的时序为依据[5]。表1是EMC模块的参数设置和端口配置。

FPGA内部的CPU软件指令控制EMC与外部USB器件通信。在该实验中,它的任务包括USB器件初始化,将编译好的CY7C67300的应用程序存入CY7C67300的内部RAM,查询,等待USB键盘输入事件,键盘数据的读入。

2.2 音频接口(LM4550)

在ML402开发板上使用的音频解码芯片是LM4550,它符合AC97协议,能够提供音频系统所有模拟功能,具有4个立体声和3个单声道输入,声音的输入和输出采用PCM分时复用技术,其中每一帧数据都有13个时槽(slot),帧同步信号由一个上升沿标记。slot0为16位,其他的为20位。

在输出(从微控制器输出到LM4550)上,slot0是标记槽,用于说明后面的slot是否有效,slot1用于控制读写LM4550寄存器,slot2为写操作时的控制数据,其他的slot分别用于PCM数据的传递。

在输入(从LM4550到微控制器)上,slot0用于标记,slot1和slot2用于寻读写寄存器的地址和数据,其他的slot分别用于PCM数据的传递。因为电子琴主要是音频输出,表2列出了输出PCM音频流数据帧的定义[6]。

LM4550内部一共有14个寄存器,通过向LM4550的寄存器发送控制命令,可以控制传输方式和质量,还可以监视传输状态。但如果不做特殊的传输,大部分寄存器可以设置为默认状态,但采样速率控制寄存器(sample rate control registers (2Ch, 32h))必须设置,实验中采用48 000 Hz,如果是输出,声源是自动识别的。

表1 EMC模块的参数设置和端口配置

表2 PCM输出时槽分配及定义

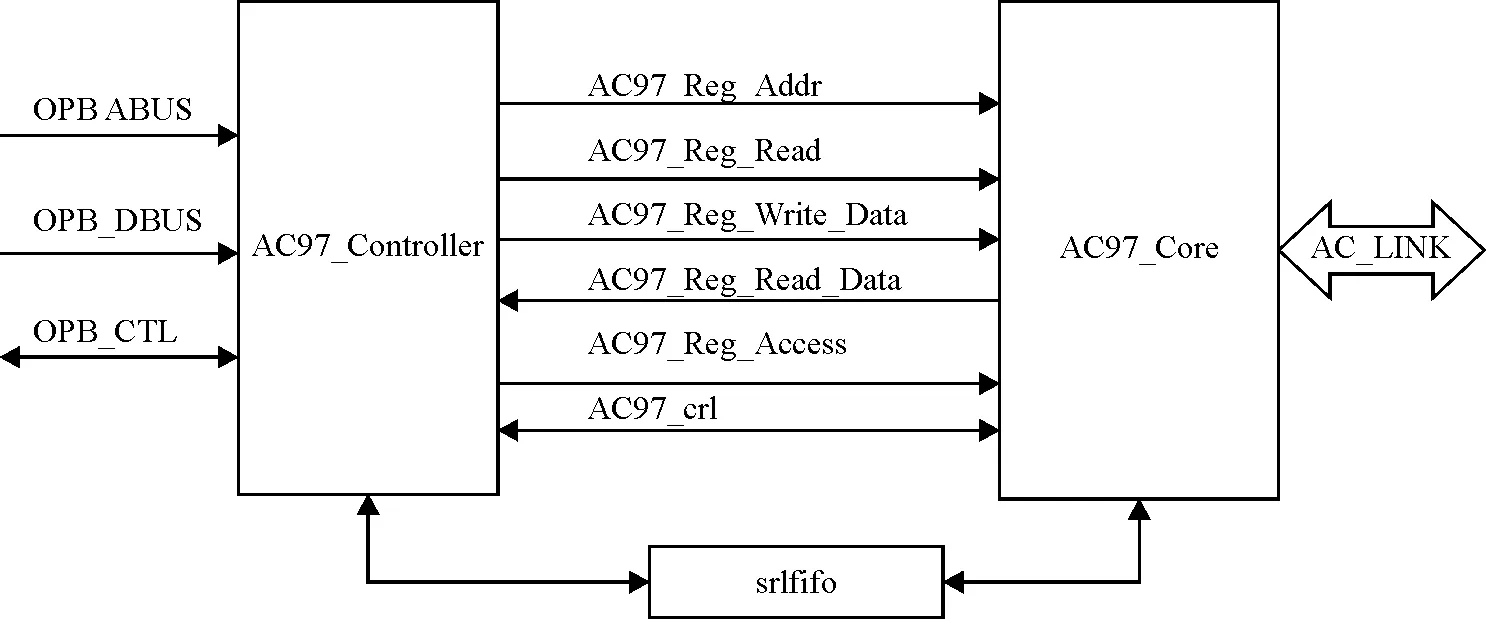

音频接口需要在FPGA片内设计一个AC97 Controller与LM4550接口,AC97 Controller在FPGA内部与OPB总线连接,外部通过AC_LINK接口与芯片LM4550相连。AC_LINK是一种音频串行数据流协议,可以PCM的方式处理多路输入/输出,同时也控制LM4550的寄存器,通过FPGA内部CPU发出指令控制声音的录制、播放等。 LM4550与FPGA的连接非常简单(AC_LINK接口),只需要五个管脚:BIT_CLK、SYNC、SDATA_IN、SDATA_OUT、RESET。BIT_CLK用于给出LM4550的数据时钟信号,SYNC是同步信号,数据则是通过SDATA_IN和SDATA_OUT来传输的,连接图如图2所示[7]。

图2 AC97 Controller与LM4550的接口

AC97 Controller是一个用VHDL设计的IP Core,参考设计来源于Xilinx 开发板ML402提供的例程。AC97 Controller包括三大模块:顶层模块AC97 Controller.vhdl、音频时序处理模块AC97_core.vhdl、声音数据fifo 模块srlfifo.vhdl,如图3所示。

图3 AC97 Controller框图

AC97 Controller.vhdl是顶层文件,调用了其他两个模块和一些程序包,其作用是在总线上捕捉由CPU发出的控制音频播放和录制的命令,并将这些命令进行转化,再传送到音频时序控制模块AC97_core.vhdl。图4是AC97 Controller.vhdl基本状态图。

图4 AC97 Controller.vhdl 基本状态图

AC97_core.vhdl是音频时序处理模块,接受从AC97_controlle.vhdl发来的数据、寄存器地址和控制信号,并将这些信号进行转化后发往LM4550,进行声音播放,或者接受从LM4550来的音频数据,经转化后送到AC97 Controller.vhdl,进行声音录制[8]。图5是AC97_Core.VHDL 的基本状态图。

2.3 存储器接口及基本音符数据的存储

基本音符数据是事先存入Flash的,可以通过录音软件以wave格式将诸如do、re、mi…等基本音符按48 000 Hz的采样频率录制下来,设置为左右双声道(slot3、4有效)。录音时的设置必须要和LM4550的设置一致,然后,将wave文件中的纯声音数据提取出来,并将声音数据按等间隔写入ML402的Flash内。存储器接口是在FPGA内部总线上连接一个EMC作为存储控制器。这里用了第二个EMC,参数设置和USB接口一致,端口配置是根据Flash的外部信号来确定,其中地址信号16位,数据信号32位,4位字节使能信号,还有读、写、片选信号。这样当有USB键盘输入事件后,就从Flash调用不同的声音数据输入到LM4550,LM4550会将声音数据插入PCM音频流的有效数据时槽,从而实现一个基本的演奏系统。

图5 AC97_Core.vhdl基本状态图

2.4 LCD接口

LCD液晶显示屏是一个标准的字符显示屏,具有4位数据信号加上3位控制信号,在FPGA内部采用普通IO控制器GPIO做接口控制模块。GPIO硬件结构由一系列D触发器构成,液晶屏的7个信号都连在GPIO的数据端口,由CPU指令来指挥LCD控制信号和数据信号的变化。

3 软件设计

3.1 CY7C67300片内应用程序的开发

CY7C67300片内应用程序的开发主要是在BIOS的上层Framwork提供的各种子程序框架上完成,应用程序的开发实际上是调用各种Framwork的子程序[9]。本实验中用到的功能比较简单,采用了Xilinx 公司提供的示例程序app.c。主要功能就是发现USB接口有键盘值输入时,将数据取回,再送到端口数据寄存器中,并设置邮箱和状态寄存器,等待外部控制器将数据取走。

3.2 FPGA片内CPU固件开发

FPGA片内软件在EDK提供的软件开发平台上开发,用C语言编写。程序先初始化,并将编译好的用于CY7C67300的应用程序通过EMC和HPI接口传到CY7C67300的RAM中;然后,通过一个无限循环查询HPI端口的键盘输入状态,如有键盘输入,则接收数据,调用音频播放子程序,并在LCD上显示状态。图6是软件设计流程图。

图6 软件设计流程图

4 结束语

该实验通过简易电子琴设计的实例,使学生学习了如何利用新的设计工具构建SOPC系统,并通过设计和增加不同的IP core对不同的接口进行控制。学生经过该实验,能够对计算机系统及结构、计算机接口原理、嵌入式系统应用等有更深刻的认识,是学习了计算机基本理论以后的一次综合性的实验,也是对理论基础学习的一次检验。通过该实验,能够让学生拓宽知识面,了解目前计算机软硬件设计的新技术,并通过对一两个接口的控制,深入细致地学习接口及协议的相关理论,体会到计算机技术的发展趋势[10]。

通过亲身实践,使学生体会到实践与理论的差距,在设计与实现的过程中,让学生提高分析能力、变通能力和动手解决实际问题的能力。学生在进行这个实验的时候,对一些可能增加风险的方案进行否决,对一些前景渺茫的尝试进行终止,并在项目完整度和效果间进行博弈,从而确保实验项目按时完成并实现核心功能。

这个实验让学生更能适应团队合作的过程,并在一定程度上消除面对未知领域的恐惧,能够帮助学生更好地适应并解决问题,从而在今后的工作岗位上发挥更大的作用。

[1] 董代洁,郭怀理,曹春雨.基于FPGA的可编程SoC设计[M].北京:北京航空航天大学出版社,2006.

[2] Xilinx.EDK concepts,tools,and techniques(UG683)[EB/OL].[2012-02-01]. http://www.xilinx.com/support/documentation/sw_manuals/xilinx12_1/edk_ctt.pdf.

[3] Cypress. EZ-host? programmable embedded USB host/peripheral controller(38-08015Rev) [EB/OL].[2012-02-01]. http://www.cypress.com/?docID=30079.

[4] Cypress.BIOS user’s manual[v1.1].[EB/OL].[2014-01-16].http://www.cypress.com/?docID=14346.

[5] 周悦芝,董代洁.微型计算机系统接口技术实验教程—基于FPGA设计[M].北京:清华大学出版社,2011.

[6] National.LM4550 AC ’97 multi-channel audio codec with stereo headphone amplifier, sample rate conversion and national 3D sound(Rev 2.1) [EB/OL].[2014-01-15].http:// www.national.com

[7] 张良臣.数字助听器芯片中单通道语音增强算法的研究与实现[D].哈尔滨:哈尔滨工业大学,2010.

[8] 本刊编辑部.逻辑分析仪在AC’97音频解码中的应用[J].今日电子, 2011(12):1-2.

[9] Cypress.Frameworks reference guide for the CY7C67300/CY7C67200 family of products(V1.0) [EB/OL].[2014-02-03].http://www.analog.com/static/imported-files/data_sheets/ADV7125.pdf.

[10]谢伟.基于FPGA的微机接口实验平台的研究与实现[D].北京:北京工业大学,2011.

USB Electronic Organ Design Experimental Based on SOPC

TIAN Shuzhen, QUAN Chengbin, DONG Daijie

(Department of Computer Science and Technology,Tsinghua University,Beijing 100084,China)

This paper introduces the design and realization of simple electronic organ based on SOPC and USB keyboard. Using the ML402 multi function interface board as the platform, a simple system on a programmable chip is achieved in the FPGA chip on the ML402. This system includes a CPU, data and instruction memories, and internal buses. On this basis, the USB interface and audio interface controller are added to the system. A USB keyboard is connected to a USB port as the keys of electronic organ, and the ML402 interface board is used as the USB host device. Through writing the CPU instruction codes in FPGA chip on the ML402, the USB keyboard value is read and keyboard notes are played.

SOPC; USB interfaces; audio interface; USB keyboard

2014-03-26

田淑珍(1966-),女,学士,工程师,主要从事计算机硬件实验教学工作。

TP368.2;G

Adoi:10.3969/j.issn.1672-4550.2015.01.014