组合逻辑实验电路设计方法研究

2015-05-08韩守梅木春梅

阎 群,韩守梅,木春梅,李 擎

(北京科技大学 a.自动化学院;b.钢铁流程先进控制教育部重点实验室,北京 100083)

组合逻辑实验电路设计方法研究

阎 群a,b,韩守梅a,木春梅a,李 擎a

(北京科技大学 a.自动化学院;b.钢铁流程先进控制教育部重点实验室,北京 100083)

讨论了三人表决逻辑电路,分别采用小规模集成门电路、中规模集成电路、只读存储器和可编程逻辑阵列实现了六种三人表决逻辑实验电路,总结了设计组合逻辑电路的步骤和方法。该方法对其他数字逻辑电路的设计具有一定的指导作用。

组合逻辑;逻辑表达式;逻辑电路;三人表决电路

电子技术实验是理工科相关专业本科生的必修课程,一般包括模拟和数字两部分[1-2]。数字逻辑电路的分析和设计是数字电子技术的重要内容,是学习后续课程的基础,在教学、科研、产品开发等方面占有重要的地位[1-3]。数字电路元器件品种繁多、性能各异,电路设计方法多种多样,如何根据具体条件选择适当的设计方法,设计出合理的电路是每个设计人员必须考虑的。电子技术实验的目的是通过实验巩固、加深对基本理论的理解,培养学生理论联系实际的能力,提高学生动手能力、设计能力、分析问题与解决问题的能力、创新实践的能力[4]。

因此,在数字电子实验教学中,鼓励学生多用几种方法进行电路实验将具有重要的意义。本文通过三人表决电路,详细介绍了组合逻辑电路分析和设计的方法,这些方法对其他数字逻辑电路的分析和设计具有一定的指导作用。

1 三人表决电路及其逻辑表达式

三人表决电路遵循少数服从多数的原则,是一种代表投票表决的装置[4]。用3个开关作为表决电路的3个输入变量,输入逻辑“1”时,表示表决者“赞同”;输入逻辑“0”时,表示表决者“不赞同”。 输出变量为表决的通过或不通过,输出逻辑“1”时,表示表决“通过”;输出逻辑“0”时,表示表决“不通过”。当表决电路的3个输入变量中有2个以上(含2个)为“1”时,则表决电路输出为“1”,否则为“0”。 三人表决电路的真值表如表1所示。

表1 三人表决逻辑电路真值表

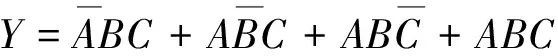

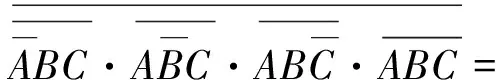

由真值表可写出三人表决电路的输出标准逻辑表达式:

(1)

2 小规模集成门电路实现三人表决

使用小规模集成门电路实现时,首先,对标准逻辑表达式进行化简,得到最简逻辑表达式,即逻辑表达式中相加的乘积项最少、每个乘积项的因子最少;然后,将最简逻辑表达式变换为与给定门电路相对应的形式[5-7]。用逻辑代数或卡诺图化简得到三人表决最简逻辑表达式为:

Y=AB+AC+BC

(2)

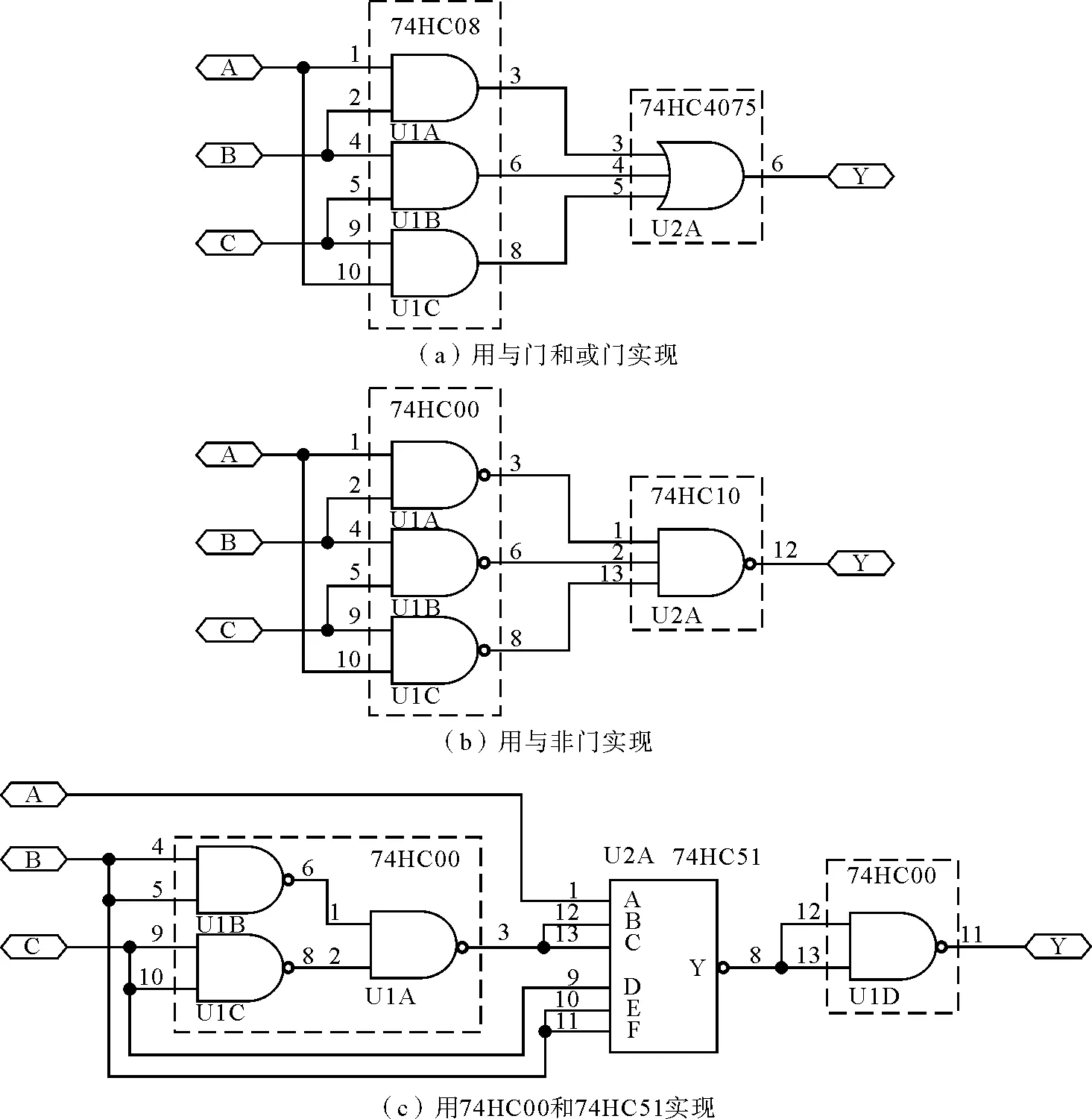

用3个双输入与门(1片74HC08)和一个三输入或门(1片74HC4075)[8]可实现三人表决,如图1(a)所示。

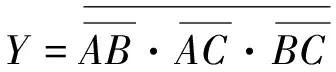

如果要求采用与非门实现,利用反演定理将式(2)变换为:

(3)

用3个双输入与非门(1片74HC00)和1个三输入与非门(1片74HC10)[8]可实现,如图1(b)所示。

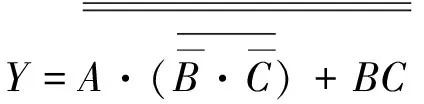

如果要求用1片双输入与非门74HC00和1片三输入与或非门74HC51[8]实现,则将式(2)变换为下式,电路图如图1(c)所示。

(4)

图1 小规模集成门电路实现三人表决

三种实现方法中, 前两种门电路的个数都是4个,成本差不多,第三种用了8个门电路,成本要高一些。

3 中规模集成电路实现三人表决

3.1 用译码器实现

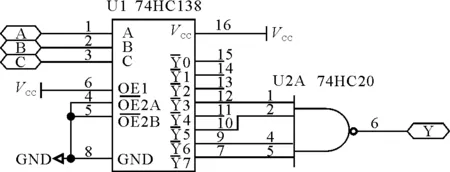

译码器是一类多输入、多输出组合逻辑器件,n变量二进制译码器具有2n个输出变量,恰为n变量的最小项。任何组合逻辑电路都可用最小项之和的标准形式表示,因此,可用n变量二进制译码器和必要的门电路实现n输入变量逻辑电路。3~8线译码器74HC138输出低电平有效[8],用译码器74HC138 和“与非”门可以实现三人表决电路。74HC138 译码器输出的逻辑表达式为:

(5)

确定译码器的地址变量,令A=A,B=B,C=C,则变换式(1)可得:

(6)

用译码器74HC138实现三人表决电路如图2所示。

图2 用74HC138 译码器实现三人表决电路

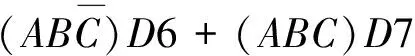

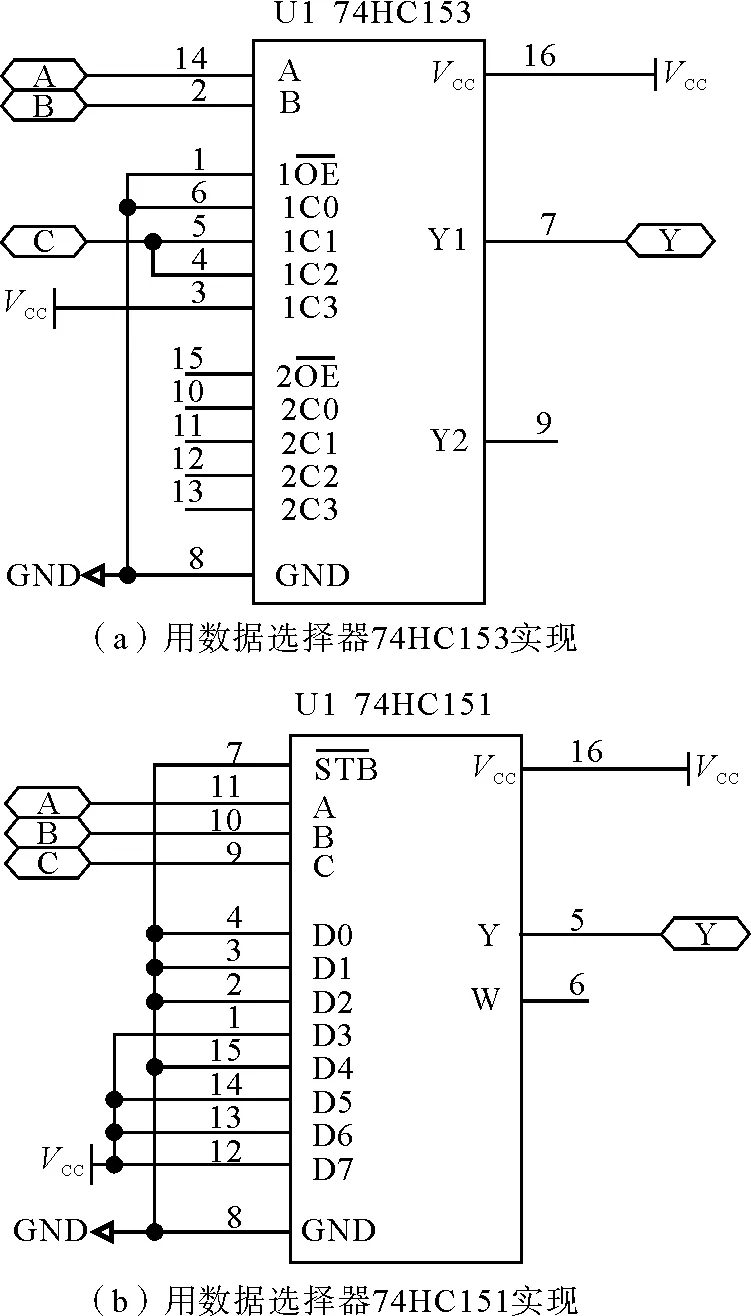

3.2 用数据选择器实现

数据选择器的输出端具有标准“与或”的形式。n选1数据选择器在选择输入控制下,从n个数据中选择某个数据送到输出端。采用n选1数据选择器可以实现任何输入变量数不大于n+1的组合逻辑电路。三人表决电路可选用4选1或者8选1数据选择器实现。

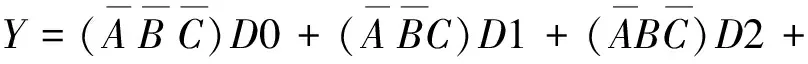

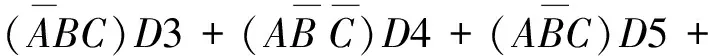

74HC153是一个双4选1数据选择器[8],其输出逻辑表达式为:

(7)

74HC153实现三人表决电路时,令A=A,B=B,变换式(1)为式(7)的形式,求得输入数据C0=0,C1=C2=C,C3=1,逻辑电路如图3(a) 所示。

74HC151是一个8选1数据选择器[8],其输出逻辑表达式为:

(8)

选用74HC151实现三人表决逻辑功能时,令A=A,B=B,C=C,根据标准逻辑表达式(1)可求得输入数据D0=D1=D2=D4=0,D3=D5=D6=D7=1,逻辑电路如图3(b)所示 。

图3 用数据选择器实现三人表决电路

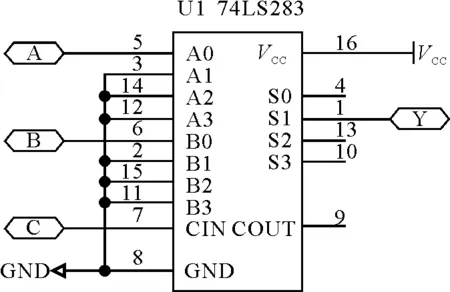

3.3 用加法器实现

加法器是产生数和的装置,分为半加器和全加器。若加数、被加数与低位的进位为输入,和数与进位为输出则为全加器。74LS283是超前进位四位二进制全加器[8],即所有各位的进位直接从最低位进位CIN产生。定义变量:

(9)

那么,74LS283的输出逻辑表达式为:

(10)

显然,令A0=A,B0=B,CIN=C,则S1即为三人表决输出Y。逻辑电路如图4所示。

图4 用加法器74LS283实现三人表决电路

4 ROM和PLA实现三人表决

只读存储器ROM和可编程逻辑阵列PLA都属于组合逻辑电路,都有一个与阵列和一个或阵列,但PLA的与阵列和或阵列都是可编程的,而ROM中与阵列是固定连接,只有或阵列可编程。

ROM 中的与阵列是一个产生2n个输出的译码器,即产生2n个最小项(与阵列的输出mi)。用ROM实现组合逻辑电路时,首先,将逻辑表达式表示成最小项之和的形式;然后,把逻辑表达式的输入作为ROM的输入;最后,根据要实现的逻辑表达式对ROM的或阵列进行编程,画出相应的阵列图。用ROM实现三人表决的阵列图如图5(a)所示。

图5 用ROM和PLA实现三人表决电路

用PLA实现组合逻辑电路的方法与用ROM实现非常相似。两者的区别在于,用ROM实现是基于最小项表达式,而用PLA实现是基于最简与或表达式,所以用PLA实现组合逻辑比用ROM实现更简单、灵活、经济。首先,将逻辑表达式化简为最简与或表达式;然后,根据最简表达式中的不同与项以及各与项之和分别对PLA的与阵列和或阵列进行编程,画出阵列图。用PLA实现三人表决如图5(b)所示。

5 结束语

组合逻辑电路设计中,首先,根据给出的实际问题建立输入、输出变量,列出所有可能的输入、输出状态,即真值表;然后,根据真值表写出输入、输出的标准逻辑表达式,用逻辑代数或卡诺图根据设计要求化简、变换逻辑表达式;最后,根据化简、变换的逻辑表达式采用标准器件实现逻辑电路,力求所用器件数、器件的种类、器件之间的连线均最少。

组合逻辑电路的输入、输出变量较少时,常常采用中小规模集成门电路实现,设计灵活,电路成本低,设计时应以减少集成电路的数量为目标,充分利用集成电路中的门,减少电路中信号通过门的级数而减少信号延时,提高工作速度。组合逻辑电路较复杂时,常采用中规模集成电路设计,成本低、体积小、功耗低、速度快、可靠性强,但受中规模集成电路功能限制,灵活性不如门电路。当最小项数目较大时,采用只读存储器ROM或可编程逻辑阵列PLA实现比较合适。

[1]阎石.数字电子技术基础[M].5版.北京:高等教育出版社,2006.

[2]邓元庆,关宇,贾鹏.数字设计基础与应用[M].北京:清华大学出版社,2010.

[3]康华光,邹寿彬,秦臻.电子技术基础(数字部分)[M].5版.北京:高等教育出版社,2006.

[4]韩守梅,刘蕴络.电工电子技术实验教程[M].北京:兵器工业出版社,2006.

[5]陈立万.数字逻辑电路设计方法探讨[J].四川师范大学学报:自然科学版,2000,23(6):656-658.

[6]林涛.一位全加器电路实现方法探讨[J].电气电子教学学报,2010,32(B10):223-226.

[7]崔祥霞,陈君.一位全加器实验电路设计方法的研究[J].物理实验,2009,23(9):39-41.

[8]刘畅生.通用数字集成电路简明速查手册[M].北京:人民邮电出版社,2011.

Study on Designing Methods of the Combinational Logic Experimental Circuit

YAN Quna,b, HAN Shoumeia, MU Chunmeia, LI Qinga

(a. School of Automation and Electrical Engineering; b. Key Laboratory of Advanced Control of Iron and Steel Process (Ministry of Education), University of Science and Technology Beijing, Beijing 100083, China)

The details of three people voting circuit are discussed. Six different experiment circuits for three people voting experimental circuit are designed, based on small scale integrated gate circuit, middle scale integrated gate circuit and read-only memory, programmable logic array, respectively. Steps and methods of designing combinational logic circuit are summarized, which can be used for reference when design other digital logic circuit.

combinational logic; logic expression; logic circuit; three people voting circuit

2013-12-25;修改日期: 2014-02-12

阎 群(1970-),女,博士研究生,讲师,主要从事电动汽车与新能源控制系统,智能控制等科研与教学工作。

TN710.5

A

10.3969/j.issn.1672-4550.2015.01.007