数字梯形成形滤波器的模块化设计

2015-05-08王毅男

王毅男 林 伟

(上海应用技术学院电气与电子工程学院,上海 201418)

数字梯形成形滤波器的模块化设计

王毅男 林 伟

(上海应用技术学院电气与电子工程学院,上海 201418)

针对数字梯形成形滤波器在数字化多道脉冲分析仪中的应用,给出其z变换方法的推导过程,并通过傅里叶变换讨论其滤波功能。从实际应用出发,对梯形成形滤波器进行模块化设计,使设计更有利于可编程逻辑器件的实现,可以简单灵活地调节梯形形状以适应不同的工作环境。利用Matlab软件对设计进行原理仿真,验证了模块化设计的正确性,并通过加入高斯白噪声的方法讨论其滤波特性。使用FPGA配合嵌入式逻辑分析仪给出梯形成形滤波器的硬件实现及仿真,验证了系统设计的正确性。

梯形成形 数字化滤波 多道脉冲幅度分析仪 延迟可调 FPGA

0 引言

20世纪90年代,基于数字信号处理技术,提出了新的核脉冲能谱分析技术。数字电路技术的最大优点是灵活性,它可以综合成各种滤波器,使系统达到更高的信噪比,获得更好的能量分辨率,这些优点也是模拟电路难以实现的,甚至不可能实现的[1-2]。

多道脉冲幅度分析器是通过测量核辐射探测器输出的电脉冲信号来获取核辐射信息,该信号具有较快的上升沿,有丰富的高频成分。由于前端电路的噪声影响和数模转换器采样频率的限制,不可能采集到每个脉冲信号的最大幅值[3-4],因此在高精度要求下,“直接数据采集法”是不可行的,而梯形成形算法可以弥补这个不足。梯形成形滤波器是将输入的下降沿衰减的指数信号成形为梯形脉冲信号输出。已有研究证明,当只考虑电压和电流噪声,探测器收集电荷的时间不为零时,梯形成形滤波器是最优滤波器,并且非常适合用数字方法实现[5]。

为提高梯形成形算法的实用性,本文对算法进行模块化设计,从更适合可编程逻辑器件实现的角度出发,完成梯形成形滤波器的结构设计。

1 梯形成形算法

设前置放大器输出为理想指数信号,时域表达式为:

Ui(t)=Umaxe-t/τμ(t)

(1)

式中:Umax为脉冲幅值;τ为前端放大器的时间常数;μ(t)为标准单位阶跃函数。

以TS为周期对输入信号进行采样,可以得到脉冲序列的表达式为:

Ui(t)=Umaxe-nTs/τμ(t)

(2)

令e-nTs/τ=q,并对式(2)进行z变换得:

Ui(t)=Umax×z/(z-q)

(3)

理想梯形函数的分段函数表示如下:

(4)

式中:ta、tb、tc分别为梯形的上升沿、平顶、下降沿的宽度。令ta=naTs、tb=nbTs、tc=ncTs,理想梯形函数的分段函数经过单边的z变换可表示为:

(5)

从而可得梯形成形算法的系统函数:

(6)

梯形成形算法是以其时域特性为出发点进行设计的,但是,任何成形处理都相当于在频域中进行了某些滤波操作。所以,有必要研究该算法的频域特性。

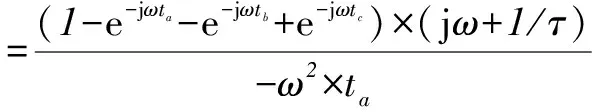

对式(1)~式(4)做傅里叶变换,得到系统函数:

(7)

对式(7)求模可得:

将上式分成两部分分析。

2 梯形成形算法的模块化设计

模块化设计可以降低系统设计的复杂度,而采用一种结构形式来实现整个滤波器需要很多运算资源,寻找最优化结构也非常困难,所以通常采用子模块级联或并联的方法来实现复杂的滤波器设计。

将系统函数分解为4个子模块,则有:

H(z)=H1(z)×H2(z)×H3(z)×H4(z)

4个子模块的级联存在顺序问题,要避免具有峰值增益的子系统发生溢出或将量化噪声扩大。在该设计中,H1模块会产生溢出,但是可以证明该溢出不会对运算结果产生影响,所以把H1置于第一级;H4为积分单元,为了避免产生溢出,将其置于最后一级;H2、H3置于中间,因其结构相同,所以位置可以互换。

2.1 H1子模块的结构设计

结构设计就是用加法器、乘法器和延迟单元等运算模块的互联结构来描述线性常系数方程,不同的结构设计消耗的系统资源以及在性能上都是有很大的差异。H1子模块的结构设计如图1所示,可以由IIR滤波器实现。IIR滤波器在结构上有很多种形式,有直接I型及其转置形式、直接II型及其转置形式。H1子模块有一个零点和一个极点,输入的核脉冲信号是指数衰减信号。假如先实现极点,就相当于对信号进行积分操作,这必定会产生溢出,是输出错误,所以必须先实现零点。可以选择直接I型或者直接II型的转置形式,因为后者消耗的延迟单元更少,所以设计选择直接II型的转置形式来实现H1子模块。

图1 H1模块结构图

2.2 H2、H3子模块的结构设计

H2、H3子模块的结构设计如图2所示。

图2 H2、H3模块结构图

设计该模块的主要任务是完成延迟数较大的延迟单元z-na、z-nb的设计。FPGA实现延迟单元有如下3种方法。

① 利用Matlab中的DSP Builder直接生成延迟单元模块,再使用Quartus II调用生成文件。

② 利用Quartus II自带的参数模型库(library of parameter model,LPM)的Shift register,也可以实现一个精准的延时。这里面有两个参数选项,一个是taps(即分成几段数据),另一个是distance(每段数据里面有几个数据),调节二者的设定值就可以改变延迟数目,taps的高位代表的就是延迟输出的数据。

比较这两种方法,使用移位寄存器消耗的资源更少,而且不需要通过第三方工具。LPM中的器件都是经过优化得到的结果,这使工程设计资源最优化以及warning更少。当需要实现任意时钟的延时时,移位寄存器不一定能够满足,这时就要用DSP Builder来实现了。

③ 以双口RAM为核心设计一个延迟模块,延迟的实现是通过改变读写地址而并非在寄存器中流动,通过控制写入地址、读出地址控制写入、读出数据,通过异步复位对模块赋初值,写入地址与读出地址之差就是延时数目,每次异步复位之后,如果输出地址所指向的存储单元不能确定就输出0。所以只需要改变延迟数的初值就可以设定模块多延迟数目。该方法增加了外围电路的设计,但是可以大幅度减小设计面积,降低芯片功耗。为了适应不同的工作环境,延迟数ta和tb的数值是灵活可调的。因此,选择双口RAM法完成模块的设计。

2.3 H4子模块的结构设计

H4模块包含一个积分单元、一个延迟单元和一个比例因子,结构比较简单,也可以采用直接Ⅱ型的转置形式,将积分器与延迟单元设计在一个结构中,以减少延迟单元的使用。如果系统的运算速度过高,官方提供的除法器将不能直接使用。此时,可以调节使比例因子的值为2-n,通过数据移位的方法来实现除法,这样就免去了乘法器或除法器的使用,而且对滤波器的性能没有影响。H4子模块的结构设计图如图3所示。

图3 H4模块结构图

3 软件仿真与硬件应用实现

3.1 原理仿真

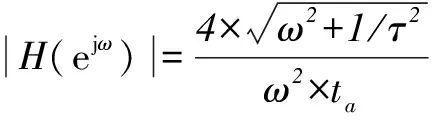

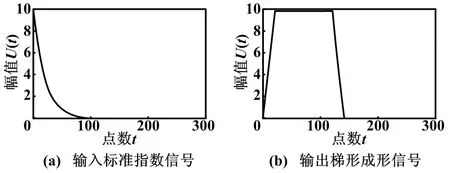

采用Matlab软件编程实现算法,以验证其可行性。仿真原理图如图4所示。输入标准指数信号Ui(t)=Umaxe-t/τμ(t),取Umax=10,TS=0.05,τ=1,输入标准指数函数如图4(a)所示。令梯形成形函数的上升沿(下降沿)宽度为20,平顶时间为100,运算后输出波形如图4(b)所示。

根据仿真结果图知,输入的标准指数信号经梯形滤波成形输出的梯形成形信号效果比较理想,得到的输出结果是一个非常标准的等腰梯形,上升沿宽度为20、平顶宽度为100、下降沿宽度为20,与输入指数信号的幅度相同。

图4 原理仿真图

当输入信号幅度为10,加入标准差为0.1的高斯白噪声,即输入端信噪比为100时,得到梯形滤波成形仿真结果如图5所示。

图5 滤波特性仿真图

仿真发现,输出信号的平均值随输入噪声标准差的增大变化并不大。文献[7]、[8]给出了梯形成形算法对包噪声的抑制作用,证明经梯形滤波成形算法后,噪声的平均值和标准差均得到减小,从而可使基线得到恢复。

3.2 算法的FPGA实现

数字化多道脉冲幅度分析器需要高速模数转化器对核脉冲信号进行采样,从而需要实时处理大量的数据。可编程逻辑器件的电路可结构化,使其非常适用于数字信号处理及复杂电路的时序控制。因此,FPGA、CPLD被广泛应用于数字化多道脉冲幅度分析器中,完成高速数据接口及大数据量的信号处理的工作。

本文采用Altera的 Cyclone III 器件实现模块化梯形成形滤波器设计。梯形成形滤波器的输出结果功能测试通过使用Quartus II自带的Signal Tap II(嵌入式逻辑分析仪)对滤波器进行观测。Signal Tap II的输出结果表明,梯形成形滤波器可以稳定地将输入的指数信号转换为梯形脉冲信号。FPGA进行数字信号处理需要将参数量化,而e-nTs/τ的数值很难精确量化。有研究表明该数值的量化精确度会直接影响梯形成形的精确度,本仿真也验证了这一结论(梯形的平顶会产生畸变)[9-10]。将时序仿真结果与Matlab仿真结果相比较,FPGA设计的梯形成形滤波器输出精度比较理想。

4 结束语

本文利用z变换法将数字多道脉冲幅度分析器中所需要的梯形成形滤波器进行模块化设计,降低了算法硬件实现的复杂度,以及对硬件资源的消耗,以更好的“速度”与“面积”特性完成数字信号处理。使用双口RAM实现了参数可调的延迟模块的设计,以适用于不同的环境。使用软件对模块化设计的原理进行了仿真,同时完成了算法的FPGA的实现,仿真结果显示梯形成形滤波器性能已达到。

[1] Sampsonte V R.Comparisons between digital gamma-ray spectrometer (DSPec) and standard nuclear instrument methods(NIM) systems[R].LA-13393-MS,March 1998.

[2] Imperiale C,Imperiale A.On nuclear spectrometry pulses digital shaping and processing[J].Measurement,2001,30(1):49-73.

[3] 肖无云,魏义祥,艾宪芸.数字化多道脉冲幅度分析中的梯形成形算法[J].清华大学学报:自然科学版,2005,45(6):810-812.

[4] Jordanov V T.Real time digital pulse shaper with variable weighting function[J].Nuclear Instrument and Methods in Physics Research Section A,2003,505(1-2):347-351.

[5] 王季红,王良厚,房宗良.梯形成形技术在数字多道系统中的应用[J].核电子学与探测技术,2011,31(5):543-546.

[6] 陈亮.核素识别算法及数字化能谱采集系统研究[D].北京:清华大学,2009.

[7] 周清华,张软玉,李泰华.基于Matlab的数字化梯形滤波器的研究[J].核电子学与探测技术,2008,28(1):85-88.

[8] 胡创业,康玺,屈国普,等.梯形成形冲击响应函数推导、仿真和实验研究[J].原子能科学技术,2014,48(2):341-346.

[9] 张软玉,陈世国,罗小兵,等.数字化核能谱获取中信号处理方法的研究[J].原子能科学技术,2004,38(3):252-255.

[10]周清华,张软玉.数字化核信号梯形成形滤波算法的研究[J].四川大学学报:自然科学版,2007,44(1):111-114.

Modular Design of Digital Trapezoidal Shaping Filter

In accordance with the application of digital trapezoidal shaping filter in multi-channel pulse analyzer, the derivation process of itsztransform method is given, and its filtering function is discussed through Fourier transform. From the practical application, the modular design of trapezoidal shaping filter is conducted, thus the design is more conductive to the realization of the programmable logic devices, and to adapt different working environment, the shape of trapezoid can be adjusted flexibly. The principle simulation of the design is conducted by adopting Matlab software, the correctness of the modular design is verified, and the filtering characteristics are discussed through adding Gaussian white noise. The hardware implementation and simulation of such filter are given using FPGA and embedded logic analyzer, the correctness of the system design is verified.

Trapezoidal shaped Digital filtering Multi-channel pulse amplitude analyzer Adjustable delay FPGA

王毅男(1989-),男,现为上海应用技术学院仿生装备与控制工程专业在读硕士研究生;主要从事高速信号采集与处理的研究。

TH83;TN713

A

10.16086/j.cnki.issn1000-0380.201510022

修改稿收到日期:2015-02-02。