基于USB 2.0/MAC协议变换的延长系统设计

2015-05-04金君潇虞致国顾晓峰

曹 杨,金君潇,虞致国,顾晓峰

(江南大学 电子工程系 轻工过程先进控制教育部重点实验室,江苏 无锡214122)

0 引 言

通用串行总线 (USB)接口作为计算机及许多外设的必备接口,它的最大传输距离一般仅5m,通过加入信号放大器可延长至50m,但很多情况下信号并不稳定,而且常常不能满足实际需求[1]。随着网络技术的不断发展,网络通信协议具有良好的稳定性和较短的传输延时,可以通过不同类型的电缆线将传输距离进一步延长,从而拓展USB延长系统在远距离通信领域的应用[2,3]。

本文提出一种修改和自定义的以太网媒体访问控制(MAC)协议,并采用该协议与USB 2.0协议之间的协议转换技术,基于现场可编程门阵列 (FPGA)平台设计了一种延长系统,不仅可实现USB 2.0接口与网络接口的相互转换,而且可利用网络通信技术将USB 2.0接口的传输距离延长至100m以上,在大规模高速数据传输、远程控制等领域具有重要的应用价值。

1 协议转换原理

1.1 系统总体结构

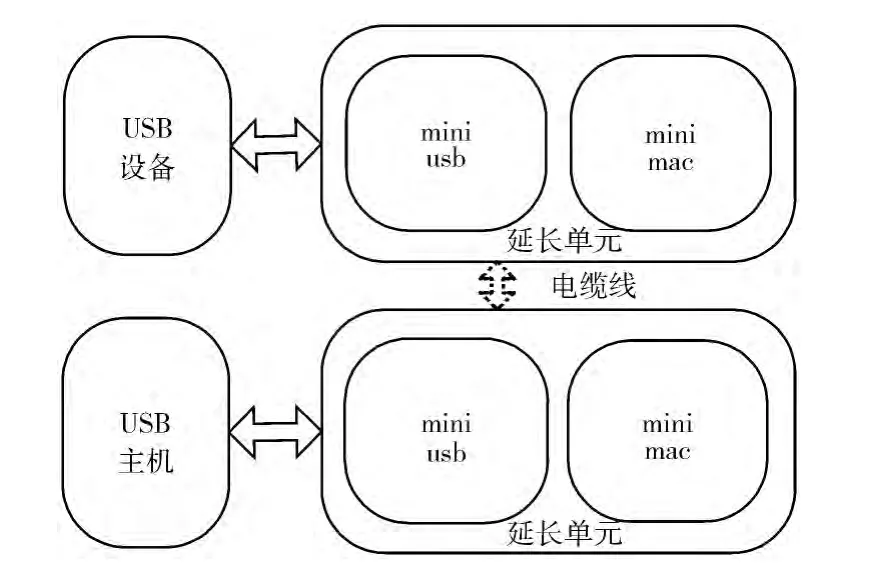

设计的延长系统具有设备与网络间的双向通信功能,即数据发送至网络和从网络接收数据[4]。系统结构如图1所示,主要包含两个完全相同的延长单元,彼此之间可根据需求选用不同类型的电缆线连接。延长单元包括miniusb和minimac两个主要模块,实现USB 2.0和以太网接口间的转换。miniusb模块功能较简单,仅负责数据传递,不对数据作任何处理。minimac模块负责把数据按协议规定的格式封装或解封,再进行传输。

图1 USB 2.0延长系统的结构

1.2 修改和自定义的以太网MAC协议

本文选用兼容性强、可靠性高且易于管理的千兆以太网协议标准IEEE 802.3,该协议采用基于共享介质信道的载波监听多路访问/冲突检测 (carrier sense multiple access/collision detection,CSMA/CD)媒体访问机制,其传输速率最高达1000Mbps[5,6]。MAC子层是体现以太网网络性能的核心,分为媒体访问控制和帧的封装/解封两个部分。文中将minimac设计为全双工通信,允许数据的发送和接收同时进行且不共享信道,因此,修改后的以太网MAC协议将忽略CSMA/CD机制,仅负责数据帧的封装/解封。全双工通信中的数据、命令和状态的接收或发送可同时进行,因此需要一个选择器mac_sel来选择传递数据还是命令。

另外由于千兆以太网与USB 2.0的传输速率 (最高达480Mbps)不相符,如果仅以一次完整的事务来传输,势必造成较长的等待时间引起总线浪费。因此,为提高总线利用率,自定义了一种支持 “分离传输”的以太网MAC协议,就是在一个数据包分成多个子数据包在介质中传输时,能够识别每个子数据包并将这些子数据包全部以以太网帧格式进行封装/解封后再传输至网络中。

1.3 速率解耦

由于USB与以太网之间传输速率的差异,需要设置一个数据缓存区进行速率解耦。另外,在miniusb、minimac的控制机制中,需要首先判断数据是否需发送或接收,而此过程也需要一个暂时存储数据的地方。文中采用双fifo(first input first output)作为缓冲区存储数据[7]。由于读写速率不同,将fifo设置成双口的RAM。

对于高速USB,其数据包中有3字节的前导码,而以太网帧数据则有7字节的前导码和1字节的命令识别码。要保证fifo两端的传输速率一致,则至少需要有6个字节的数据存在fifo中。

minimac的发送条件设置为当fifo中有大于1个字节数据或声明已存一个完整的数据包,即:

miniusb的发送条件设置为只要fifo不为空则开始发送数据,即:

对于低速/全速USB,其最大容忍的延时为18ns,如果采用与高速USB相同的速率解耦方式,则至少延时32 ns,留给传输介质的延时就为负值。因此,这里我们采用异步传递方式,设置低速/全速USB数据的采样频率分别为12M/96M,这样基本能够实现数据的实时传输。发送的触发条件设置为USB的差分输入Dm和Dp不为J状态,即:assign start_rx_rl=~j state。

2 主要功能模块设计

2.1 fifo缓存区

以由主机到设备的下行通信为例,延长单元的写速率为480Mbps,读速率为1000Mbps;由设备到主机的上行通信正好相反。因此,上下行通信过程中都必须有独立的数据缓存区。为了提高数据吞吐率,保证miniusb和minimac模块在发送缓冲区数据的同时可接收来自主机或设备端的数据,为miniusb和minimac模块分别设置了两个缓冲区(即双fifo)。通过自定义发送和接收的触发条件,可达到两者同步传输的目的,并将其写或读数据的状态全部反映到相应的寄存器中[8]。

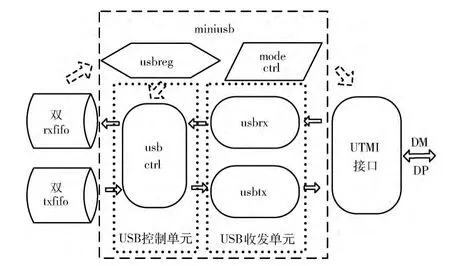

2.2 miniusb模块

miniusb模块的结构如图2所示,其基本工作流程可分为两个部分:从 UTMI (USB 2.0Transcceiver Macrocell Interface)接口接收USB信息包,并完整地存入rxfifo中;usbctrl根据minireg和fifo中的空、满状况,选择写rxfifo中某个fifo的数据,再发送至UTMI接口[9,10]。

usbctrl是miniusb模块设计的核心,其作用是接收数据至rxfifo中和发送txfifo中的数据。USB协议规定同一时刻只能传输一个信息包,因此接收及发送数据的过程存在优先级且不可间断,接收数据过程的实时性使其优先级大于发送数据过程[11]。此外,对于双fifo结构,fifo0的优先级大于fifo1,即当fifo0在使用时,系统自动选择使用fifo1。

图2 miniusb模块的结构

modectrl主要用于对主机和设备的UTMI接口进行控制及信息获取。在主机端,modectrl负责监控设备的复位信号se0和处理主机端的上下拉电阻。当se0状态保持超过1μs,则认为设备需接入主机并将其复位;根据对设备端的判断及接收到的命令,设置上下拉电阻,判断设备需发送何种速度的标准请求。在设备端,根据主机发送的命令,将设备复位、连接并识别其速度模式。当设备连接状态保持超过2μs,认为设备连接成功;否则发送信号se0,当se0状态保持超过2ms,认为设备掉线。

usbtx和usbrx是一种胶合逻辑 (glue logic),前者负责传递txfifo中的数据包到UTMI接口并计数,后者仅负责将UTMI接口的数据包传递至rxfifo中,不对数据作任何处理。

2.3 minimac模块

minimac模块的结构如图3所示。

图3 minimac模块的结构

mactx是数据发送逻辑,用于将USB接口的数据按规定的格式封装并发送至物理层 (PHY),或把PHY层发来的数据解封再转送至上层协议处理。为避免低速和全速模式下的发送过程出现underrun的情况,在未检测到miniusb端发来的数据时,首先发送填充包,直至检测到数据。填充包字段为 (dd,55,f0,f,55,dd)。txctrl用于控制mactx逻辑,具体控制机制为:检测两个fifo中的数据,若fifo中数据深度大于n(n为自行设置,本文定义n=8)时,开始发送数据。

macrx是数据接收逻辑,用于将PHY层传来的信息解封再继续传输。与mactx的工作过程相反,它需要把数据包中的前导包和填充包删除。rxctrl的主要功能是把从macrx接收的有效数据放入fifo,以及在接收完成后设置相应的寄存器。

comm_send和comm_rcv用于发送两边的USB状态。首先,主机端和设备端互发握手包,随即相应的控制寄存器都设置为1,表示握手成功;若握手失败,将每隔16’hffff个时间位重发一次握手包,直至成功。其次,对于普通命令,如果一方发起普通命令,另一方必须回应;若没有回应,则每隔4×210个时间位重发一次。comm_send中发送命令的状态机比较简单,首先发起发送,然后按命令顺序逐个发送。comm_rcv的主要作用是解析由macrx接收到的命令并输出。

3 仿真结果

采用Candence Ncverilog在LINUX环境下对设计的延长系统进行仿真,利用Verilog HDL进行硬件模块编程,根据芯片的控制时序及每个模块的具体功能编写程序。

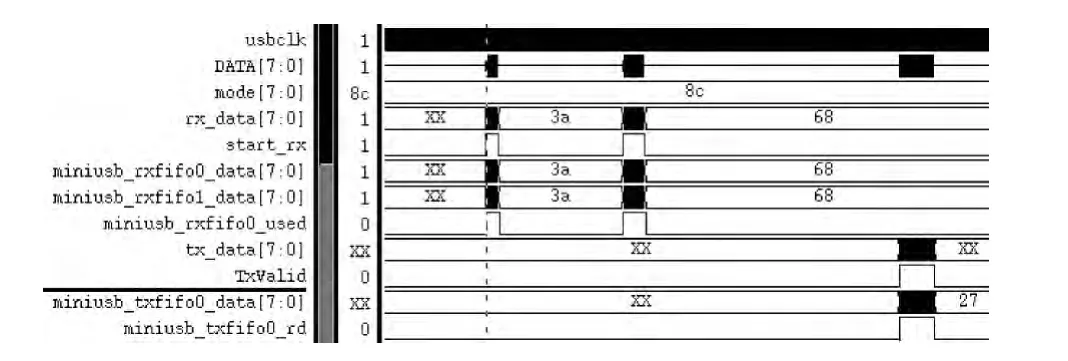

3.1 miniusb模块仿真

图4给出了miniusb模块发送和接收过程的仿真波形。由主机发送数据DATA [7:0],此时模式状态机 mode[7:0]的值为8c,表示当前状态为下行通信模式,并且连接有高速USB设备。当start_rx跳变为高电平,开始接收数据,miniusb_rxfifo0_used有效时,将接收到的数据发送至fifo0缓存中;当TxValid跳变为高电平,开始发送数据,类似地,该过程选择发送fifo0中的数据。仿真结果表明,miniusb模块仅负责传输数据而不对数据作任何处理。

图4 miniusb模块发送和接收过程的仿真波形

3.2 minimac模块仿真

图5给出了minimac模块的仿真波形。在图5(a)所示的发送过程中,tx_comm_sel为高电平,标志一个命令字段的发送过程,tx_start置为高电平,tx_valid、fillbytecnt_start被拉高,开始发送前导包 (7个连续的55)并计数;之后,fillbytecnt_start被拉低,填充结束,根据信号tx_start的变化情况,命令字段 (11,22,33,55)被发送至fifo_data[7:0]中;发送完毕后tx_done拉高,信号fifo_done声明,继续发送填充字段 (dd,55,f0,f,55,dd)并计数,直至tx_valid被拉至低电平,表示整个发送过程完成,该过程中的各个状态可由信号tx_state[4:0]体现。如图5(b)所示,数据接收过程以信号startframe跳变开始,由commandsel声明该过程为命令接收过程,数据phy_data[7:0]经minimac模块处理,去除前导字段和填充字段,最终将命令发送至rx_data中。rx_done跳变表明整个接收过程完成。类似地,该过程中的各个状态可由信号state[6:0]体现。

图5 minimac模块发送和接收过程的仿真波形

4 FPGA验证

最后,基于FPGA平台对USB2.0延长系统进行验证。其中用于连接延长单元的电缆线作为传输介质只负责数据传输,验证时由FPGA内部的数据线实现[12]。

根据设计需求,选用Corecommander II嵌入式开发平台,其FPGA芯片为Altera公司的Cyclone III FPGA系列的EP3C25F256C8芯片,低成本、低功耗、并自带USB 2.0物理层接口 (USB 2.0PHY),符合本设计的需求。基于Altera公司的Quartus II 11.0软件平台,完成功能仿真后的系统综合、布局布线和时序验证。

验证中将开发板的USB A接口连至主机,主机通过该接口向FPGA发送数据;将USB Mini AB接口连至USB高速设备 (选用USB 2.0Hub)。为进一步考察该系统的兼容性,在 USB 2.0Hub上同时连接一个 USB低速设备(键盘)。

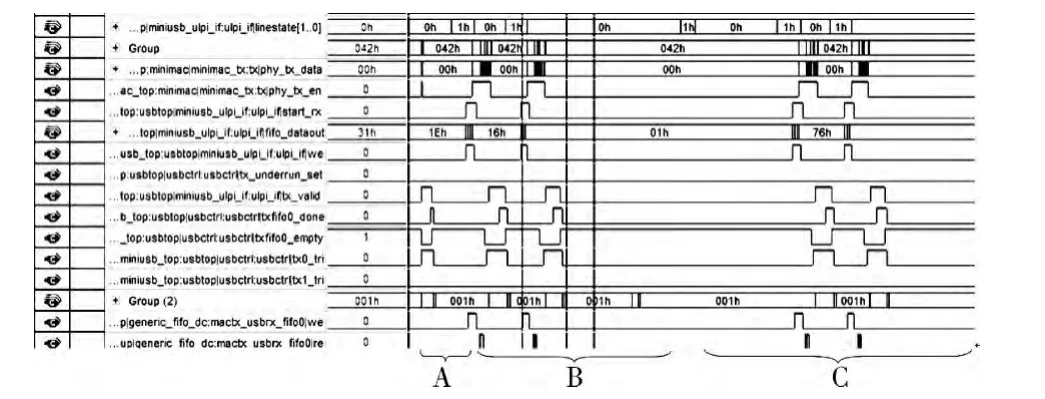

系统连接并配置完成后,复位开发板,再将连接在USB A接口的电缆接入主机。同时利用Quartus II自带的逻辑分析仪SignalTap II实时地采集并显示延长系统中的数字信号,完成系统的时序测试。SignalTap II记录了采样过程的所有数据,捕获结果如图6所示,其中过程A是主机识别设备的过程;过程B和C是主机端和设备端之间的数据或命令交换过程。

图6 逻辑分析仪SignalTap II记录的测试结果

图6可以看出,复位后,当设备接入系统时,由主机首先发出请求,并识别出设备的传输模式为高速传输,如过程A所示。一次完整的数据或命令交换过程如B或C所示,系统对不同的有效数据或命令字段的处理过程都是一样的。测试中发现,过程B和C均选用具有较高优先级的fifo0作为缓存区。miniusb和minimac对数据或命令的识别、填充等处理准确无误,未发生丢包、延时导致的错误,传输性能优良。此外,主机通过FPGA开发板可同时识别高速 (USB2.0Hub)和低速USB设备 (键盘),表明该系统具有良好的兼容性。最后,键盘通过FPGA开发板后能被快速、准确地识别并保持正常工作,证明了该系统的可行性和稳定性。

5 结束语

利用网络通信的优势,并基于修改和自定义以太网MAC与USB 2.0协议转换技术设计了延长系统,不仅实现了设备在通过100m甚至更长距离的电缆线时仍能正常运行,还实现了USB 2.0接口和以太网接口间的转换。

FPGA验证结果表明该系统具有良好的可行性、稳定性和兼容性。

协议转换原理不仅适用于文中USB 2.0延长系统的设计,还可以拓展到USB与其他网络协议 (如无线 WIFI、蓝牙等)之间的协议转换,甚至可以拓展到不同网络协议之间的转换,以更灵活方便地实现接口转换或传输延长等功能。在未来高速数据传输、远程控制等应用领域具有极大的市场价值。

[1]HUANG Tuchen,GONG Hui,SHAO Beibei,et al.Multifunctional data acquisition system based on USB and FPGA[J].Atomic Energy Science and Technology,2013,47 (11):2172-2176 (in Chinese).[黄土琛,宫辉,邵贝贝,等.基于USB和FPGA的多功能数据采集系统 [J].原子能科学技术,2013,47 (11):2172-2176.]

[2]LIU Yan,LIU Lian,LUO Junyong,et al.Fast identifying steady phase of communication network based on network signature [J].Journal of Computer Research and Development,2011,48 (z2):445-450 (in Chinese). [刘琰,刘楝,罗军勇,等.基于图形签名的通联网络平稳期快速判定方法 [J].计算机研究与发展,2011,48 (z2):445-450.]

[3]Han Kyeong-Eun,Yang Choong-Reol,Kwangjoon Kim,et al.An energy saving scheme for multilane-based high-speed Ethernet[J].ETRI Journal,2012,34 (6):807-815.

[4]Erik Patron,Candelario Pinto,Raciel Poot,et al.Design and implementation of a serial-USB converter [J].International Journal of Computer Science and Network Security,2011,11 (6):69-76.

[5]WANG Shiyu,HE Zhanzhuang,ZHANG Shengbing.Design of MAC controller based on FPGA [J].Microelectronics &Computer,2012,29 (2):171-175 (in Chinese). [王时雨,贺占庄,张盛兵.基于FPGA的以太网MAC控制器的实现[J].微电子学与计算机,2012,29 (2):171-175.]

[6]Grzegorz Polaków,Mieczyslaw Metzger.Performance evaluation of the parallel processing producer-distributor-consumer network architecture [J].Computer Standards &Interfaces,2013,35 (6):596-604.

[7]WANG Jian,WANG Hong,YANG Zhijia.New method for determining the depth of asynchronous FIFO in SoC based on the model of dynamic parameters [J].Journal of University of Electronic Science and Technology of China,2009,38 (3):447-450 (in Chinese).[王剑,王宏,杨志家.动态参数模型确定SoC中异步FIFO深度的方法 [J].电子科技大学学报,2009,38 (3):447-450.]

[8]PENG Yao,YANG Yintang,ZHU Zhangming,et al.A high-speed delay-independent synchronous to asynchronous interface [J].Journal of Computer Research and Development,2012,49 (3):669-678 (in Chinese). [彭瑶,杨银堂,朱樟明,等.一种高速延时无关同异步转换接口电路 [J].计算机研究与发展,2012,49 (3):669-678.]

[9]MA Kai, YANG Feng, WANG Yanwen.Research on USB2.0transfers interface of high speed data acquisition system[J].Computer Engineering and Design,2013,34 (11):3862-3866 (in Chinese).[马凯,杨峰,王彦文.高速数据采集系统中USB2.0传输接口研究 [J].计算机工程与设计,2013,34 (11):3862-3866.]

[10]YI Chunli,ZHANG Yanjun,WANG Jinqi,et al.FPGA control and implementation of USB2.0transmission [J].Control and Instruments in Chemical Industry,2011,38(6):733-735 (in Chinese). [易春莉,张彦军,王瑾琪,等.USB2.0接口传输的FPGA控制与实现 [J].化工自动化及仪表,2011,38 (6):733-735.]

[11]Huo Zhanpeng, Wei Zhengying,Tang Yiping.A remote control system based on short messaging service for intelligent agricultural irrigation [J].Applied Mechanics and Materials,2012,190-191:1104-1108.

[12]LIU Dong,JIN Huihua,YAN Meng,et al.Design of IEEE 1394/GbE conversion system based on SOPC technology [J].Journal of Beijing University of Aeronautics and Astronautics,2010,36 (2):214-217 (in Chinese). [刘栋,金惠华,颜猛,等.基于协议变换的图像采集系统设计 [J].北京航空航天大学学报,2010,36 (2):214-217.]