DIMA系统实时通信流量的时延分析方法

2015-05-04许晋瑞赵露茜熊华钢

许晋瑞,李 峭,赵露茜,熊华钢

(北京航空航天大学 电子信息工程学院,北京100191)

0 引 言

当前,先进的航空电子体系结构正从集中式综合向分布式综合发展,形成 “分布式综合模块化航空电子 (distributed integrated modular avionics,DIMA)” 的 概 念[1]。在DIMA系统中,为保证安全关键性处理任务的严格时间确定性,在采用分布式时钟精确同步和时间触发 (timetriggered,TT)通信的同时,需兼容既有设备的事件触发速率约束 (rate-constrained,RC)通信。SAE AS6802标准定义的时间触发以太网 (time-triggered Ethernet,TTE)[2]就是支持这种混合关键性流量的综合化航空电子网络互连解决方案。TT流量的时延确定性主要由离线设计的调度时刻表保证,W.Steiner等[3]提出由形式化方法求解组合优化问题以获得可行调度时刻表的方案,然而,设计验证过程中仍需要分析给定功能构件之间TT流量的时延参数。对于RC流量,虽然存在确定性网络演算、随机网络演算、实时演算 (real-time calculus,RTC)、轨迹法等多种分析方法,但考虑到DIMA系统中存在高优先级TT流量占用的情况,必须开发适应这种特定场景的建模与分析方法。

本文基于DIMA系统综合化互连配置的特征,从处理层次和互连层次相结合的角度,提出一套适用于分布式综合航空电子系统的流量建模与时延分析方法,即:采用体系结构分析 与设计语言 (architecture analysis and design language,AADL)描述系统的体系结构,基于体系结构模型进行TT流量的时延分析,采用模型转换的方法将体系结构模型及其具体配置转化为RTC分析模型,对RC流量的时延进行最坏情况分析。最后,结合典型的流量配置案例,对该方法进行了验证。

1 DIMA系统的AADL模型

体系结构分析与设计语言 (AADL)[4]脱胎于具有长期航空电子领域应用基础的MetaH语言,适用于描述具有实时响应要求、容错、必须经过认证的嵌入式实时系统,故特别适于对航空电子体系结构进行描述与分析。开放源码AADL 工 具 环 境 (open source code AADL tool environment,OSATE)是AADL开发小组开发与维护的一个Eclipse插件集,全面支持AADL模型的构建与前端处理[5]。本文即采用该工具开展DIMA系统的AADL建模与分析。

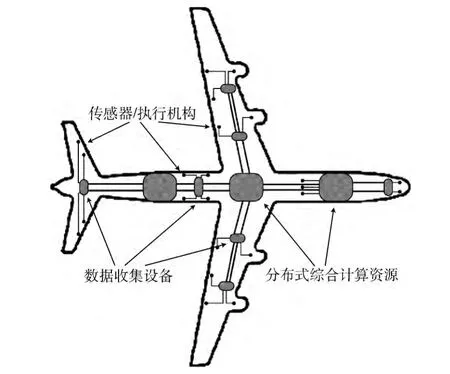

DIMA系统的体系结构兼具 “综合模块化”与 “分布式”两大优点:一方面,对共享程度很高的硬件采用模块化的构件实现,并使之具有统一的网络互连接口;另一方面,由于硬件模块和处理资源的分布式部署,允许异构的处理模块通过高精度同步的网络进行并行处理,并克服了集中式系统不利于散热的缺点,解决了其电磁兼容等环境控制问题[1,6]。综合化互连对DIMA系统优点的发挥具有至关重要的作用,图1展示出在大型飞机上DIMA系统的处理与互连方式。

图1 DIMA系统处理与互连方式

相比于集中式系统,分布式系统的核心处理资源不再集中于某个固定的区域内,而是在较大的范围分布部署;同时,可重构性提高了这些分布式资源的利用率[7]。据此,DIMA体系结构建模过程中必须着重考虑如下两点:

(1)只能在较高层次的子系统中声明分布式应用到资源的绑定情况。

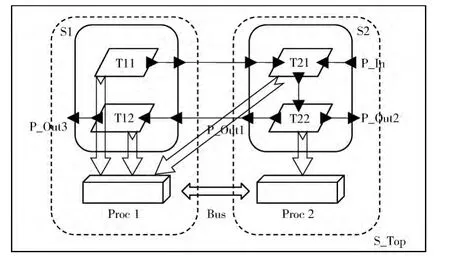

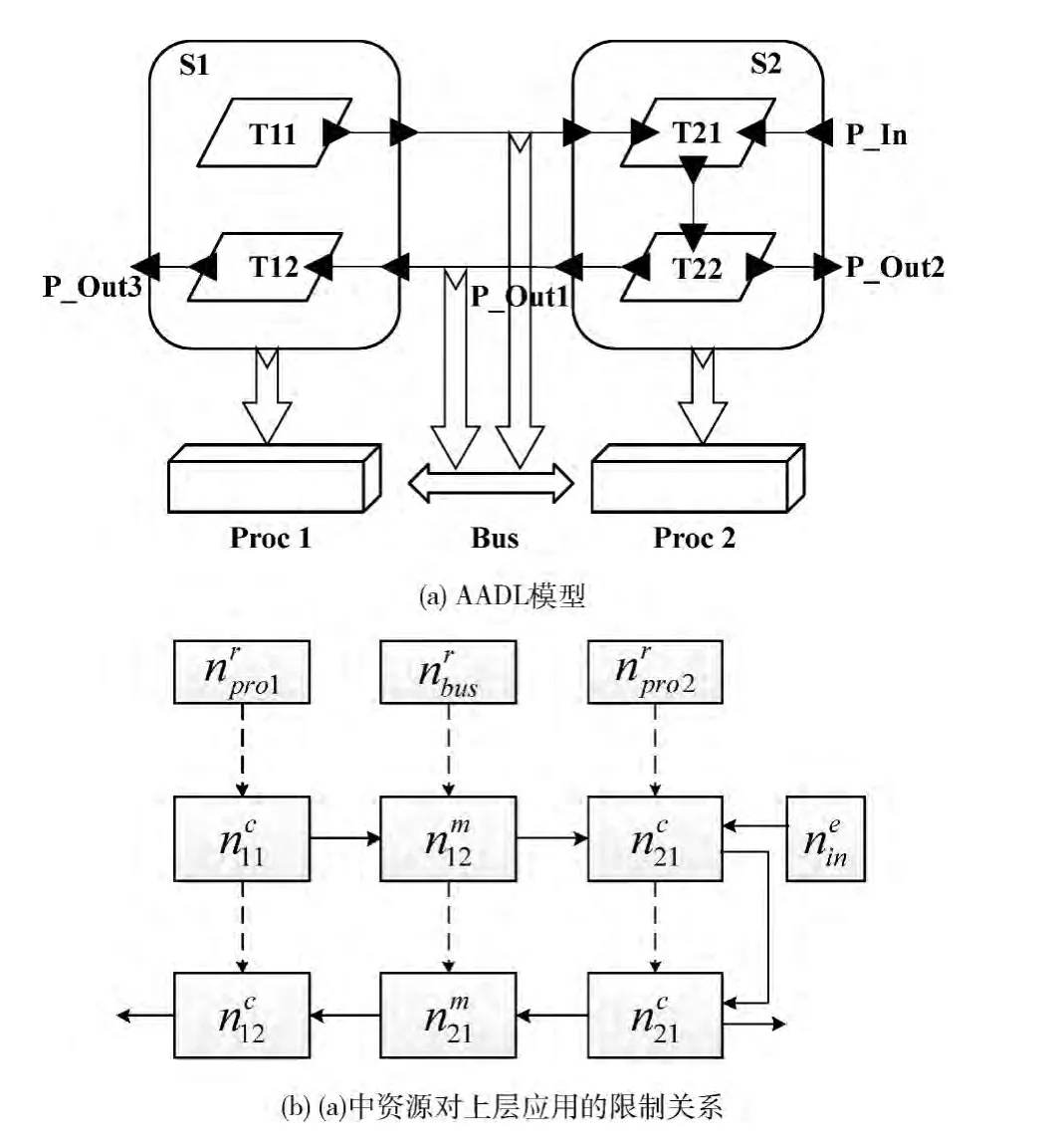

由于资源的分布式排布,上层应用完全可能绑定到其它子系统所包含的硬件资源上。这种情况下,由于该应用所绑定的硬件资源不是其所属的当前层次子系统中的构件,故只能在较高层次的子系统中对绑定情况进行声明。如图2所示的分布式系统 (空心燕尾箭头表示线程到处理器的绑定情况)中,线程T21绑定的处理器Proc1并不是子系统S2的子构件,只有在系统S_Top层次才能对这种绑定情况做出声明。

图2 一个简单分布式系统的AADL模型

(2)处理器需要针对绑定在其上的各个线程声明调度方式。

由于处理器上绑定的线程可能来自不同的上层应用(如图2中绑定到处理器Proc1上的线程T12与T21),因此建模过程中,处理器必须明确声明对绑定在其上的每个线程,特别是分布式线程 (如T21),可采取的调度方式。

2 DIMA系统的流量模型

时间触发以太网 (TTE)是实现DIMA系统互连的关键,各个分布式节点对协议控制帧 (protocol control frame,PCF)打透明时钟时戳,并根据PCF进行固化和压缩操作以实现亚微秒级的时钟校准[2,8,9],从而可支持同步消息跨越异构设备的传输。TTE网络在为时间触发 (TT)流量提供严格的时间确定性保证的同时,为保护投资,还设置有优先级较低的速率约束 (RC)和 “尽力传”服务类型[8,9]。在航空电子网络中,一般采用RC类型承载事件触发的流量。

AADL对端到端流量的模型描述,归纳定义为流规范(flow specification)、流实现 (flow implementation)和端到端流 (end-to-end flow)[4,5,10]。

“流规范”在构件类型中对该构件中流的起始 (flow Source)、从输入端口到输出端口所通过的路径 (flow path)以及终止 (flow sink)进行定义,流路径上的端口类型可以不同,而且同一个端口可包含在多个流规范的定义中。“流实现”在构件实现中通过一系列由子构件流规范的输入端口到输出端口的流路径和连接的序列对流规范的具体结构进行描述,同一个流规范可以有多种实现形式。“端到端流”在构件实现中采用关键字 “end to end flow”对一条源于子构件、途经一系列子构件并终止于子构件的逻辑信息流进行声明,虽然只涉及当前一层子构件,但子构件实现中还可以包含子构件,使端到端流的声明逐层实例化,最终得到由流规范实例和连接实例组成的端到端流的实例[10]。在图3所示的典型AADL流模型中,线程构件T1、T2和T3分别是进程构件P1、P2和P3的子构件,系统S中由P1发出,经过P2到达P3的端到端流,具体到线程层次即表现为由T1发出,经过T2到达T3的端到端流。相应的代码形式的AADL模型描述如图4所示。

图3 AADL流模型

图4 图3中模型的代码描述 (部分)

3 DIMA通信流量的时延分析

为保证数据和事件的时间确定性满足实时性能要求,从航空电子系统设计初期开始就需要对信息流量进行时延分析。在DIMA系统中,由于分布式计算和通信的实时行为既与网络通信任务的配置有关,又涉及资源的规划设计,故有必要从处理层次和互连层次相结合的角度综合考虑,进行较为全面的时延分析。据此,本文拟定如图5所示的DIMA系统通信流量时延分析方案。

3.1 时间触发流量的时延分析

时间触发 (TT)流量是在封闭性系统中的时间确定性信道上进行传输的:一方面,系统中客户端之间通过中心调度器实现协作,建立无冲突的全局调度方案;另一方面,对于具有时间确定性的传输信道,消息的最大和最小传输延迟由设计者预先设定,以确保消息传输时延的有界性[9]。因此,TT流量的端到端传输过程中不存在因传输协议或多路复用造成的排队延迟,只需在处理层次进行时延分析。

AADL提供了基于流模型的时延分析框架。该框架认为,端到端流的时延主要受如下4种因素影响[10]:

(1)处理时间:主要包括执行时间和完成时间,相关的属性有计算执行时间Compute_Execution_Time、截止期限Deadline、周期Period等,最坏情况的处理时间分析主要考虑Deadline以及Period。

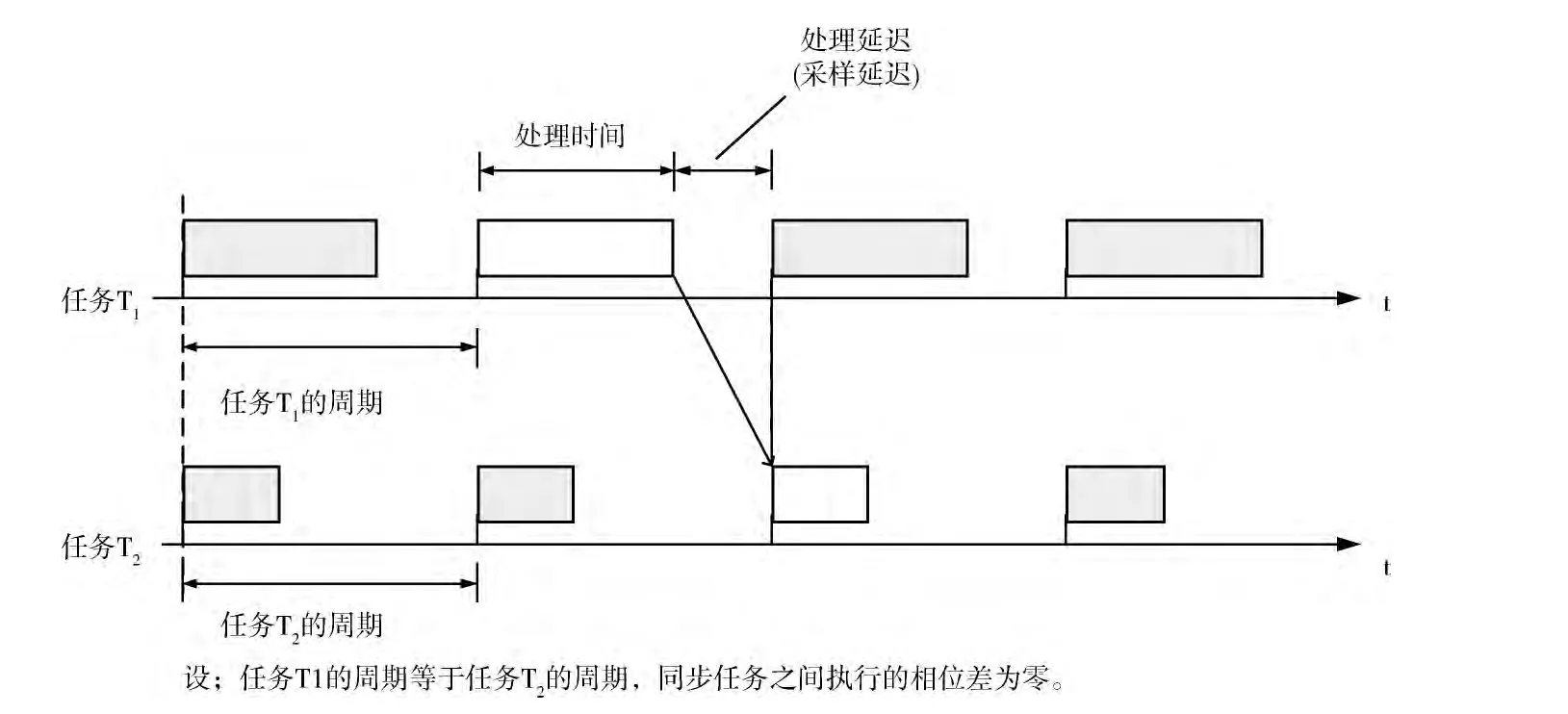

(2)处理延迟:不同采样方式造成的处理延迟是不同的,由于TTE网络为系统提供了精确的分布式时钟同步,需按照同步采样的方式进行计算——处理时间加上所有的传输时间和延迟之后,再以采样周期上取整,如图6所示。

(3)传输时间:主要受数据块大小、连接或传输设备的速度,以及传输协议开销的影响,相关的属性包括数据块大小Source_Data_Size、传输时长Transmission_Time等。

(4)传输延迟:这是实际传输协议或多路复用排队的结果,需要借助框架之外的工具,并结合综合化互连、流量约束等信息进行分析。相应的属性为Propagation_Delay,其值需要由设计者预先给定。

OSATE平台集成有相应的分析工具,即,流时延分析插件 (flow latency analysis plug-in)。该插件利用前文所述的相关属性值,对特定流量的端到端时延进行分析计算,并以信息提示的形式给出结果。

3.2 速率约束流量的时延分析

对于速率约束 (RC)流量,由于TTE并不提供严格的时间确定性保证,传输过程中可能存在因传输协议规定或多路复用造成的排队延迟,因此,在利用AADL流时延分析插件进行处理层次时延分析的同时,还需要充分考虑传输过程中的排队延迟,在互连层次进行分析。

AADL流时延分析框架的一个局限在于,无法通过自身的分析计算得出表征传输延迟的属性值而需要设计者预先给定,故必须借助其它分析方法为该预设过程提供支持。作为网络演算在实时应用领域的扩展,实时演算(RTC)[11]基于精确描述事件流时间特征的事件模型,实现实时系统中各构件的时间性能、缓冲区需求和负载状况的分析求解。

采用RTC进行互连层次时延分析的前提是,系统AADL模型中必须包含构建相应RTC模型所需的参数。这些参数主要描述系统各个节点输入的事件流的到达曲线、服务曲线,以及通信和处理过程的历时,如处理器和线程的调度方式、总线的带宽等。特别地,作为流量的入口和出口,构件的端口应当为RTC描述输入流特性的周期-抖动-延迟 (period-jitter-delay,PJD)模型提供相关参数。对此,可定义两个属性:输入速率 “Input_Rate”取值为范围 [s,p],其中,s表示在到达的事件流中相邻两个到达事件的最小时间间隔 (参数D),p表示该事件流的周期(参数P);输入抖动 “Input_Jitter”的值表征PJD模型中的参数J[11]。

图5 DIMA通信流量的时延分析方案

图6 同步采样造成的处理延迟

由于AADL并未深入考虑互连层次的具体实现情况——一部分所需的参数 (如:线程的调度方式、PJD模型相关的端口属性等)是标准AADL中未定义的,因此,需借助AADL的可扩展性[4,5],对标准AADL属性集进行扩展,为相关构件增加适于表征具体互连特征的属性,以补充与完善AADL模型,使之适用于互连层次的时延分析。

与RTC参数相关的自定义属性集的部分代码如图7所示。

图7 与RTC参数相关的自定义属性集

4 AADL模型向RTC模型的转换

在跨越处理和互连两个层次进行时延分析的过程中,时间触发 (TT)流量可以直接在AADL流时延分析框架下进行分析,而对速率约束 (RC)流量的分析必须借助其它专用的分析模型,即实时演算 (RTC)模型。因此,必须实现从AADL模型到RTC模型的转换,并且使转换后的模型可以利用RTC分析工具快速获取必要的时延参数;将这些参数加入到AADL体系结构模型中,以使体系结构模型的成熟度随设计过程的深入而不断提升。值得说明的是,模型转换不仅涉及RC流量,考虑到TT流量 (高优先级)在传输过程中会对RC流量 (低优先级)造成影响,TT流量的配置和性能指标同样需要一并转换。

在具体的转换过程中,要保持模型意义的一致性,必须结合流量和资源两个角度综合考虑,而从AADL模型中准确提取出资源对上层应用的限制关系,是保证模型一致性的关键[11]。

资源角度——排定绑定在各个硬件资源上的应用的优先次序,次序较前者享有使用硬件资源的优先权:①对于处理器,按照与调度方式相应的属性值排定绑定在其上的线程的优先次序,如对绑定在固定优先级 (FPS)调度方式的处理器上的线程,应当按照各自的优先级属性值进行降序排列;②对于总线,按照复用方式排定绑定在其上的连接的优先次序,如对TDMA方式,需先按照各自所占据的时隙对连接进行分组,每个时隙内部再进行排序,优先级高的连接享有对该时隙的优先访问权。

流量角度——在应用已按资源利用的优先权完成排序后,依照流量方向,顺次连接所经过的各个应用节点。

按照上述方法,可从图8(a)所示的AADL模型中提取出资源对上层应用的限制关系,如图8(b)所示。其中,上标r、e、c、m分别代表资源节点、输入事件源节点、计算节点 (对应于线程构件)和消息节点 (对应于连接构件)。

获得资源对应用的限制关系后,需要再次按资源方向检查各个应用节点,将符合特定条件的多个节点进行合并 (如,接受EDF调度的多个节点可合并为一个EDF调度模型抽象节点),形成最终的RTC模型。在生成的RTC模型中,硬件资源的服务曲线沿资源利用优先级方向 (纵向)“传递”,各流量的到达曲线沿流量方向 (横向)“传递”。

以上述模型转换思想和方法为指导,本文开发了实现AADL模型向RTC模型转换的插件。该插件以DIMA系统AADL体系结构模型为分析对象,提取系统实例中的端到端流量信息和流量方向上各个应用节点中与RTC建模相关的属性值,整合并存储为以流量为导向的XML文件;提取该XML文件中的资源信息并整理生成以资源为导向的XML文件;对流量导向和资源导向的两个XML文件提供的信息进行综合分析,最终生成存储RTC模型的Matlab文件。

图8 一个简单系统的AADL模型及其资源对应用的限制关系

5 案例研究

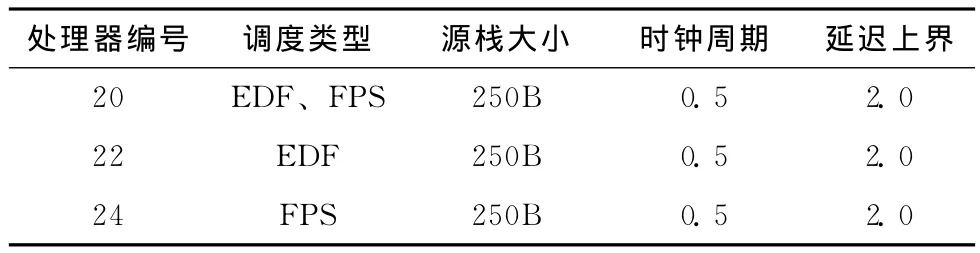

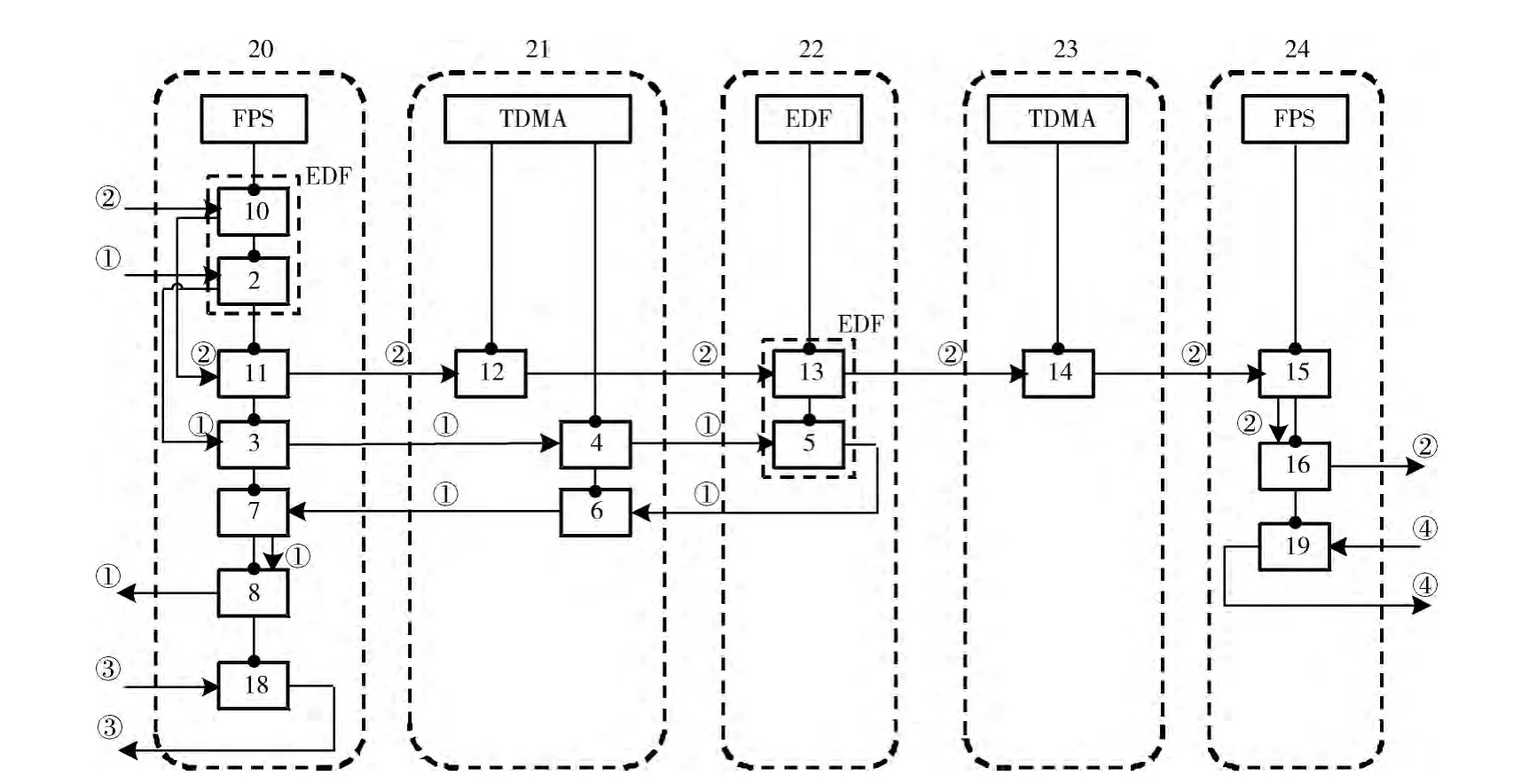

图9展示出一个简单DIMA系统案例的AADL模型。由于页面篇幅所限,用数字编号代表系统中的子构件。主要构件中相关属性值的设定情况详见表1、表2和表3(时间单位均为微秒)。

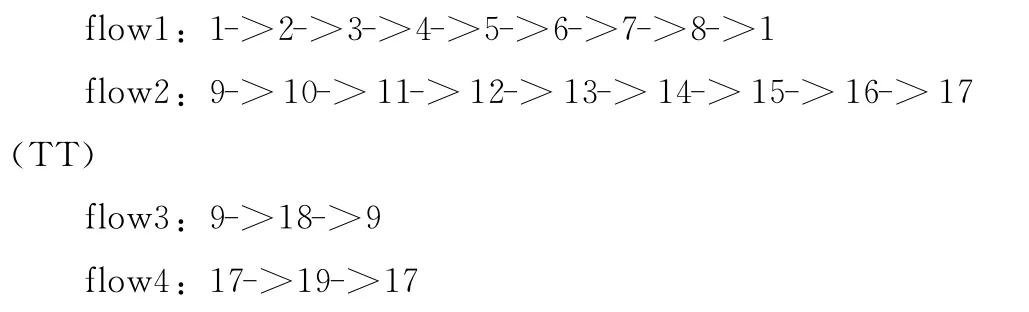

为便于讨论,将图9中4条端到端流量进行编号:

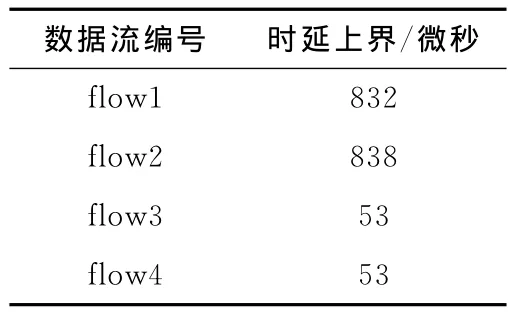

首先,借助OSATE平台上的AADL流时延分析插件进行处理层次的时延分析,计算得各条流量的时延上界见表4。然后,使用自行开发的模型转换插件,将图9所示的AADL模型转化为RTC模型 (如图10所示),并通过瑞士联邦技术学院开发的RTC分析工具RTCToolBox对该模型进行互连层次的时延分析,计算得各个节点的互连层次时延上界见表5。

图9 DIMA系统案例AADL模型

表1 各线程的主要属性值设定

表2 各处理器的主要属性值设定

表3 各流量输入端口的主要属性值设定

表4 图9中系统模型的处理层次时延分析结果

表5 图9中系统模型的互连层次时延分析结果

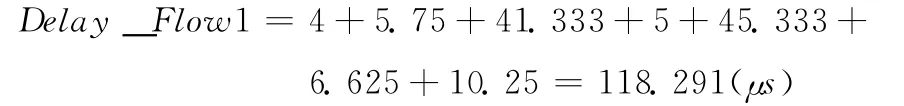

对于flow1,因其流经多个节点,将所流经的各个节点的时延上界相加,可得到一个总体的时延上界

另一方面,依据 “Pay Burst Only Once”原则计算所得的时延上界为117.042μs,显然,后者是一个更 “紧”的确界。

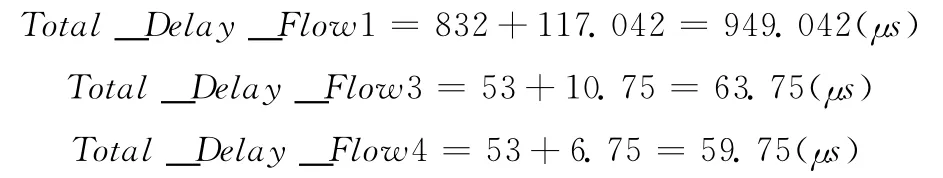

下面,对两个层次的分析结果进行综合:

图10 由图9中AADL模型转化而来的RTC模型

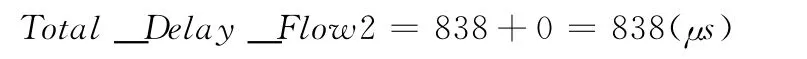

对于TT流量flow2,由于不存在因传输协议或多路复用造成的排队时延,故综合考虑处理和互连两个层次的时延上界为

对于其它3条RC流量,将处理层次和互连层次的分析结果相加,即得到综合考虑两个层次的时延上界

在按照上述方法求得各条流量的时延上界参数后,即可利用这些参数开展系统实时性能评价,以及必要的迭代设计等后续工作。

6 结束语

本文基于DIMA系统特征,使用AADL语言建立系统体系结构模型和流模型,结合AADL流时延分析框架和RTC,提出一套处理与互连层次相结合的端到端流量的时延分析方法。该方法通过自行开发的插件将AADL模型转换为RTC模型,在AADL体系结构模型与专业的RTC分析工具之间建立有机联系,实现了跨层次的时延分析,可用于分布式综合航空电子系统设计过程中通信任务的时间确定性分析与评价。

此外,在研究过程中发现,目前AADL语言在描述互连通信方面存在明显的局限,如表征硬件设备之间互连的总线构件非常抽象,难以准确表述实际传输网络中的分组交换情形等。因此,随着DIMA系统在航空电子领域的逐渐推广,AADL语言有必要增加相应的硬件设备互连建模符号的语义。

[1]Wolfig R,Jakovlievic M.Distributed IMA and DO-297:Architectural,communication and certification attributes [C]//IEEE 27th Digital Avionics Systems Conference,2008.

[2]SAE AS6802,Time-triggered Ethernet [S].2011.

[3]Steiner W.Synthesis of static communication schedules for mixed-criticality systems [C]//14th IEEE International Symposium on Object/Component/Service-Oriented Real-Time Distributed Computing Workshops,2011:11-18.

[4]SAE AS5506, Architecture analysis & design language(AADL)[S].2004.

[5]Feiler PH,Gluch DP.Model-based engineering with AADL:An introduction to the SAE architecture analysis & design language [M].Addison-Wesley Professional,2012:1-312.

[6]Fuchsen R.IMA NextGen:A new technology for the Scarlett program [J].IEEE A&E System Magazine,2010,25 (10):10-16.

[7]Perez H,Gutierrez JJ,Asensio E,et al.Model-driven development of high-integrity distributed real-time systems using the end-to-end flow model[C]//37th EUROMICRO Conference Software Engineering and Advanced Applications,2011:209-216.

[8]Steiner W.TTEthernet specification [S].TTTech Computertechnik AG,ver.0.9.1-22968,2008.

[9]Kopetz H.The rationale for time-triggered Ethernet [C]//Real-Time Systems Symposium,2008:3-11.

[10]Peter F,Jorgen H.Flow latency analysis with the architecture analysis and design language(AADL)[R].Software Engineering Institute of Carnegie Mellon University,2007:1-53.

[11]Sokolsky O,Chernoguzov A.Analysis of AADL models using real-time calculus with applications to wireless architectures[R].University of Pennsylvania Department of Computer and Information Science,2008:1-24.