时序基准电路S344可测性设计

2015-04-19赵树军王永强

赵树军,王永强,张 帅

(黑龙江工程学院 电气与信息工程学院,黑龙江 哈尔滨 150050)

时序基准电路S344可测性设计

赵树军,王永强,张 帅

(黑龙江工程学院 电气与信息工程学院,黑龙江 哈尔滨 150050)

以时序电路的可测性设计方法为主要研究内容,针对时序电路中由于时序元件的可观测性和可控制性比较差,导致测试生成难度较大,并且存在影响测试故障覆盖率的问题。以固定型故障模型的检测为研究基础,通过对时序电路进行扫描测试技术的可测性设计,解决时序电路中内部节点难以测试的问题。设计实现的目标是以尽可能少地插入可测性设计的硬件逻辑,提高被测时序电路的故障覆盖率。

可测性设计;扫描测试技术;硬件描述语言;网表;测试故障覆盖率

通常对集成电路的用户而言,所应用的芯片是经过了若干复杂步骤而获得的,那么对芯片的实现一般要经历4个阶段,分别是集成电路设计阶段、制造阶段、晶圆片测试和已封装芯片的测试[1]。工作人员用Verilog语言绘制HDL代码到设计芯片中,也决定该芯片所能支持的所有技术特征,是整个设计过程的基础工作,如果错误过多将延长验证阶段的周期,从而增加研发成本[2]。通过晶圆片测试和封装的芯片还不能算作真正意义上的产品,仍然要进一步进行故障测试,以确认封装好的芯片是否有故障,通过此阶段故障检测才能进入市场,成为真正的半导体产品[3]。在产品的设计开发阶段考虑集成电路的可测性问题,这就是所谓的可测性设计(Design For Test,DFT)问题[4]。可测性设计技术的提出和应用对于保证芯片产品质量,降低测试成本的开销,缩短产品上市时间,都具有十分重要的意义。

在集成电路实际设计和可测性设计开发时,还需对扫描技术的设计优化问题进行深入研究。优化的DFT技术对于提高故障覆盖率、降低芯片硬件开销、减少生产和测试构成的芯片成本而言是很关键的,因此,在掌握集成电路DFT设计技术的同时,还要结合优化技术,将其更好地用于实际工程中。

本文采用时序基准电路ISCAS′89中的S344为待测电路进行时序电路的全扫描测试技术的可测性设计。原有时序电路的门级网表中只是功能设计,不含有DFT技术,对此修改门级网表,增加新的逻辑单元和连接关系,将原有时序电路中难以控制和观测的时序元件构成具有扫描测试的结构,使得电路故障测试能力提高。并对所修改的具有扫描测试技术的门级网表进行故障仿真,然后进行自动测试向量生成工作,并对时序电路S344的扫描可测性设计技术进行分析。

1 扫描测试技术原理与方案实现

1.1 扫描测试技术原理

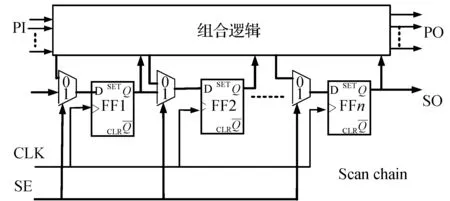

对于一些特定类型的器件,如时序电路,为了缩减测试开发和测试应用时间以及测试成本,提高测试故障覆盖率,所利用的途径之一就是应用扫描测试。将时序元器件通过一定硬件逻辑和连接方式构成的测试电路来完成测试的方法叫扫描测试,是一种故障覆盖率较高的结构化设计方法,其原理是将时序电路抽象为组合电路和扫描链部分,并配合一定的时钟周期来进行测试。图1所示的普通模式下的钟控同步逻辑电路就是对面测试很好的描述[5]。

图1 普通逻辑电路

图1模式下,电路的主要组成部分组合逻辑段和一连串的存储单元(M1,M2,…,Mn)是由系统时钟控制的。组合逻辑得到的输入包括器件的输入(原始输入)和从存储单元反馈回来的第二级状态变量,与当前状态共同作用控制了器件的输出(原始输出)。

经过以上方法,存储扫描设计和建立途单元的扫描路径问题基本上得到解决。如图2所示,每个存储单元之前都增加一个通用扫描选择信号控制下的多路选择器。当信号关闭时,多路选择器连通组合逻辑的输出端与存储单元的输入端,电路处于通常的工作模式下;当选择信号打开,存储单元被重新配置为独立的串入/串出移位寄存器。

图2 加扫描后的逻辑电路

通常称串行数据输入端为扫描输入(Scan Data In),串行数据输出端也被称为扫描输出(Scan Data Out)。通过在扫描输入端口依次置入数据并以系统时钟锁存移位寄存器,在扫描模式下把所有的特殊数值放入到存储单元中[6]。

1.2 时序电路S344的扫描测试设计方案的实现

因为实验所用的是S344电路。现在将原始的元件数量加以统计,用以和通过可测性设计的S344进行对比。原始的S344包括9个输入、11个输出、15个D-type flipflops、59个inverters、44个ANDs、18个NANDs、9个ORs、30个NORs,如图3所示,通过对S344的端口添加二选一多路选择器用以完成可测性设计[7]。

图3 S344的可测性设计

以下是通过修改后的S344的元件数统计,在DFF端加入二选一多路选择器的方法来完成可测性设计。PI为原始输入端口(Primary Input),PO为原始输出端口(Primary Output),为了实现扫描功能需要增加3个额外的I/O引脚,它们分别是:扫描输入(Scan Input,SI),扫描输出(Scan Output,SO)和扫描控制端(Scan Enable,SE),其中扫描输入/输出引脚可以和其他输入/输出引脚复用。扫描路径中,在每个触发器前都增加一个两输入的多路选择器(二选一多路选择器由一个非门、两个与门和一个或门组成。总共添加了15个非门,30个与门,15个或门),其输入端分别为前一个触发器的输出和原始设计中所接收的信号。扫描路径上所有触发器的控制端都统一接在控制线SE上,确定触发器是处在正常模式还是测试模式。正常工作模式时,SE置0,电路按原始设计连接。测试模式时,SE置1,电路中的触发器形成移位寄存器结构,即构成扫描链(扫描路径)。

S344作为ISCAS89中的一个时序电路是以网表的形式描述,本文的工作在原始网表的基础上进行时序电路的可测性设计,根据上述对扫描测试技术的分析,在进行S344可测性设计的过程中,需要增加多路选择器,则在S344原始网表中给出二选一多路选择器的定义,如图4所示。

图4 扫描路径

二选一多路选择器的输入有3个端口,分别为2个信号输入端PI,SI,一个选择信号SE,PI为原始输入端,SI为扫描输入,SE为扫描控制端,当SE信号为“1”时,扫描链是在测试模式下,信号SI通过多路选择器,当SE信号为“0”时,扫描链在非测试模式下,信号PI通过多路选择器[8]。

2 实验结果与分析

2.1 对比电路功能测试

如图4所示,因为该时序电路的设计工作是通过在原电路的D触发器前添加二选一多路选择器的方式用以完成S344的可测性设计,在提高故障检测能力的同时,也必须保证原电路S344的功能没有变化,因此,需做以下验证。将带有扫描结构的S344的SE=0,在原始输入端输入随机施加的向量,测试激励的Verilog程序如下:

Initial

Begin:

C k=0;

S i=1;

S e=0;

START=1;

B O=1;

B 1=1;

如何缓解电压暂降问题并采取有效的措施是一个难点。为了解决这些问题,下面以绵阳区域电网某220 kV配电系统为例,建立了仿真模型。通过与现场实测数据进行对比,分析了该区域电压暂降的原因,提出了相应的缓解措施,对改善后的效果进行预估计,利用仿真结果在敏感设备曲线上绘图,研究各类设备的敏感性以达到对该区域的电压暂降评估分析的目的。

B 2=1;

B 3=1;

A O=1;

A 1=1;

A 2=1;

A 3=1;

End

S344

S 3 4 4(.G N D (),.V D D (),C K(C k),.A O(A O),.A1(A1),.A2(A2),.A3(A3),.

PO(),.P1(P1),.P2(P2),.P3(P3),.P4(P4),

,.SE(se),.SI(si);

Endmodule

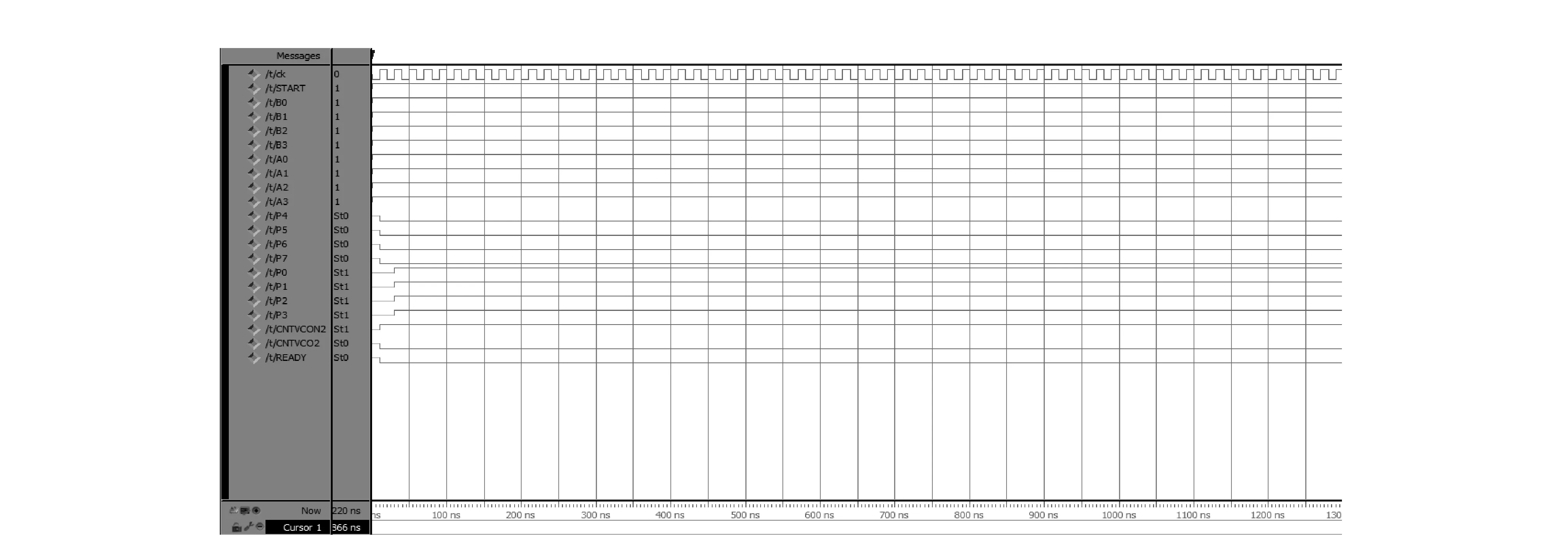

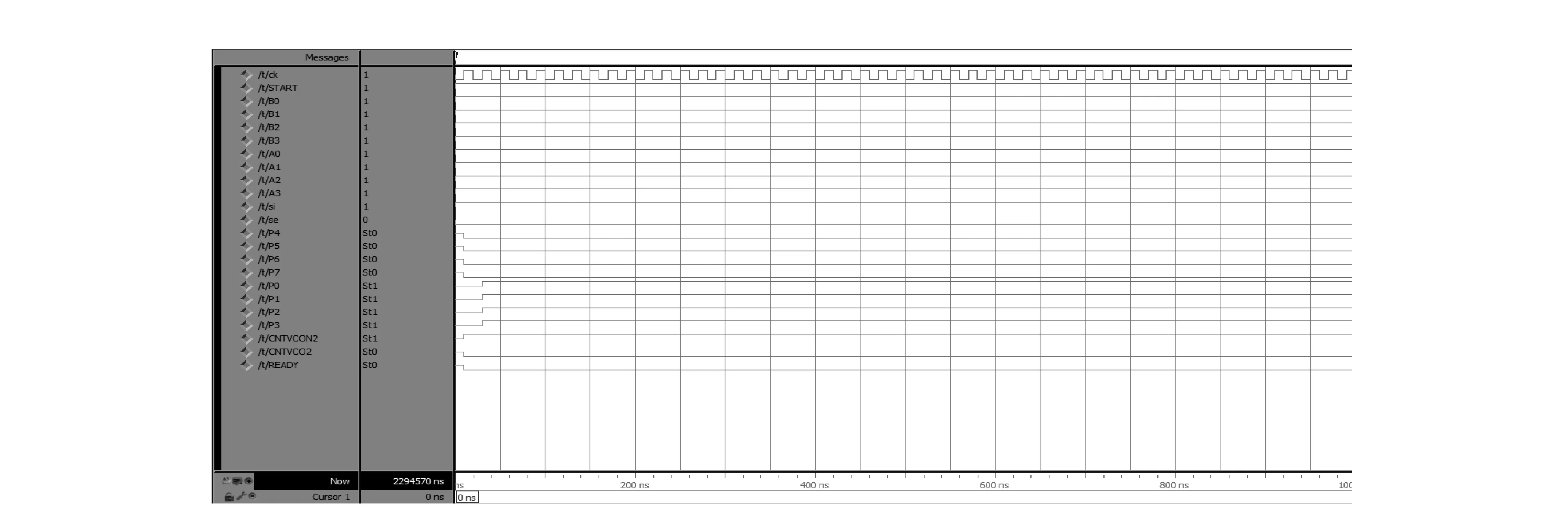

将A0=1、A1=1、A2=1、A3=1、B0=1、B1=1、B2=1、B3=1、CK=0、SI=1、SE=0得输出结果:tp4=1、tp5=1、tp6=1、tp7=1、tp0=0、tp1=0、tp2=0、tp3=0、CNTVCON2=0、CNTVCO2=1、READY=1,具有扫描测试结构的S344电路原始功能仿真结果如图5所示。

为了比较和分析添加了可测性结构是否改变电路功能,本文又将原始S344时序电路(未添加多路选择器)的输入端输入向量,同时保证与S344时序电路(添加多路选择器)的输入向量相同,并将仿真结果与原S344的结果进行对比,如图6所示。

结果表明,在输入完全相同的情况下,两种电路的输出亦完全相同。因此,在S344的D触发器前添加多路选择器来完成可测性设计,未改变时序电路S344的测试激励程序如下:

Initial

Begin

图5 具有扫描结构的S344扫描结果

图6 原始电路功能仿真结果

START=1;

B 0=1;

B 2=1;

B 2=1;

B 3=1;

CK=0;

A 0=1;

A 1=1;

A 2=1;

A 3=1;

end

always # 10 ck=~ck;

VDD(),.CK(CK),.A0(A0),.A1(A1),.A2(A2),.A3(A3),.B0(B0),.B1(B1),.B2(B2),.B3(B3),.CNTVCO2(CNTVCO2),.CNTVCO2(CNTVCO2),.P0(P0),.P1(P1),.P2(P2),.P3(P3),.P4(P4),.

P5(P5),.P6(P6),.P7(P7),.READY(READY),.START(START);

Endmodule

将CK=0、START=1、B0=1、B1=1、B2=1、B3=1、A0=1、A1=1、A2=1、A3=1,得输出结果:tp4=1、tp5=1、tp6=1、tp7=1、tp0=0、tp1=0、tp2=0、tp3=0、CNTVCON2=0、CNTVCO2=1、READY=1。本文主要对S344的可测性进行研究,对原始电路的实现功能并不需要重点了解,因而对电路功能不做讨论。

2.2 故障测试及仿真

运用tetramax对原始的S344进行故障仿真,得出以下测试结果:通过图7可以看出,原始的S344共有136个错误,其中不可测试的错误为12个,由于时序节点的不可控制和不可观察,导致该电路含有大量ATPG工具无法检测故障,因而导致该电路成为一个难以检测的电路,故障覆盖率为0[10]。

图7 原始电路故障仿真结果

为解决时序电路中大量不可测试故障节点的存在,本文在原有S344电路基础上,进行了可测性设计,运用扫描测试结构,解决时序电路难以检测的问题,再对添加了可测性设计的S344进行故障仿真,得到的结果如图8所示。

图8 具有扫描测试结构的电路故障仿真结果

由图8可以看出,添加了可测性设计的S344共有292个错误,其中不可测试的错误为19个,而ATPG工具不可测试的故障为0,并且测试故障覆盖率可以达到100%。比较结果表明,本文所设计的具有扫描测试结构的时序电路S344可明显提高故障测试覆盖率。

由图9的测试向量报告得出,测试的向量数为8个。换言之,对于一个具有扫描测试结构的S344电路,其仅需要8个测试向量就可达到100%的测试故障覆盖率。

图9 具有可测性设计结构的S344测试向量报告

此为修改后的测试结果,从图10可以看出扫描链中15个DFF触发器在SE=1全部出现,所以证明在SE=1所设计的扫描链结构正确[11]。

图10 扫描链结构验证

3 结束语

本文阐述了可测性设计在数字集成电路中的重要性,并通过对原电路中添加二选一多路选择器的方式完成了对数字电路的可测性设计。且在最后对添加了可测性设计的S344与原始的S344同时给出相同的随机输入激励,得到完全相同的输出结果。其后对添加可测性设计的S344与原始的S344同时进行故障覆盖率的仿真,得出加入可测性设计的S344的故障覆盖率远大于原始的S344的故障覆盖率,且仅需要8个测试向量。最后又证明了所设计的扫描链是完全正确的,从而可以知道通过在原电路中加入二选一多路选择器的方式能较理想地解决对电路测试覆盖率的测试问题。

[1] YEO K.S.,ROFAIL S S.,GOH W.L.低压低功耗CMOS/BiCMOS超大规模集成电路[M].周元兴,张志龙,等译.北京:电子工业出版社,2010:124.

[2] 吴德馨,钱鹤,叶甜春.现代微电子技术[M].北京:化学工业出版社,2012:64.

[3] 伊藤秀男,野口孝树,藤原洋.VLSI与数字信号处理[M].北京:科学出版社,2009:78.

[4] 谢永瑞.VLSI概论[M].北京:清华大学出版社,2002:187.

[5] 王振宇,成立,高平,等.先进的芯片尺寸封装(CSP)技术及其发展前景[J].半导体技术,2003,28(12):39-43.

[6] RESSELL S.规划综合性强、性价比高的芯片测试策略[J].半导体技术,2003,28(6):38-40.

[7] 叶明均,颜学龙,雷加.伪随机测试生成在混合电路参数测试中的应用[J].半导体技术,2003,28(9):25-28.

[8] 成立,李彦旭,李春明.开发LSI DAC新品的技术综述[J].半导体技术,2001,26(6):1-3.

[9] 高平,成立.数字VLSI电路测试技术-BIST方案[J].半导体技术,2003,28(9):29-32.

[10] 安捷伦科技硅芯片系统测试部.DFT时代的ATE结构-多端口ATE[J].半导体技术,2003,28(6):41-43.

[11] 赵树军.CMOS轨到轨电压跟随器的设计及优化[J].黑龙江工程学院学报:自然科学版,2013,27(2):61-64.

[责任编辑:郝丽英]

The testability design of sequential circuits S344

ZHAO Shu-jun,WANG Yong-qiang,ZHANG Shuai

(College of Electrical and Information Engineering, Heilongjiang Institute ofTechnology, Harbin 150050)

Because of temporal element in sequential circuits with poor observability and controllability, the test generation leads to be difficult, and the fault coverage problems will occur. The design of sequential circuits is studied. Base on a fixed type failure model, through the study of the scanning measurement technology of sequential circuits of measurability design, the problem of internal nodes in the sequential circuits is difficult to test. This design will realize the as little as possible goals on insertion measurability design of the hardware logic, and improve the fault coverage of the sequential circuit under test.

testability design; scanning measurement technology; hardware description language; net list; test fault coverage

2014-09-22

2014年黑龙江省教育厅规划课题(GBC1214057)

赵树军(1970-),男,副教授,研究方向:应用物理及电子技术.

TN722

A

1671-4679(2015)02-0013-05