逐次逼近(SAR)模数转换器进展

2015-03-28刘萌马奎刘娇傅兴华

刘萌,马奎,刘娇,傅兴华

(贵州大学电子科学系贵州省微纳电子与软件重点实验室,贵州贵阳550025)

逐次逼近模数转换器(SAR-ADC),具有中等速度与精度,低成本和低功耗的综合优势。在工业控制、医学仪器、随身设备、军事侦察等多方面应用广泛。近些年来,SAR-ADC在追求低功耗的道路上取得不少亮点。其中在DAC部分的不转换窗口的概念[1](no-switching window)比传统二进制逼近节省50%左右的功耗。在此基础上又提出了时间窗口(time-based fixed window)概念[2],电源电压只有0.5 V,在100 kS/s速度下功耗FOM只有3.9fJ/conversion-step。在数字逻辑部分采用基于计数器的结构,可以比传统SAR逻辑电路减少30%功耗。此外随着CMOS器件速度的不断增长,SARADC也逐渐渗透到了高速领域,建立起fast conversion loop的概念。采用时间交织技术(time-interleaved)的SAR-ADC已经达到了7bit精度下1.5 GS/s的采样速率[3]。考虑到通道间的不匹配,需要添加额外的校准电路。最近的2bit/cycle的技术[4]提供了新选择,即每个循环两次逼近。在8位精度下也达到了400 M/s的速度。随着CMOS电路尺寸缩小,规模的增大,晶体管或运放的固有增益降低。使得对运放要求相对较低的SAR结构模数转换器更加受到欢迎。因此,最近的研究都集中到SAR模数转换器上。

1 逐次逼近型模数转换器基本结构

SAR-ADC主要模块包括S/H电路、数模转换器(DAC)、比较器、逻辑控制电路等。如图1。通过Vi与不同权重的Vref比较来逼近Vi,并输出编码。

图1 SAR-ADC的主要结构Fig.1 Mian structure of SAR-ADC

2 SAR ADC中的数模转换器(DAC)

2.1 DAC的主要结构

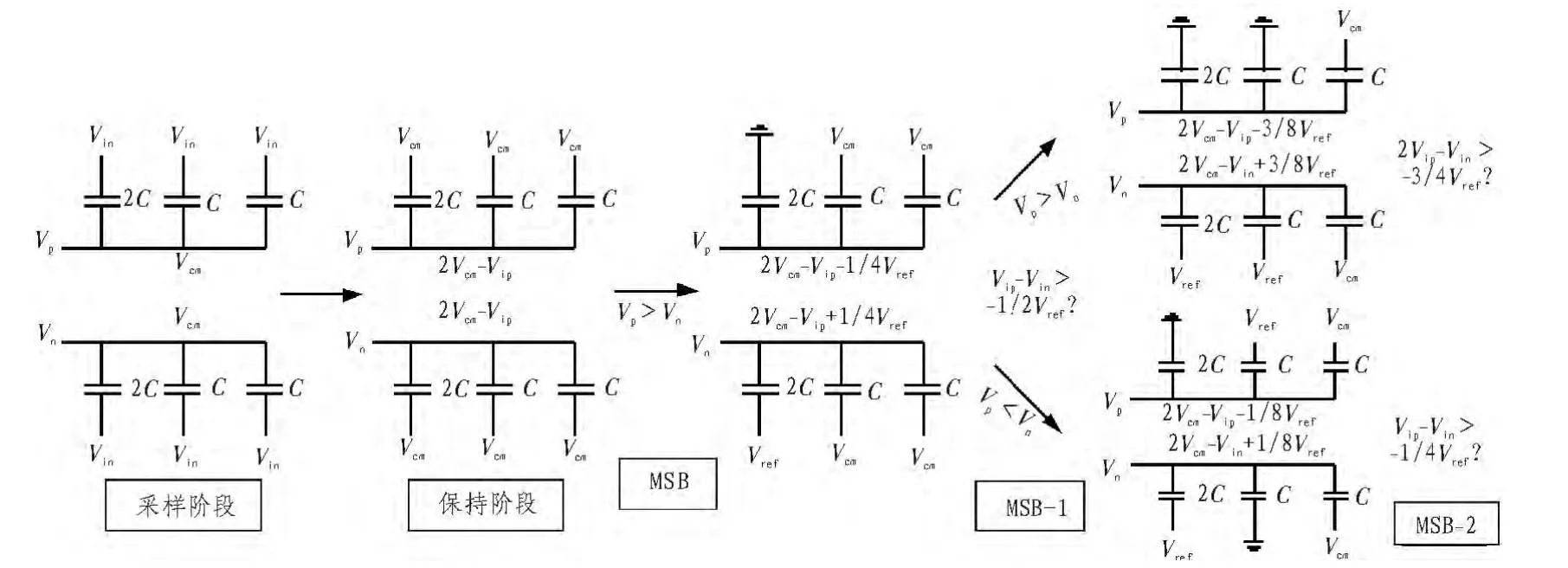

DAC有电压定标型、电流定标型、电荷定标型。其中多采用电荷定标(CDAC),功耗较低且不需要专门采样保持电路。CDAC由二进制权重电容阵列,LSB等值电容、开关和比较器组成。图2为2位的电容阵列与转换步骤。首先对信号进行采样与保持。之后通过将MSB电容接Vref来产生1/2Vref(电荷再分配),并进行比较。以此类推完成二进制搜索算法,直到最低位(LSB)结束。

随着分辨率(位数)的增加,电容值也成指数增加。采样充放电时间延长,转换速度下降。可使用桥接电容来构成分段电容阵列。如图3所示。

图2 电容阵列转换步骤Fig.2 Conversion of CDAC

图3 整数桥接电容Fig.3 Integral split-CDAC

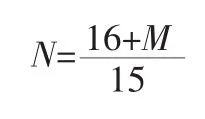

由一个桥接电容Cs将电容阵列分为高位电容与低位电容。并使得∑C低位电容+CS=C高位单位电容。为使桥接电容为整数,会在低位电容阵列上加个接地电容CF。桥接电容CS与低位接地电容CF的大小关系由电荷再分配决定。具体的计算不再详述。以图中结构为例,最后得到M、N的关系为:

当N=1时,M=-1,这表示去掉低位电容阵列中的一个单位电容。以8位电容为例,电容总量由原来的256 C减小到32 C。

2.2 DAC的精度

影响DAC精度的主要有两个方面:电容失配以及噪声。图3中的虚线部分是简单的寄生电容模型。CP2、CP3存在于金属与衬底间。CP1存在于金属之间。通常这些非理想因素限制了DAC的精度,也限制了单位电容的最小值。

为了减少电容间的失配,通常选用匹配度较好的MIM(Metal-insulator-Metal)电容或者(fringe capacitor)边缘电容。失配率从传统HPP电容2.3%提升到MIM电容(高k值)的0.3%·μm[5]。尤其边缘电容在小电容(1.2 fF)匹配度方面同样能达到0.8%[6]。对于高精度DAC通常需要引入校准。

2.3 DAC的速度

基于电荷定标结构的DAC的速度主要与电容充放电速度的快慢有关。DAC的建立过程是输出电压对阶跃输入的响应:Vout(t)=Vstep(1-e-t/τ)

这里的Vstep是各位的台阶电压,大小为Vref/2i。其中建立误差为Vstep×e-t/τ,大小要小于0.5LSB。则(N+1-i)ln2

因此减小时间常数可以提高处理速度,做法是减小电容大小与开关的导通电阻。单纯的NMOS或PMOS在导通电阻参数上并不能满足要求。通常采用CMOS传输门,保证分别在低电压与高电压下的低导通电阻。另外开关还有两个主要的非理想效应:电荷注入和时钟馈通。消除电荷注入的方法有:增加由CLK虚拟开关、NMOS与PMOS的互补开关以及采用差动电路。时钟馈通效应可以采用差分时钟馈通衰减技术(DCFA-Differential Clock Feed-through Attenuation)。通过电容与运放对电压进行保持,衰减后的时钟馈通由传统结构的12.0 μA降到了0.27 μA。另外增加冗余或采用双速时钟可以加快DAC速度。

2.4 DAC功耗

DAC的功耗主要为转换过程中对电容充放电时的功耗。以2位CDAC为例。

最高位是1时,Vin>Vref,MSB-1位由接地转为接Vref,称为向上偏转。这时功耗为

MSB-1位电容功耗:

Ec=2CVref[(-Vin+1/2Vref)-(-Vin+3/4Vref-Vref)]=3/2V2ref

MSB电容功耗:

E2C=4CVref[(-Vin+1/2Vref-Vref)-(-Vin+3/4Vref-Vref)]=-CV2ref

最高位是0时,Vin<Vref,MSB位由Vref转为接地,MSB-1由接地转为接Vref。成为向下偏转。这时的功耗为MSB-1位电容

Ec=2CVref[(-Vin+1/2Vref)-(-Vin+1/4Vref-Vref)]=5/2CV2ref

因为第一步的充电电荷,在第二步中被接地释放掉了。所以向下偏转过程功耗比较大。同理依次得出之后的各个转换过程的能耗,在图2中标出。

最近几年对低功耗领域的探索,获得了很多成果。其中一种为的转换模式。其采用了差分结构,可有效减小共模噪声、偶次谐波失真以及失配电压的影响。电容的转换是基于VCM向Vref和GND转换的,电容充放电电荷数减少。功耗在传统分段结构基础上节省了80%[7]。并且开关数量由原来的12n-2减小到6n-4。具体转换步骤如图4所示。

为解决向下偏转功耗过高这个问题,可以采用一种新的转换方式:monotonic转换方式[8]。总的CDAC功耗为传统二进制的19%。Monotonic转换采用顶极板采样,将本来需要的2N个开关减少到2个。具体的偏转波形如图5所示。

图4 Vcm-based转换模式Fig.4 Vcm-based conversion

此外巧妙利用与地的转接可以实现对N位转化,只需要进行N-2次转换(tri-level)[9]。功耗中减小了MSB、MSB-1位电容的功耗。面积也只为普通二进制电容的4.7%。另外还有通过在DAC输出加电阻分压的方式进行每次两位转换的方法。

图5 传统与monotonic偏转波形比较Fig.5 Comparison of traditional and monotonic switching procedure

3 SAR-ADC中的比较器

比较器是ADC中重要的一个模块。对低功耗SAR-ADC来说,可以采用动态的预防大锁存比较器。或者基于时域(time-domain)的比较器[10],用压控延时串产生时间信号,并通过鉴相器比较大小。也可以采用两个动态比较器,噪声小、功耗高的比较器只用作后几位精细比较。保证精度的同时控制功耗。

要提高比较器的速度,通常的方式是降低响应时间。也要避免亚稳态现象(meta-stability)[11]。可以采用多级比较器或故意失调技术。通过一个固定失调(4LSB)的比较器提高微小输入信号时的速度,且误码率降低到1.9×10-12[12]。另外增加一个亚稳态检查器MD(meta-stable detector)可实现比较区域三级划分。避免亚稳态的同时,还可以提高SNR(中区域占50%下,SNR提高6 dB)[13]。

对高精度的要求则需要处理失调与噪声。通过对晶体管参数的合理调整,失调电压可以减少50%以上[14]。消除失调的方法还有输入失调存储(IOS)、输出失调存储(OOS)、调整输入管阈值电压(失调降到0.25LSB[15])、输入管漏源间并联电阻(失调降到50 μV[16])等。对锁存结构来说,还要考虑回踢噪声的消除。可以将锁存输出节点与输入管的漏极隔离,或在左右支路间添加中和电容。

4 校准方法

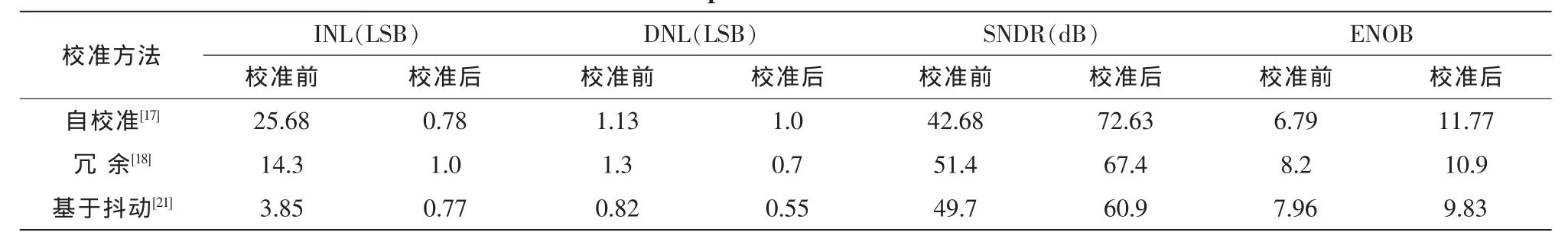

由于非线性以及失调的影响,对于SAR ADC在要求精度达到12bit时,通常需要加入校准电路才能满足要求。然而每种校准方法几乎都需要在模拟电路上做相应的改变,所以特定的结构搭配相应的校准。下面介绍几种典型的校准方式。

4.1 自校准电路

Hae-Seung Lee首先提出的自校准电路,基本原理为在采样前对电容阵列进行匹配校准,产生误差编码。然后在输入或输出上加上误差码进行校准[17]。这种先测量误差,再校准的方式,也称为前台校准。优点是易于实现,校准速度快。缺点是不能实时调整误差。文献[18]则通过在电容上并列比单位电容更小的电容来校准失配。这也在一定程度上弥补了比较器的输入失调电压。缺点是更小电容没有进行匹配测试,且不能完全校准失调。

4.2 冗余(redundancy)校准

所谓冗余,是指在DAC转换过程中增加一位转换,逼近区域重叠部分为冗余,是一种DAC直接校准的技术[19]。冗余的采用是来减少DAC不完全建立产生的误差。以4位DAC为例,在传统权重中增加冗余电容4C[20],权重为8、4、4、2、1。具体的建立步骤如图6所示。

图6 建立过程Fig.6 DAC setup

理想建立过程中,可以看到DAC在每个时钟周期都达到了相应的参考电压水平。在不完全建立过程中,由于第一位的DAC输出没有达到,使得下个周期进入了错误的比较范围。即使之后每一步都能完全建立,最后的输出编码仍偏离正常的值。图5-1(c)因为增加了一个冗余电容4c,所以转换次数增加到5次,但最后逼近到正确范围。输出编码增加到5位,经过转码可以转换为正常4位编码。

4.3 基于抖动(dither)的校准电路

基于抖动校准ADC的技术在之前的流水线型ADC应用较多,但是用在SAR-ADC上是在2012年才实现的[21]。方法是在输入端加入一个伪随机码(抖动噪声),输出端利用数字电路进行噪声消除。这种信号采样同时进行误差测量与校准的方式也称为后台校准。其基本原理如图7所示。

图7 抖动校准的基本结构Fig.7 Structure of dither calibration

整个过程实质上是用抖动频谱来平均其他噪声频谱。具体的抖动信号,也分为宽带小信号、宽带大信号、窄带大信号等。通常宽带抖动需要额外的减法结构去除,而窄带抖动信号可以通过数字滤波实现。表1列出了以上3种校准方式的效果。

表1 3种校准技术对比Tab.1 Compare of calibration methods

5 结束语

SAR-ADC的主要特点是低功耗,并且在速度与精度方面有很高的可塑性,综合性能具有优势。SAR-ADC的功耗主要由其中的DAC和比较器决定,首先可以从降低每次逼近的功耗与逼近次数两个方面来提高DAC的速度,从而减少SAR-ADC的转换功耗。另外,在低电压低功耗条件下采用基于时域的比较器,可以减小比较器的电压依赖与功耗。为降低电路复杂性、提高系统的抗干扰能力,SAR-ADC的校准方法多采用数字电路来实现。论文通过对SAR-ADC的分析与回顾,结合实际需要,总结得出SAR-ADC将继续向更高速度、更高精度、更低功耗方向发展。

[1] LIU Chun-cheng,SOON-JYH C,HUANG Guan-ying,et al.A 1V 11fJ/conversion-step 10bit 10MS/s asynchronous SAR ADC in 0.18um CMOS[Z].2010:241-242.

[2] CHENG-HSUN H,SOON-JYH C,HUANG Guan-ying,et al.A 3.9-fJ/c.-s.0.5-V 10-bit 100-kS/s low power SAR ADC with time-based fixed window[Z].2014:2234-2345.

[3] Akita I,Furuta M,Matsuno J,et al.A 7-bit 1.5-GS/s timeinterleaved SAR ADC with dynamic track-and-hold amplifier[Z].2011:293-296.

[4] DAI Guo-xian,CHEN Chi-xiao,MA Shun-li,et al.A 400-MS/s 8-b 2-b/cycle SAR ADC with shared interpolator and alternative comparators[Z].2014:2236-2365.

[5] 许军.原子层淀积高k介质MIM电容性能研究[D].上海:复旦大学,2009.

[6] Tripathi V,Murmann B.Mismatch characterization of small metal fringe capacitors[J].Circuits and Systems I:Regular Papers,IEEE Transactions on,2014,61(8):2236-2242.

[7] Anon.A split-capacitor vcm-based capacitor-switching scheme for low-power SAR ADCs[Z].2013:2014-2017.

[8] ZHU Zhang-ming,YU Xiao,SONG Xiao-li.Vcm-based monotonic capacitor switching scheme for SAR ADC[J].Electronics Letters,2013,49(5):327-329.

[9] YUAN C,LAMY.Low-energy and area-efficient tri-level switching scheme for SAR ADC[J].Electronics Letters,2012,48(9):482-483.

[10] YAN-JIUN C,CHIH-CHENG H.A 0.4V 2.02fJ/conversionstep 10-bit hybrid SAR ADC with time-domain quantizer in 90nm CMOS[Z].2014:1-2.

[11] Figueiredo P M.Comparator metastability in the presence of noise[J].Circuits and Systems I:Regular Papers,IEEE Transactions on,2013,60(5):1286-1299.

[12] Kang J J,Flynn MP.A 12b 11MS/s successive approximation ADC with two comparators in 0.13μ;m CMOS[Z].2009:240-241.

[13] Shikata A,Sekimoto R,Kuroda T,et al.A 0.5 V 1.1 MS/sec 6.3 fJ/Conversion-Step SAR-ADC with Tri-Level comparator in 40 NMCMOS[J].Solid-State Circuits,IEEE Journal of,2012,47(4):1022-1030.

[14] GUO Yong-heng,CAI Wei,LU Tie-jun,et al.A novel 1GSPS low offset comparator for high speed ADC[Z].2009:1125-1251.

[15] Anon.A 10-b 50-MS/s 820-uW SAR ADC With On-Chip Digital Calibration[J].Biomedical Circuits and Systems,IEEE Transactions on,2010,4(6):410-416,242.

[16] VAN DER PLAS G,DECOUTERE S,DONNAY S.A 0.16pJ/Conversion-Step 2.5mW 1.25GS/s 4b ADC in a 90nm digital CMOS process[Z].2006:2310.

[17] Anon.A 1.35 GS/s,10 b,175 MW Time-Interleaved AD converter in 0.13um CMOS[J].Solid-State Circuits,IEEE Journal of,2008,43(4):778-786.

[18] Aghaie S,Mueller J H,Wunderlich R,et al.Design of a lowpower calibratable charge-redistribution SAR ADC[Z].2014:1-4.

[19] Chang A H,HAE-SEUNG L,Boning D.A 12b 50MS/s 2.1mW SAR ADC with redundancy and digital background calibration[Z].2013:109-112.

[20] 吕伟.用于无线传感网络的逐次逼近型模数转换器研究与实现[D].合肥:中国科学技术大学,2014.

[21] LIU Wen-bo,HUANG Ping-li,CHIU Y.A 12-bit 50-MS/s 3.3-mW SAR ADC with background digital calibration[Z].2012:1-4.