DSOGI-PLL 算法在不平衡和畸变电网电压监测中的应用*

2015-03-26王科俊马晓伟

巩 冰,王科俊,马晓伟

(哈尔滨工程大学 自动化学院,黑龙江 哈尔滨150001)

0 引 言

在新能源发电系统中,为保证并网功率变换器与其他依赖于电网同步的电力电子设备能可靠运行,不能将电网电压当作幅值恒定的常量,需要不断地监测电网电压的幅值、频率与相位,以确保并网功率变换器与电网协调一致的工作。锁相环(phase-locked loop,PLL)可以自动跟踪输入信号的相位和频率,并输出相位同步信号。因此,在电网监测中,采用锁相技术对电网状态进行实时监测是目前实现并网功率变换器与电网同步普遍采用的方法。电网运行中可能存在各种故障,如电压跌落、电压不平衡、相位和频率突变、谐波等,PLL 必须不受影响,准确跟踪电压正序基频分量的相位与频率[1]。

PLL 分为硬件和软件两种形式。软件PLL 也叫柔性PLL,它可以克服硬件PLL 难以克服的难题,如直流零点漂移、器件饱和、必须初始化校准等。三相系统中常用的是同步参考坐标系软件锁相环(synchronous reference frame-PLL,SRF-PLL)算法[2]。在理想电压情况下,该PLL 能够可靠工作,但是当电网电压不平衡或发生畸变时,该PLL的输出就会受到影响,出现谐波,尤其是二次谐波。

本文提出了一种双二阶广义积分器的软件锁相环(dual second-order generalized integrator-PLL,DSOGI-PLL)算法。该PLL 通过构建二阶广义积分器(SOGI)来实现90°相角偏移,产生两相正交信号,完成对电网电压正序分量的提取。在SOGI 的基础上构建基于内模原理的自适应滤波器既可以快速实现90°相角偏移,又可以滤除高次谐波,实现在电网不平衡、含有谐波或电压畸变等情况下的准确锁相。

1 DSOGI-PLL 算法

1.1 基于SOGI 的正交发生器

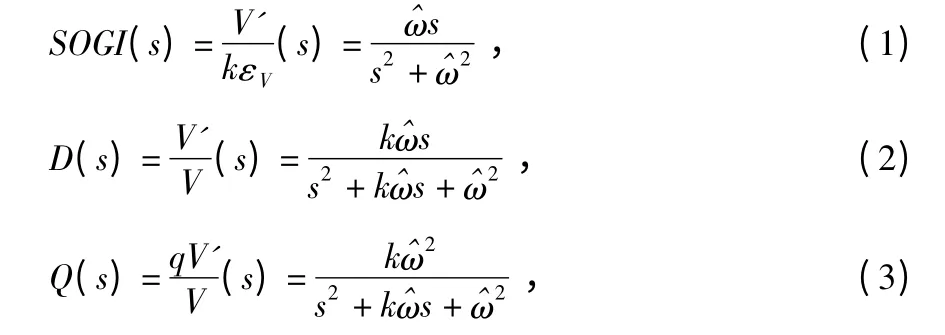

基于SOGI 的正交信号发生器(quadrant signal generator of SOGI,SOGI-QSG)如图1 所示,V'和qV'为输出的两正交信号,εV为输入V 和输出V'之间的误差信号。由图可得

由式(2)和式(3)不难看出,式(2)是一个带通滤波器,式(3)是一个低通滤波器,它们的滤波性能受参数k 的影响,而与频率无关。当k 值较小时,系统响应慢但滤波效果好,综合考虑响应速度和抗扰性能,选择对应二阶系统的阻尼系数

图1 SOGI-QSG 结构图Fig 1 Structure of SOGI-QSG

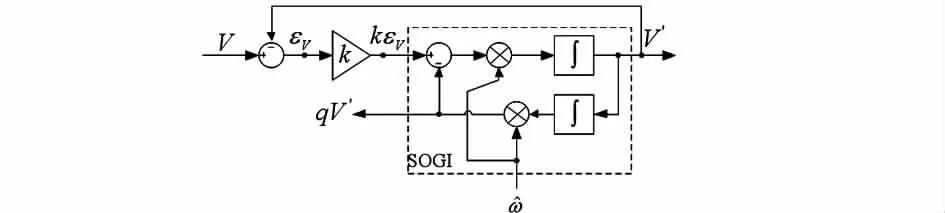

1.2 锁频环

带有锁频环(frequency-locked loop,FLL)的SOGI 如图2所示。FLL 的输出是SOGI 所需要的频率输入。FLL 本质上是一个积分器,作用是调节频率实现无静差。图中是归一化系数,ωff为前馈角频率,作用是加快暂态过程,这里,ωff=2π×50=314 rad/s。

图2 SOGI-FLL 结构图Fig 2 Structure of SOGI-FLL

1.3 DSOGI-PLL 算法

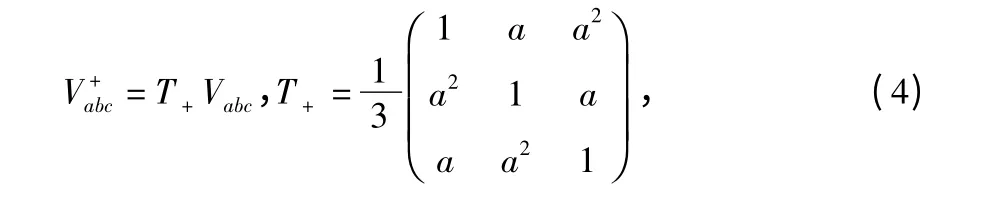

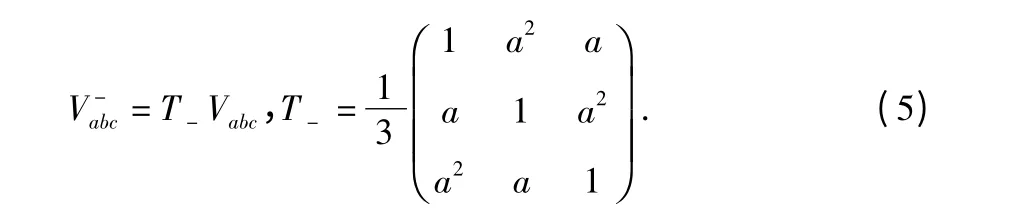

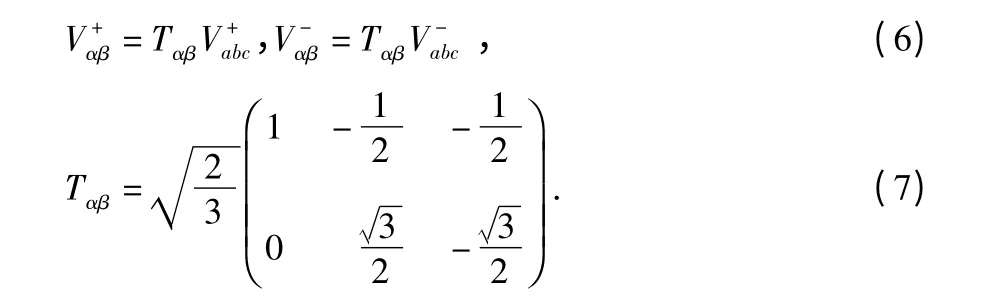

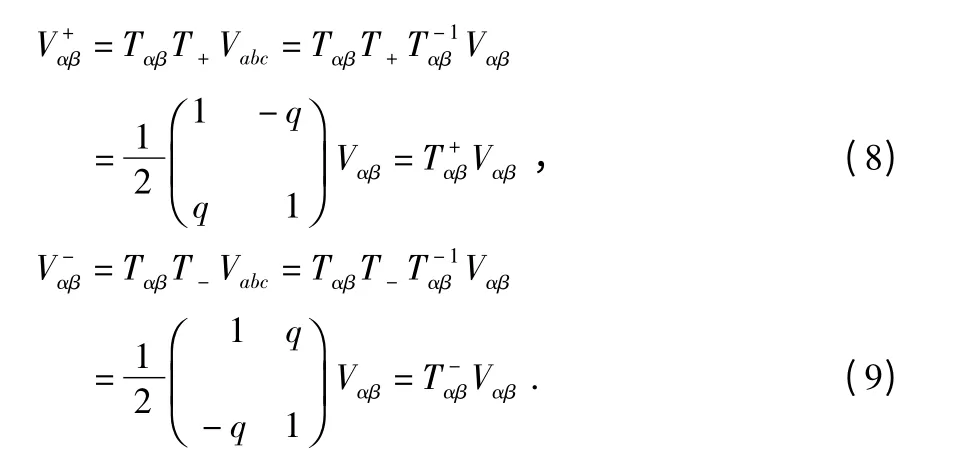

根据对称分量法,三相电网电压Vabc的正序分量和负序分量为

其中,算子a=ej2π/3。

采用Clarke 变换,将三相电网电压Vabc的正负序分量转换到两相静止坐标系αβ 下得

将式(4)和式(5)代入式(6)中得到

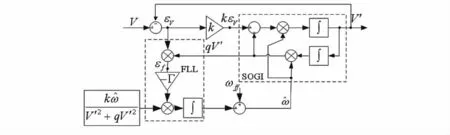

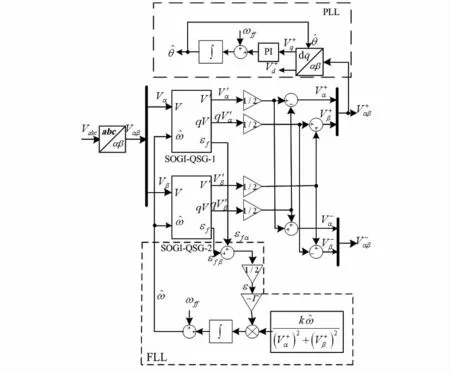

由式(8)、式(9)和图2 SOGI-FLL 的结构,可得到DSOGI-PLL 算法的结构图,如图3 所示。

图3 DSOGI-PLL 算法的结构图Fig 3 Structure of DSOGI-PLL algorithm

2 仿真验证

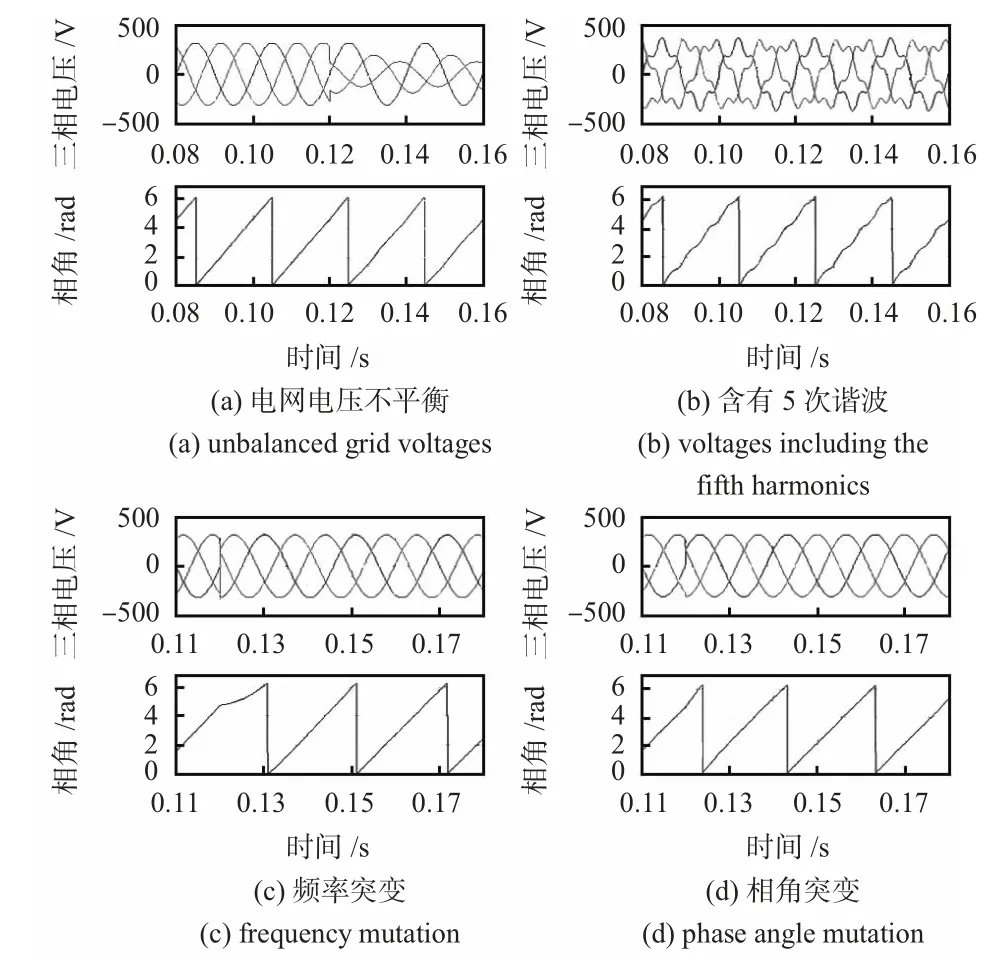

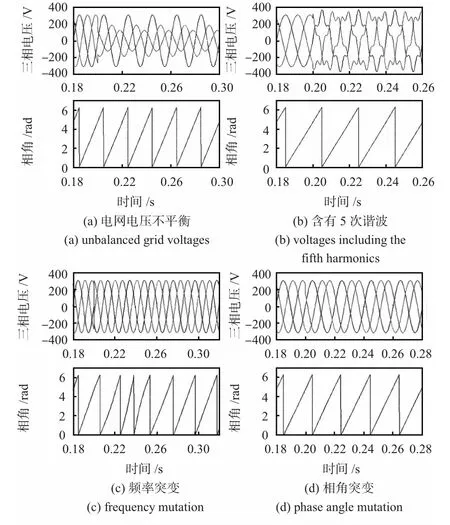

本文采用Matlab/Simulink 软件,分别在三相电压不对称、频率突变、相位突变、含有谐波等情况下对传统的SRFPLL 算法和本文所提出的DSOGI-PLL 算法进行了仿真。DSOGI-PLL 算法中的参数Γ=100。仿真结果如图4 和图5 所示。

图4 SRF-PLL 算法的仿真结果Fig 4 Simulation results of SRF-PLL algorithm

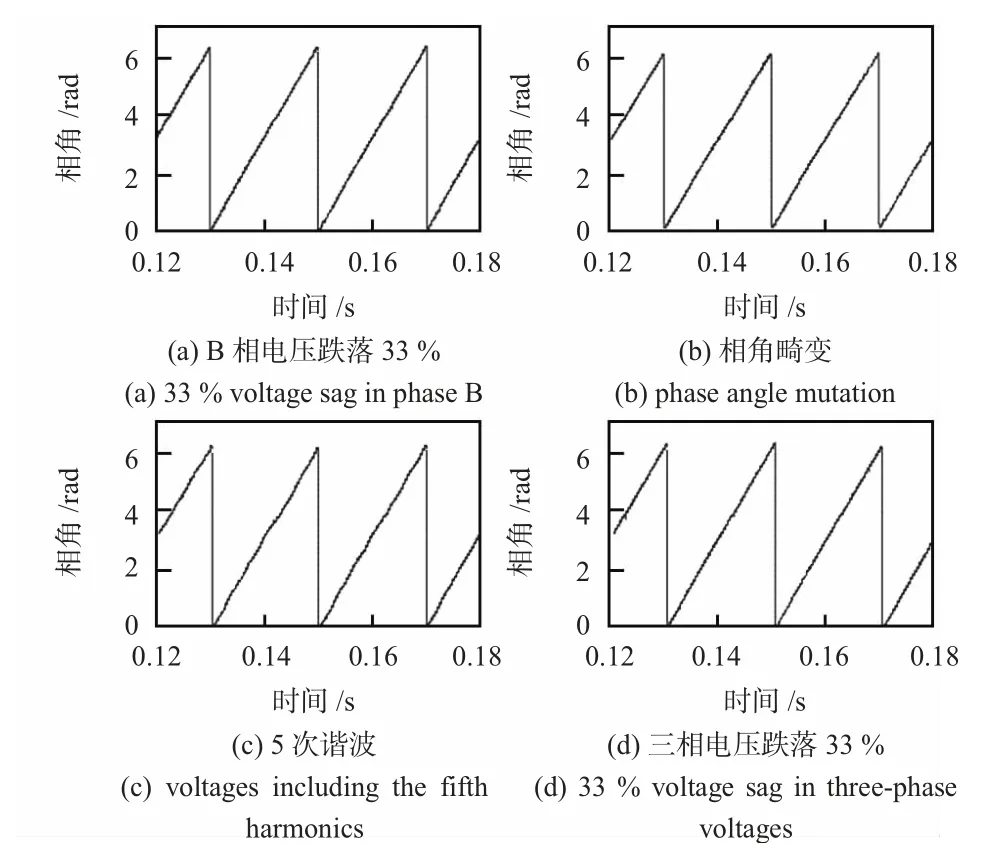

图5 DSOGI-PLL 算法的仿真结果Fig 5 Simulation results of DSOGI-PLL algorithm

从图4 中可以看出:SRF-PLL 算法在电网发生频率突变和相角突变的情况下,可以准确迅速地完成锁相,但在电网电压不对称和含有谐波的情况下,输出的锁相信号中也含有谐波,不能准确锁相。因为SRF-PLL 算法缺少对电网电压负序分量和高次谐波的滤除能力,使得用来提取相位信息的信号中含有谐波。而从图5 中看出:本文所提出的DSOGI-PLL 算法在电网不对称、频率和相角畸变和谐波情况下都能够准确实现相位锁相。证明引入FLL 后的DSOGI-PLL 算法结构对谐波有很强的抑制能力,可以获得良好的频率适应性。

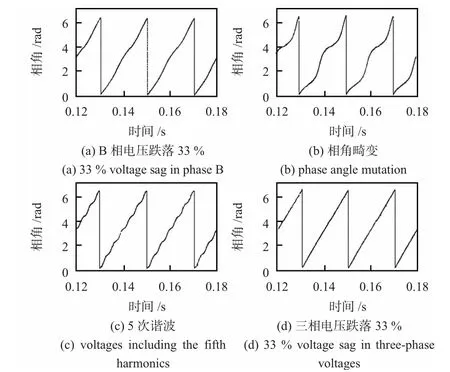

3 实验验证

本文以ARM Cortex-M3 内核的STM32F103RBT6 处理器为核心构建锁相环的硬件实验平台,并在三相电压不平衡、含有谐波和相角突变的情况下对传统的SRF-PLL 算法和本文提出的DSOGI-PLL 算法进行实验验证,实验结果如图6 和图7 所示。

图6 SRF-PLL 算法的实验结果Fig 6 Experimental results of SRF-PLL algorithm

图7 DSOGI-PLL 算法的实验结果Fig 7 Experimental results of DSOGI-PLL algorithm

从图6 可以看出:在三相电压不平衡的条件下,SRFPLL 算法不能准确锁相,电压不平衡程度越高,其相角畸变程度越严重。当电网出现谐波时,SRF-PLL 算法对谐波抑制能力弱,相角输出信号中出现明显的波动。图7 表明:DSOGI-PLL 算法可以避免电网电压中负序分量对锁相的影响,对谐波有很强的抑制能力,在谐波含量较大的环境中仍能准确锁相,这与理论分析和仿真验证的结果相一致。

4 结 论

本文提出了一种在电网电压不平衡和畸变情况下仍能准确工作的DSOGI-PLL 算法。通过仿真和实验结果证明:与常用的SRF-PLL 算法相比,该方法正确有效,能够实现频率自适应,具有较强的谐波抑制能力。

[1] 张 兴,张崇巍.PWM 整流器及其控制[M].北京:机械工业出版社,2012.

[2] Kaura V,Blasco V.Operation of a phase-locked loop system under distorted utility conditions[J].IEEE Trans on Industrial Application,1997,33(1):58-63.

[3] Best Roland E.锁相环设计、仿真与应用[M].北京:清华大学出版社,2007.

[4] 李彦栋.动态电压恢复器锁相及控制方法的研究[D].西安:西安交通大学,2004.

[5] 林百娟.三相电压不平衡条件下锁相环的设计与实现[D].呼和浩特:内蒙古工业大学,2009.

[6] Robles E,Ceballos S,Pou J,et al.Variable-frequency grid-sequence detector based on a quasi-ideal low-pass filter stage and a phase-locked loop[J].IEEE Trans on Power Electronics,2010,25(10):2552-2563.

[7] Rodriguez P,Pou J,Bergas J,et al.Decoupled double synchronous reference frame PLL for power converters control[J].IEEE Trans on Power Electronics,2007,22(2):584-592.