基于PowerPC+FPGA构架的综合信息处理系统设计

2015-03-23刘青

刘 青

(中国电子科技集团公司第20研究所,西安 710068)

基于PowerPC+FPGA构架的综合信息处理系统设计

刘 青

(中国电子科技集团公司第20研究所,西安 710068)

提出了一种基于PowerPC+现场可编程门阵列(FPGA)构架的综合信息处理系统设计方案,以PowerPc和FPGA为核心处理模块,详细阐述了系统的硬件设计思想及实现。

PowerPC;高速传输;动态加载;Vxworks

0 引 言

近几十年来,随着软件无线电概念[1]的不断发展,军用航空电子系统已经改变了传统的、将不断出现的功能设备逐渐堆积式的向前发展模式,而是沿着网络化、综合化、模块化、通用化和智能化的方向发展。通过可重构现场应用软件,能够实现动态修改通信数据链系统功能。采用通用硬件以及不同的软件配置的组合,实现从单一通信数据链系统到综合化通信数据链系统的发展。

软件无线电的核心内容之一是综合化的信息处理功能,它包括高速实时信号处理功能、高速数据传输功能、多任务数据处理能力和软件动态重构功能。随着科学技术的高速发展,采用并行处理构架的FPGA逐步取代数字信号处理器(DSP)应用于实时的信号处理算法。而随着嵌入式的发展,在网络层和通信协议层具有更大灵活度和完整度的POWERPC,伴随着丰富的通信接口也被更广泛地应用于军用航空电子系统中,用于多任务数据处理和高速链路信息传输。

本文设计了一种基于PowerPC+FPGA构架的综合信息处理系统,用于完成多种通信数据链的综合应用和动态处理。

1 系统结构

本处理系统采用PowerPC+FPGA构架作为系统的核心处理模块。PowerPC通过Local Bus与FPGA相连,并通过RapidIO交换芯片和以太网交换芯片与外部高速通信接口相连,完成系统的高速信息传输和多任务数据处理。FPGA作为逻辑构建单元主要完成接口时序控制和高速实时信号处理算法等功能。复杂可编程逻辑器件(CPLD)主要完成模块的电源管理、复位管理、时钟综合器管理等功能。系统具有丰富的高速外部接口,包括有高速低电压差分信号(LVDS)接口,高速G比特收发器(GTX)接口,10 M、100 M、1 000 M自适应以太网接口,RapidIO接口等。系统的构成框图如图1所示。

图1 系统构成框图

2 硬件设计

2.1 PowerPC部分

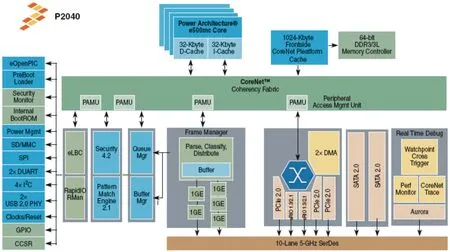

PowerPC采用飞思卡尔公司的P2040四核处理器,型号为P2040NXN7MMC,每个处理器包括4个e500mc内核,内核最高主频可达1.2 GHz(考虑到功耗问题,实际使用为1 GHz),操作系统使用VxWorks 6.9,可以实现通过网口在线下载并烧写操作系统和应用程序,并通过以太网固化和更新PowerPC和FPGA程序。PowerPC的功能框图如图2所示。

图2 P2040处理器功能框图几何尺寸(单位:mm)

P2040集成了一个DDR3/3L 同步动态随机存储器(SDRAM)接口,位宽支持64 bit/72 bit,数据率最高支持1 200 MT/s;拥有5个以太网控制器,支持10 M/100 M/1 000 M;2个串行RapidIO接口(SRIO)控制器,支持×1,×2,×4模式,速率支持2.5 Gbps/3.125 Gbps/5.0 Gbps/;1个eLocal bus接口,位宽16位,时钟频率最高66 MHz。

2.2 PowerPC内存扩展

P2040内部集成了DDR3 SDRAM,可以直接进行内存阵列连接和控制,容量支持最大为8 GB。

本处理系统设计中P2040外挂2 GB字节DDR3 SDRAM用于数据存储功能,选用4片MT41J256M16HA-125 IT(DDR3-1600)和1片MT41J512M8HA-125IT的DDR3存储器颗粒拼接成72位宽,含8 bit 错误检查和纠正校验。

2.3 NOR FLASH

NOR FLASH用来存储PowerPC自启动时的引导程序。PowerPC通过Localbus实现外挂NOR flash。由于Localbus的数据地址线复用,需要外部锁存器电路将数据线与地址线分离。本处理系统通过CPLD实现数据线与地址线分离,PowerPC间接连接到NOR FLASH,可以实现PowerPC对NOR flash 的读写操作,完成PPC最小程序引导加载。

本处理系统NOR FLASH芯片选用SPANSION公司的S29GL01GP,容量128 MByte,数据位宽32 bit。

2.4 eMMC存储器

PowerPC一般外接NAND FLASH,用于存储用户程序、数据和日志,FPGA程序等。但NAND FLASH的纠错要求与P2040自带的NAND FLASH控制器不匹配,后期使用会造成数据可靠性降低。因此,本处理系统采用嵌入式多媒体卡(eMMC)存储器作为存储数据的介质。P2040自带eSDHC控制器接口,该接口支持MMC协议。选用MICRON公司的型号为MTFC8GLVEA-4M IT的eMMC存储器芯片,该芯片的特点是在1个封装内集成了NAND FLASH存储颗粒和1个多媒体卡(MMC)控制器,通过标准的eMMC接口与外部通信。

2.5 以太网交换部分

本处理系统采用BROADCOM公司的BCM5396IFBG千兆以太网交换芯片,用于以太网数据交换。BCM5396支持全双工10 M/100 M/1 000 M自适应以太网协议,遵循IEEE802.3,802.3u,802.3ab和802.3x标准,有16个1.25G-SerDes/SGMII接口可以连接到外部的PHYs上。本处理系统根据需求共使用5路10 M/100 M/1 000 M自适应信号对外输出,其中一路与PowerPC相连,另一路通过网线与显控设备相连,其余3路用于背板的高速数据传输。

BCM5396的配置接口SPI接到CPLD[2]芯片上,PowerPC可通过CPLD访问此SPI接口,完成配置交换芯片的功能。以太网交换部分功能如图3所示。

图3 以太网交换功能框图

2.6 RapidIO交换部分设计

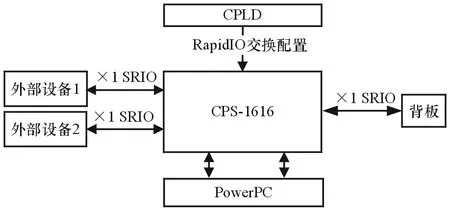

本处理系统采用RapidIO交换芯片实现多路RapidIO数据的交换传输,RapidIO交换芯片型号为IDT公司的CPS-1616,该芯片基于RapidIO 2.1规范,共有16路串行通道,其中4个端口为1组,每组可以单独配置传输速率,可灵活配置为4×4,8×2,16×1的端口工作方式,其中每组端口可单独配置为1×4,2×2,4×1的工作方式,可以根据外部接口需求进行灵活配置。

本处理系统根据需求通过CPLD将RapidIO交换芯片配置成3路×1模式和2路×2模式,分别与背板、外部设备和PowerPC相连。RapidIO交换部分原理如图4所示。

图4 RapidIO交换部分原理框图

2.7 FPGA设计

本处理系统的FPGA选用XILINX公司Kintex7系列FPGA芯片XC7K325T-2FFG900I,主要用于高速数据的收发时序控制,不同通信数据链系统的信号处理算法实现以及与PowerPC的数据传递。该型号FPGA拥有326 080个逻辑单元,840个DSP模块,块RAM容量为16 020 kb,10个时钟单元,16个GTX收发模块,以及1个支持八通道PCIe2.0协议的硬件PCIe模块。

FPGA采用16位Slave SelectMap方式加载,配置接口引出至CPLD[2]。系统显控设备可实时根据实际需求,通过高速以太网口将不同通信数据链系统信号处理算法的FPGA程序传输到eMMC存储器中,然后PowerPC读出eMMC存储器中的FPGA程序,并通过Local bus访问CPLD中构建的FPGA配置接口逻辑,间接地将FPGA程序写入FPGA芯片中,完成信号处理算法的动态加载。FPGA的动态加载过程如图5所示。

图5 FPGA程序动态加载示意图

2.8 CPLD设计

本处理系统选用ALTERA公司MAXII系列的型号为EPM2210F324I5N的CPLD,用于实现系统的电源管理、复位管理、时钟管理、FPGA程序动态加载控制和NOR FLASH存储器控制等功能。

CPLD负责完成电源芯片的管理和各个模块的上电控制,系统上电时,CPLD首先完成频率综合器的配置,确认时钟有效后,对交换芯片进行配置,发送整板复位信号给PowerPC和交换芯片。PowerPC复位后进入正常的BOOT流程,从NOR FLASH中搬移引导程序并运行,再从eMMC存储器中搬移用户程序并运行。PowerPC加载完成后,从eMMC存储器中读取FPGA程序,并通过CPLD连接的FPGA配置端口,将配置程序写入FPGA芯片中,FPGA逻辑运行后,整个系统进入正常工作模式。

3 软件设计

本处理系统设计的操作系统采用WindRiver公司的VxWorks6.9版本。软件设计的主要工作是VxWorks操作系统BSP的设计实现[3]。板级支持包(BSP)是介于底层硬件和上层软件之间的底层软件开发包,其作用类似于磁盘操作系统(DOS)的基本输入输出系统(BIOS)。它的主要功能为屏蔽硬件,提供操作系统的驱动及硬件驱动。具体功能包括:单板硬件初始化,主要是CPU 的初始化,为整个软件系统提供底层硬件支持,为操作系统提供设备驱动程序和系统中断服务程序;定制操作系统的功能,为软件系统提供一个实时多任务的运行环境。初始化操作系统为操作系统的正常运行做好准备。WindRiver公司在集成开发环境WorkBench中提供了许多典型设计的BSP软件包,设计人员只需要在这些BSP上进行针对修改即可。根据本处理系统设计需求,驱动程序设计包括NOR Flash驱动、eMMC存储器驱动、以太网接口驱动和RapidIO接口驱动等,因不是本文讨论重点,不再一一赘述。

4 结束语

本文设计了一种基于PowerPC+FPGA构架的综合信息处理系统,通过可重构现场应用软件,实现动态修改通信数据链系统功能,使原来的单通道通信数据链系统变为适应不同信道要求的综合通信数据链系统。

[1] 杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[2] 陈雪峰,尹剑峰,贾敬乐.基于PowerPC的FPGA远程配置设计实现[M].计算机与数字工程,2013,41(3):437-439.

[3] 孔祥营,柏桂枝.嵌入式实时操作系统VxWorks及其开发环境Tornado[M].北京:中国电力出版社,2002.

Design of Integrated Information Processing System Based on PowerPC and FPGA Framework

LIU Qing

(The 20th Research Institute of CETC,Xi'an 710068,China)

This paper presents a design project of integrated information processing system based on PowerPC and field-programmable gate array (FPGA) framework,which takes the PowerPC and FPGA as central processing modules,expatiates the hardware design idea and realization of the system in detail.

PowerPC;high-speed transmitting;dynamic loading;Vxworks

2015-03-16

TN919

A

CN32-1413(2015)02-0117-04

10.16426/j.cnki.jcdzdk.2015.02.030