基于FPGA的高速并行数据传输系统*

2015-03-14赵亚范

赵亚范 王 坤 杨 帆 毕 涛

(1.海军航空工程学院基础实验部 烟台 264001)(2.海军航空工程学院基础部 烟台 264001)

基于FPGA的高速并行数据传输系统*

赵亚范1王 坤2杨 帆1毕 涛1

(1.海军航空工程学院基础实验部 烟台 264001)(2.海军航空工程学院基础部 烟台 264001)

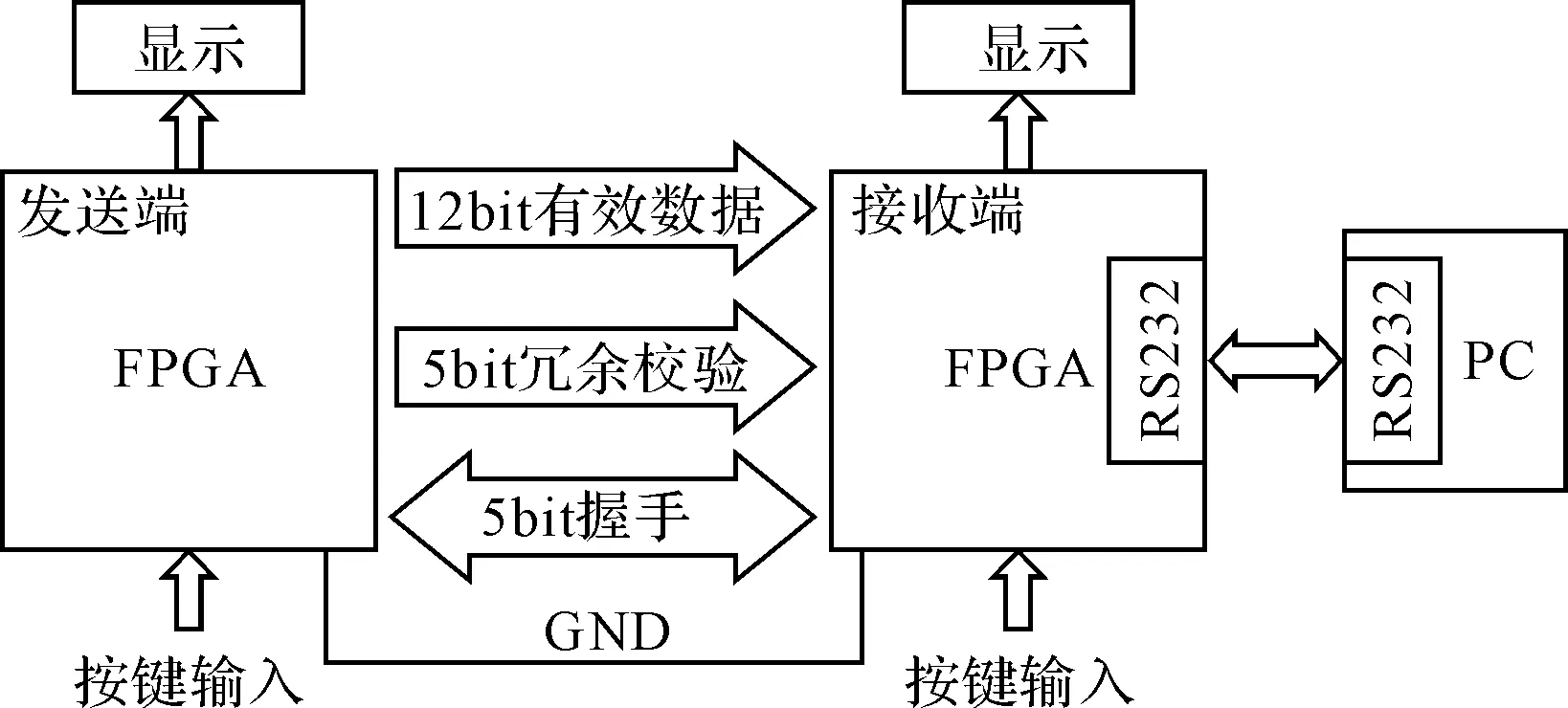

该系统以FPGA为核心,通过两个彼此独立的FPGA核心板构成高速并行数据传输系统的发送端和接收端。传输协议采用12bit有效数据带宽、5位循环冗余码进行校验编码(CRC),总线传输速率可达24Mbps以上。接收端成功接收完数据后可通过液晶屏显示数据内容,通过RS232总线上传至PC机进行分析,传输速率9600bps。传输过程中通过核心板上的LED指示灯指示传输线路状态。整个系统模块化程度好、集成度高,充分发挥单片机灵活实用的特点和运算速度快的优势。

FPGA; 校验编码; 并行传输; RS232

Class Number TP274.2

1 引言

数据传输系统是硬件和软件结合在一起的产物,在很多领域都有着广泛的应用,随着通信网络的不断发展,传统的数据传输系统传输速率低,在传输的过程中不能校验编码是否正确,已经不能适应数据传输业务的发展[1]。本文介绍了一种基于FPGA为核心板的高速数据传输系统,可进行并行通信,具有传输速率高,误码率低的特点。

2 总体方案设计

高速并行数据传输系统主要包括发送端、接收端、RS232接口、数据总线以及相应的输入显示设备组成。发送端、接收端采用Cyclone EP1C6Q240c8N芯片作为主芯片,通过按键可以进行通信数据设置和通信过程控制。发送端通过数码管和LED指示灯显示相关的发送数据和通信状态,接收端通过LCD和LED指示灯进行相关显示[2]。系统构成框图如图1所示。

图1 系统构成总体框图

发送端和接收端通过22根排线连接,其中12bit有效数据位,5bit冗余校验位,5根握手协议信号线,传输数据时,发送端对12bit有效数据进行编码,通过握手信号询问接收端,接收端接收到握手信号后反馈给发送端允许发送;接收端接收完一组数据(12bit)后进行循环冗余解码,并将解码情况告知发送端,若错误则发送端重发[3]。

在一组数据的接收过程中,如果接收端连续10次解码错误,则启动导线故障检测逻辑,分析接收到的12bit数据,并分析出导线故障,如两根导线短接、一根导线断接、或者某根导线恒为高或低。并将测试结果通过显示设备显示并报警。

3 硬件电路详细设计与理论分析

主控模块主要包括电源转换模块、FPGA芯片、4位共阳极数码管、LED、按键开关、TG12864液晶显示屏、MAX232芯片以及外围的电阻电容等元件[4]。

图2 通信系统详细电路连接图

5980个逻辑单元(LE)和92Kbit的片上RAM,有185个用户I/O口,非常适合用于并行数据传输,晶振采用48Mhz。在数据通信时,FPGA1可以发送内置ROM文件给FPGA2,也可以通过按键设定随机值进行发送,以检测通信效果。FPGA2接收到数据后存储至RAM,并可通过LCD12864显示,或者通过232总线发送至电脑[5~6]。

连接线hsend、hrecv、dfinishi、error、clk_tx构成握手总线,其中hsend由FPGA1发送,为高表示告知FPGA2准备接收FPGA1发送的数据;hrecv由FPGA2发送至FPGA1,用于答复FPGA1可以发送数据,dfinishi由FPGA2发送,用于告知解码成功(接收成功),error由FPGA2发送,用于告知解码错误(接收失败),请求重发[7]。

TG12864是汉字图形点阵液晶显示模块,可显示汉字及图形,内置8192个中文汉字、128个字符及64*256点阵显示RAM,完全可以满足接收端对于数据显示的要求。设计时采用8位并行通信接口与FPGA进行通信。

电源模块采用LM317电压变化模块,输入电压+5V,输出为+3.3V和+1.5V。其中1.5V电压主要是FPGA内置PLL电路需要的供电电压。

4 软件设计与分析

软件开发环境采用ALtera公司的QuartusⅡ 11环境,接收端和发送端分别进行独立设计。发送端要实现的功能有:按键读取、数码管显示、数据产生读取、数据编码、数据发送控制以及ROM存储等[8]。在QuartusⅡ开发环境下采用Verilog HDL作为编程语言,将上述功能梳理为crc5模块和crc5_test模块,如图3所示。

图3 发送端程序模块

crc5模块采用5位冗余码进行编码,生成多项式设为G(x)=x^5+x^4+x^2+1,用于实现12bit的有效数据的编码和发送,crc5_test用于手动产生12bit发送数据,并显示crc5模块计算得出的5bit校验码。

接收端要实现的功能主要包括接收数据、解码、传输状态判断、LCD显示、232通信等功能。功能模块图如图4所示。

当接收端接收到hsend信号时,将hrecv信号置高,表示可以进行数据通信。接收完毕后,接收端对数据进行解码与判断,如果解码正确,则将dfinish置高,高速发送端发送正确;如果解码错误,则高速发送端解码错误,发送端重发数据[9~10]。具体的通信时序图如图5所示。

图4 接收端功能图

图5 通信时序图

5 系统功能测试

为了验证本系统的可靠性,对本系统的误码率和传输速率进行了测试。

表1 误码率测试数据

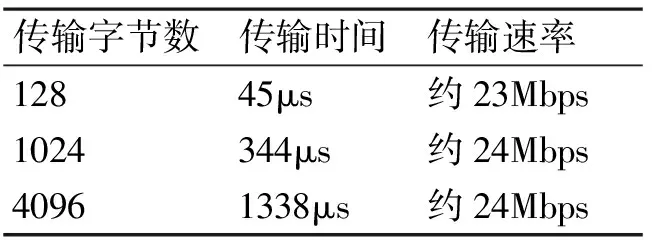

表2 传输速度测试数据

由表1可以看出,传输系统的误码率可控制在0.05%以下,由表2可以看出,系统的传输速度可达到24Mbps,实现了高速的特点。

6 结语

本系统着重于软件的设计,尽量提高计算速度和优化硬件设计,实现软硬件的合理设置。提高系统的整体功能和稳定性,系统以FPGA为核心器件,利用软件编程,实现数据传输,系统稳定,可靠性高,实现了高速并行数据传输功能。传输高效、误码率低、传输距离较长,当导线出现问题时,接收器能自行报警。数据传输的结果显示明了,便于分析。接收器自行报警后接收端能实现数据纠错功能,传输速度达到24Mbps,系统能够自行分析数据传输的误码率和传输效率。具有实际的应用前景。

[1] 丁瑞卿,孙毅刚,张红颖.基于DSP的USB数据传输系统设计[J].现代电子技术,2009(18):25-27.

[2] 林浩杰.基于FPGA和USB数据传输电路的设计[J].国外电子测量技术,2008,27(3):50-51.

[3] 李丽军,王代华,祖静.基于CC1100的无线数据传输系统设计[J].2007,26(12):12-13.

[4] 焦艳,刘勇智.基于FPGA多通道通用总线数据传输系统的设计[J].空军工程大学学报(自然科学版),2006,7(3):41-42.

[5] 罗蔚,方康羚.基于C8051F02X的无线数据传输系统[J].现代电子技术,2009(9):59-61.

[6] 许佳龙,张一闻,刘建平.基于TMS320C6713的USB数据传输系统设计[J].现代电子技术,2011,34(22):80-82.

[7] 吴昊,严胜刚,薛双喜.基于W5300的以太网数据传输系统的设计与实现[J].电子设计工程,2012,20(9):93-94.

[8] 轩志伟,轩春青,张志杰,等.基于ARM+WiFi无线数据传输系统的设计[J].测控技术,2013,32(12):53-55.

[9] 王怀侠,王永,王首浩.基于DSP+FPGA数据传输系统的实现[J].电子测量技术,2013,36(11):100-101.

[10] 张杰,胡世安,龙子夜,等.基于GPRS的无线数据传输系统及其应用探讨[J].电子测量与仪器学报,2009(增刊):155-156.

High Speed Parallel Data Transmission System Based on FPGA

ZHAO Yafan1WANG Kun2YANG Fan1BI Tao1

(1. Department of Basic Experiment, Naval Aeronautical and Astronautical University, Yantai 264001) (2. Department of Basic, Naval Aeronautical and Astronautical University, Yantai 264001)

This system takes FPGA as the core, while the sender and the receiver of high-speed parallel data transmission system have been constituted by two independent FPGA core boards. Transfer protocol adopts 12 bit effective data bandwidth and five cyclic redundancy check code(CRC), and transmission rate of bus can reach more than 24 megabits per second. The receiver can be displayed panel data content by LCD after successfully receiving the data which is analyzed by uploading to the PC through the RS232 bus with the transmission rate 9600 BPS. The state of transmission lines is indicated through the LED indicator light on the core board in the process of transmission. The whole system with good modular degree and high integration plays full advantage of flexible and fast practical computing speed.

FPGA, check code, parellel data transmission, RS232

2015年3月5日,

2015年4月28日

赵亚范,女,工程师,研究方向:可编程逻辑器件。王坤,男,硕士研究生,讲师,研究方向:可编程逻辑器件。杨帆,男,工程师,研究方向:可编程逻辑器件。毕涛,男,工程师,研究方向:可编程逻辑器件。

TP274.2

10.3969/j.issn.1672-9730.2015.09.019