GPU像素引擎的设计与实现*

2015-03-14丁振青熊庭刚秦信刚

丁振青 熊庭刚 秦信刚

(武汉数字工程研究所 武汉 430205)

GPU像素引擎的设计与实现*

丁振青 熊庭刚 秦信刚

(武汉数字工程研究所 武汉 430205)

随着各种娱乐设备以及数据处理设备的普及,三维图形技术逐渐应用到各种领域。论文对于针对国内目前GPU中像素引擎研究的不足,设计了一种具有完整功能的像素引擎,能够完成alpha测试、模板测试、深度测试和alpha混合。采用Verilog HDL语言设计了各功能模块,并生成了各功能模块的内部电路图。最后对各个功能模块进行了功能仿真,并在开发验证平台上验证像素引擎的功能。

计算机图形学; 图形处理器; 像素引擎; 像素测试; Cache

Class Number TP301

1 引言

随着计算机软硬件突飞猛进的发展,数据处理的重点从声音转向图形[1],随着图形的复杂度越来越高,仅仅依靠软件算法来绘制图形大大加重了中央处理器(CPU)的负担,不仅显示效率低下,而且会影响整个系统的性能[2]。因此需要专用的硬件,图形处理器(GPU)来加速图形处理,从而解放CPU,提高系统性能。

GPU是现代信息系统中把复杂信息通过图形图像方式展现出来,并能够对图形图像信息进行高速处理的集成电路。随着处理能力的加强,图形处理器已被广泛应用于办公自动化、动画制作、视频加速[3~4]、3D游戏[5]和高性能计算[6]等民用领域,同时,在军队的武器装备中图形处理器也有巨大的用途。像素引擎是GPU的重要组成部分,直接影响着像素处理的速度和输出画质的质量,像素引擎的研究对于国产GPU的研制具有重要的意义。

像素引擎处在图形处理流水线的最后,负责剔除和渲染输出像素。像素引擎完成各种像素级的操作,通过alpha测试、深度测试、模板测试快速剔除不符合要求的像素,减轻图形管线负担,提升系统性能,通过对源像素进行适当的格式转化,使之与目标像素完成alpha混合最终将完整处理的像素写入显存。经过测试和混合后的像素进入显存,最终才能够在屏幕上显示一幅清晰、平滑的图像[7]。

查询了大量资料发现,在20世纪90年代国外关于像素引擎的研究处于一个高峰期[8~10],但随着研究的愈发成熟,近年来已经很少有这类的文章出现,因此可知在像素引擎的研究方面国外起步较早,研究已经比较完善。国内的GPU研究处于起步阶段,像素引擎研究则相对落后。研究成果大致分为两类,一类是采用国外的商用GPU IP,但是没有自主知识产权,且大都是嵌入式产品,不能够运行于通用操作系统。如华为、瑞芯微电子、全志、新岸线等公司都只是采用了集成进口商用嵌入式GPU IP的方案[11~12],有一定的图形处理能力。另外一类是自主研发的产品,不兼容通用操作系统、通用图形API,经像素引擎输出的图形性能也不及商用的嵌入式GPU IP,这都不能满足市场需求[13]。在国内的文章和研究报告中可以看到,上世纪90年代国外像素引擎研究的高潮阶段国内基本没有参与,到21世纪后才能在一些高校的文章中找到一些踪迹,但大多数都只是建立模型,没有实际产品出现。近年来随着国家的重视和集成电路产业的发展,国内在像素引擎方面的研究突飞猛进,取得了一定的成果,但是总体还处于起始阶段,和国外高性能GPU还有一定的差距。

2 像素引擎的工作原理与硬件实现

像素在被写入显存前还必须进行一系列的测试,当某项测试默认关闭时,该测试直接通过。若某个像素在一项测试中被排除,后面的测试则不需要执行。通过测试的像素在完成混合后才能被写入显存。完整的像素测试包括alpha测试、模板测试和深度测试。

本节依次探讨了像素引擎的这些主要功能,明确了主要流程,根据流程图设计RTL代码。并用Synopsys公司的Verdi软件进行仿真,并生成RTL级电路。

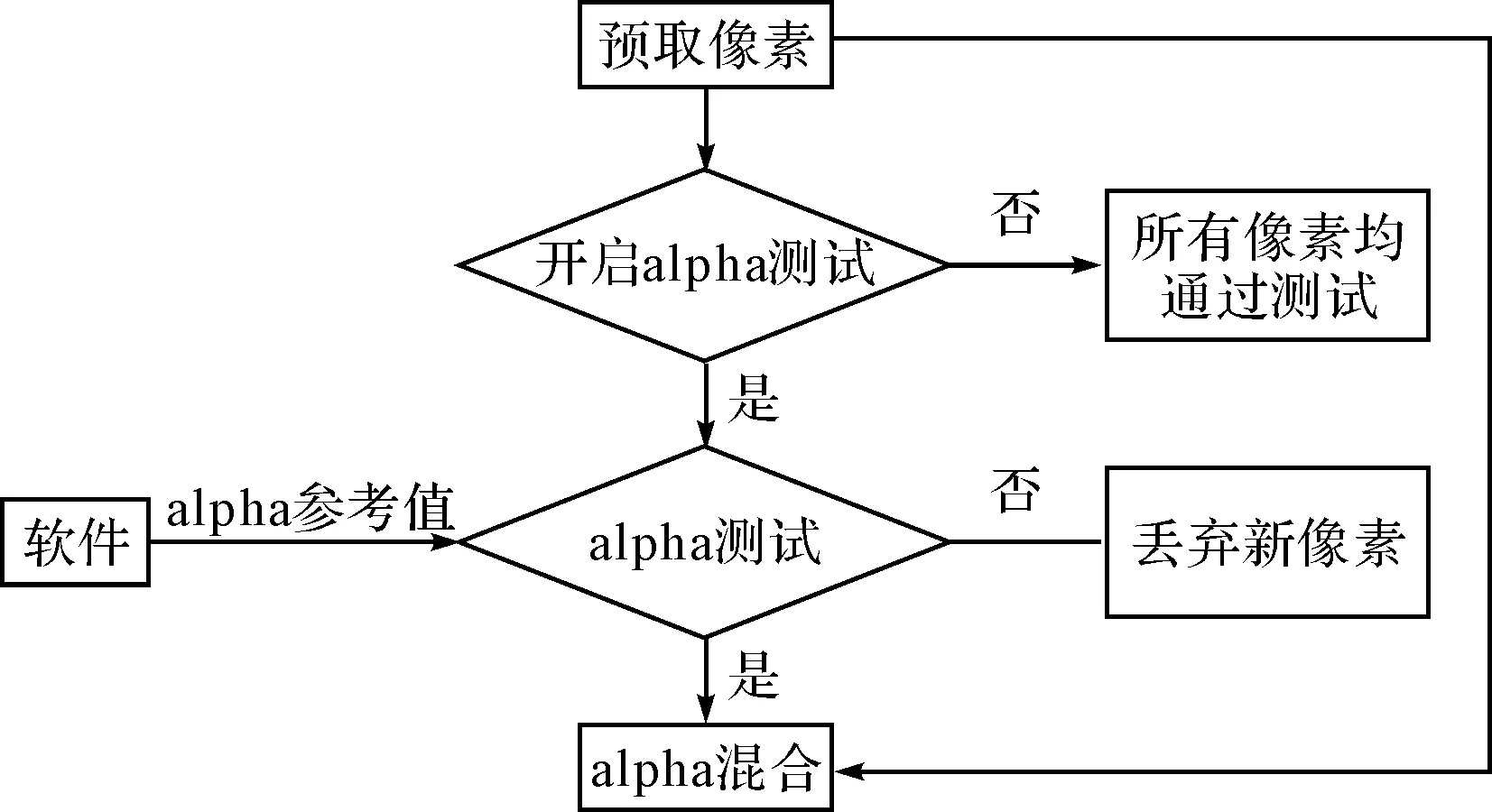

2.1 alpha测试

alpha测试去除大量的alpha值不满足需要的像素,减少系统资源消耗,有效提升图形流水线的处理速度。在一个复杂的三维场景中,大量的像素测试耗费巨大的系统资源,尤其是大部分的像素并不会绘制到显存中,尽量剔除这些不满足需要的像素,可以有效减轻图形管线的负担。

在RGBA模式下,alpha测试是根据一个像素的alpha值来判断是否保留或者丢弃这个像素。alpha测试启用时,可通过驱动为alpha测试配置一个参考值,硬件设计中通过将各像素的alpha值与参考值相比较来决定保留还是丢弃该像素[14]。

alpha测试的实现的流程图如图1所示。

图1 alpha测试的实现的流程图

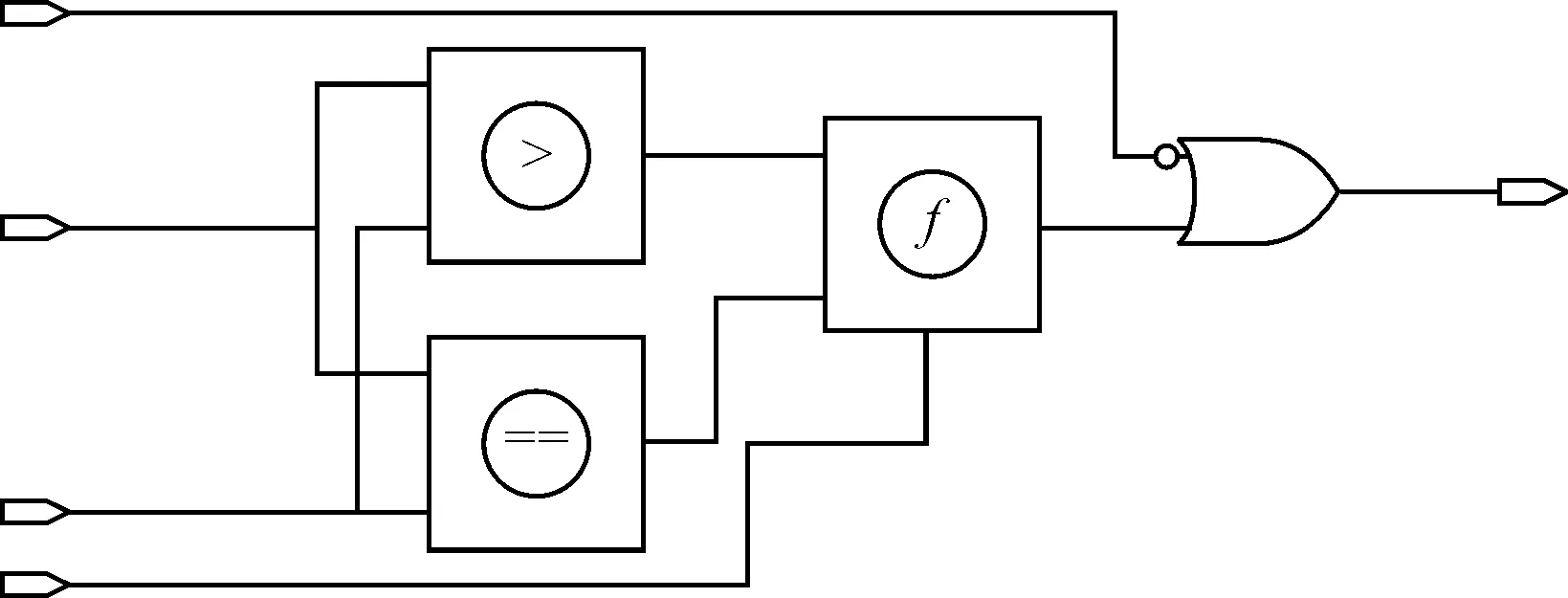

根据alpha测试的流程图,设计alpha测试的Verilog HDL代码。在Linux环境下用Synopsys公司的Verdi软件进行仿真,并生成RTL级电路,alpha测试的内部电路如图2所示。

图2 alpha测试的内部电路

2.2 alpha混合

alpha混合实现一种半透明的效果,模拟复杂场景中透过透明物体看到后面的物体的情况,alpha混合使场景看起来更加真实自然,有层次感。透过透明物体看向远处时既能看到透明物体的颜色也能看到后面物体的颜色,在这种场景中,将透明物体的颜色和后面物体的颜色按照一定规律组合来实现这种半透明的效果。

在硬件设计上当一个像素通过alpha测试后,它就可以按照不同的方式与当前颜色缓冲区的颜色进行混合,即将源像素的R、G、B和alpha值与已经存储在这个点的像素的对应值进行组合。

alpha混合启用后,一般按照以下四个逻辑步骤执行,但不一定是实际步骤:

1) 透明/不透明转化:在这个阶段,输入的alpha值(独立的源像素alpha值和目标像素alpha值)必须加以转化,从而匹配内部的alpha规则。在像素引擎内,alpha为“0”或“0x0”表示透明,alpha值为“1”或“0xFF”表示不透明。外部的alpha值也许使用的是相反的规则。这一步的输出是As(目标像素alpha值是Ad)或者1-As(目标像素alpha值是1-Ad);

2) 环境alpha替换:寄存器中的环境alpha值可以放大或者替换输入的alpha值,在这一步中,输入alpha值能够通过,或者直接被Ags(环境alpha)替换,或者被环境alpha放大(As*Ags)。源像素alpha值和目标像素alpha是完全不同的。

3) 混合因子的产生:在这个步骤,混合因子被计算出来。根据混合模式的不同,每个alpha的值可能为0、1、A或1-A。

4) 最终混合:这是最后一个步骤,源和目标像素最终混合,混合操作按根据混合模式参数的不同而有多种混合方式。

alpha混合的步骤如图3所示。

图3 alpha混合的实现

根据alpha混合的原理,设计alpha混合的Verilog HDL代码。在Linux环境下用Synopsys公司的Verdi软件进行仿真,并生成RTL级电路,alpha混合的内部电路如图4所示。

2.3 模板测试

模板测试基于片段掩码移除不符合条件的片段,它只有在存在模板缓冲区的情况下才会执行,如果不存在模板缓冲区,模板测试总能通过。模板测试启用时,可通过驱动为模板测试配置一个参考值,硬件设计中通过将像素的一个值与参考值相比较来决定保留还是丢弃该像素。无论一个像素通过或未通过模板测试,模板缓冲区的数据必须修改[14]。

模板缓冲区存储模板参考值,使用模板缓冲区可以把将要绘制的图形限制在屏幕的某个特定区域内,就像使用镂空的纸板喷漆一样。比如,实现一个模拟驾驶的程序,在模板缓冲区内存储一幅挡风玻璃形状的图像,然后绘制整个场景,模板缓冲区能够防止那些透过挡风玻璃无法看到的物体被绘制出来。

图4 alpha混合的内部电路

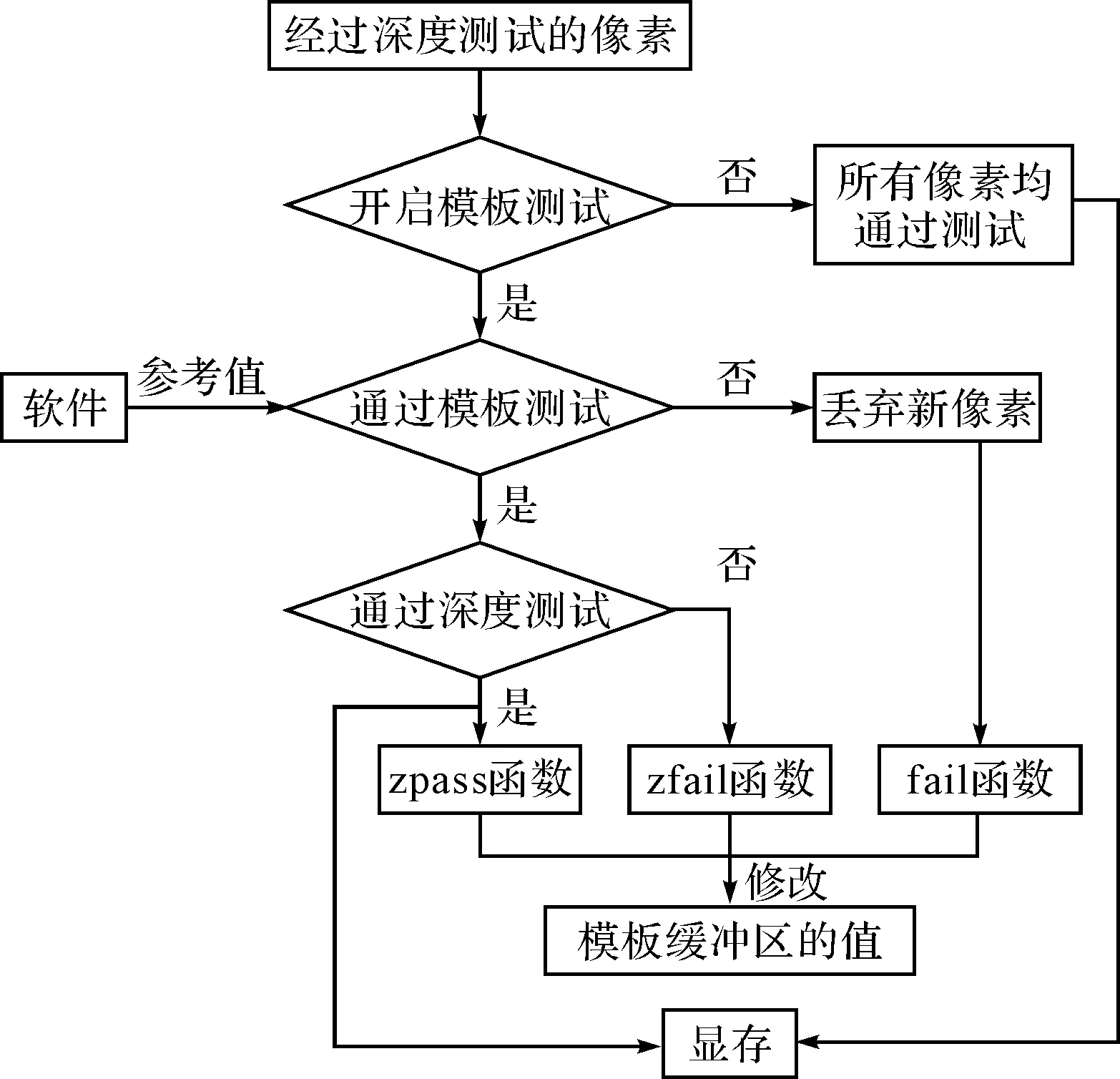

模板测试把参考值与模板缓冲区的值进行比较,但比较只在那些对应的掩码设置为1的位上进行。当模板测试开启后,无论这个像素是否通过模板测试,必须修改模板缓冲区的数据。fail、zfail、zpass这三个函数指定了像素进行了模板测试后怎样修改模板缓冲区的值。如果像素无法通过模板测试,则应用fail函数;如果模板测试通过但是却无法通过深度测试,zfail函数就会应用;如果模板测试通过,深度也通过或者未执行那个深度测试的情况下,应用zpass函数。模板测试的实现的流程图如图5所示。

图5 模板测试的实现的流程图

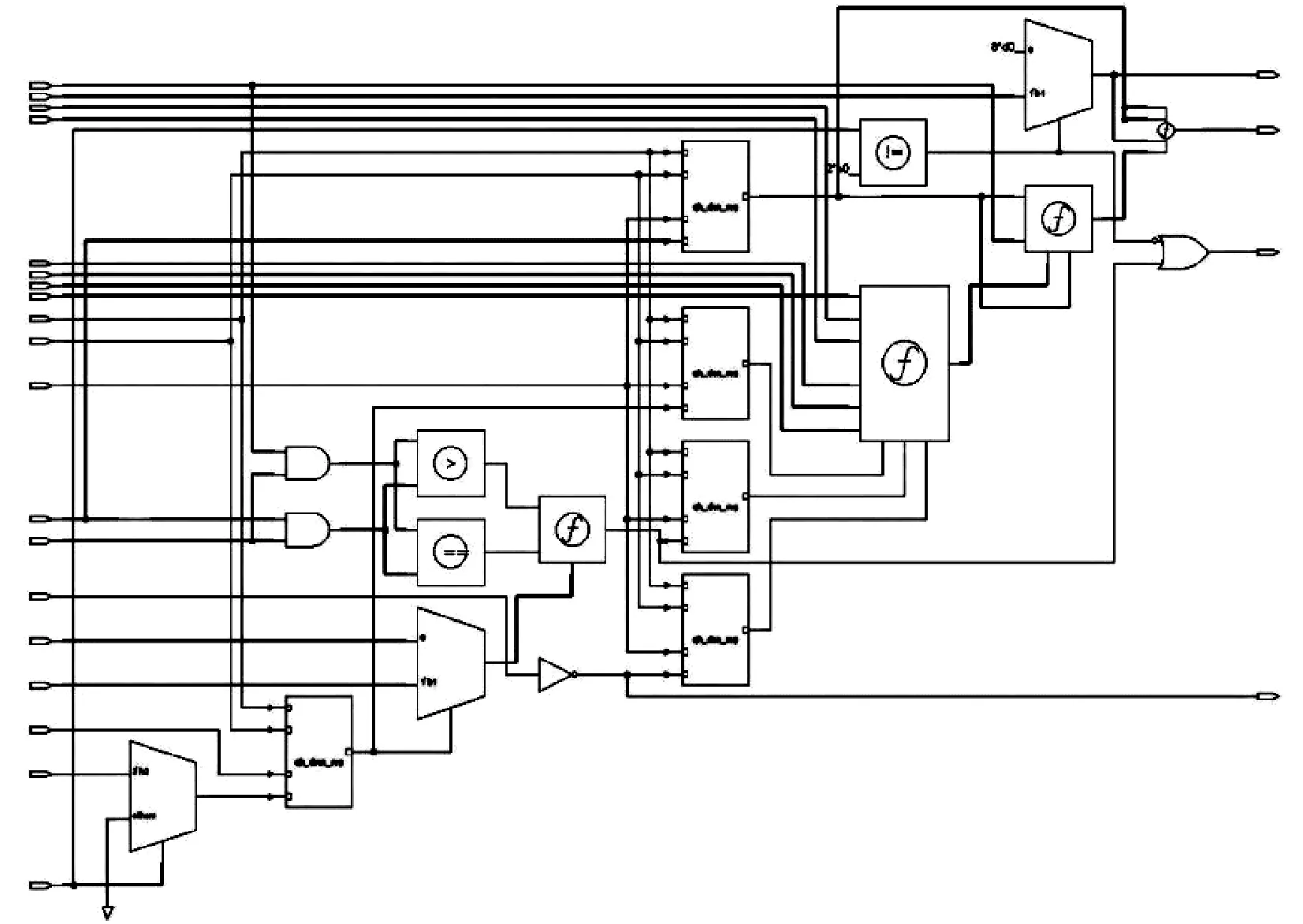

根据模板测试的流程图,设计模板测试的Verilog HDL代码。在Linux环境下用Synopsys公司的Verdi软件进行仿真,并生成RTL级电路,模板测试的内部电路如图6所示。

图6 模板测试的内部电路

2.4 深度测试

深度测试剔除被遮挡的像素,在场景渲染完成之后,只有那些没有被其他物体遮挡的物体才会保留,并绘制到显存。在一个复杂的三维场景中,存在着大量物体,但有很多物体是被其他物体遮挡的,深度测试将这些被近处不透明物体遮挡的远处物体剔除[14]。

对于屏幕上的每一个像素,都会对应一个与屏幕像素数目一致的缓冲区,用来保存片段的深度值,这就是深度缓冲区,即Z_buffer、Z缓冲区。深度缓冲区一般用于隐藏表面的消除。当整个场景完成深度测试之后,只有那些没有被其他物体遮挡的物体或者物体的部分才会保留。因此场景中需要绘制的像素数量会急剧减小,有效地提升图形处理器的处理能力。

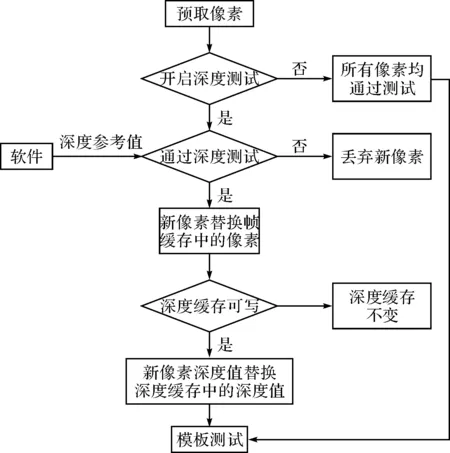

当深度测试通过,深度缓冲区可写时,将测试像素的深度值写入对应的深度缓冲区,深度测试的实现的流程图如图7所示。

图7 深度测试的实现的流程图

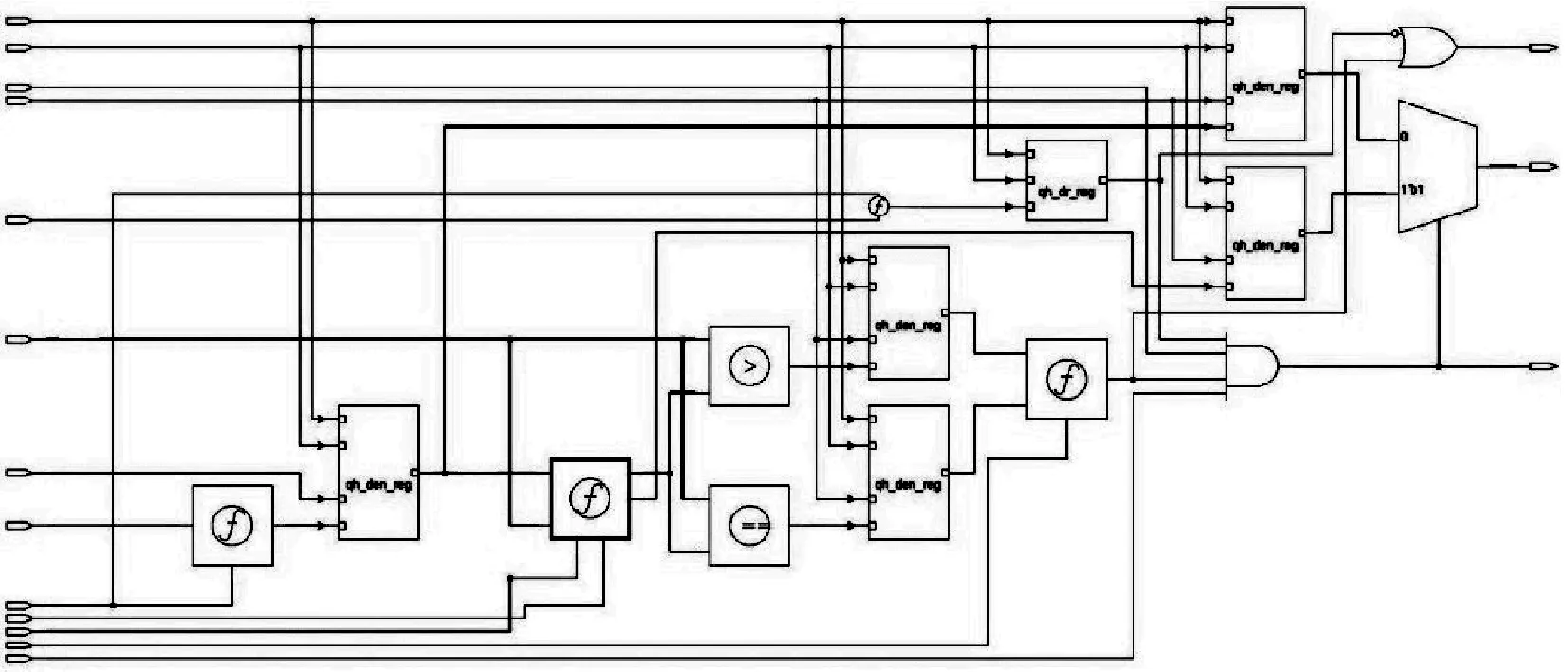

根据深度测试的流程图,设计深度测试的Verilog HDL代码。在Linux环境下用Synopsys公司的Verdi软件进行仿真,并生成RTL级电路,深度测试的内部电路如图8所示。

图8 深度测试的内部电路

3 功能仿真与验证

硬件代码设计完成并完成功能仿真后,需要对图形处理器进行FPGA验证,进一步验证设计的合理性和正确性。本节包括图形处理器像素引擎的FPGA验证以及验证结果。

本课题设计的图形处理器选择在S2C公司的QuadE Virtex-7 TAI Logic Module开发验证平台板上实现验证。该验证板丰富的板上资源可以完全满足本课题的FPGA验证需要。

在Linux环境下用Synopsys公司的vcs软件进行功能仿真,验证设计的合理性和正确性。在功能仿真通过后,在验证版上进行实际验证。该验证板可以运行Linux操作系统,为了便于快速验证,在Linux操作系统中编写测试程序,观察测试程序的运行效果。

3.1 alpha测试

alpha测试剔除那些alpha值不符合要求的物体,大大减轻了图形处理流水线的负担,因此在一个拥有较多透明物体的场景中,alpha测试是一种有效的提升系统性能的方法。

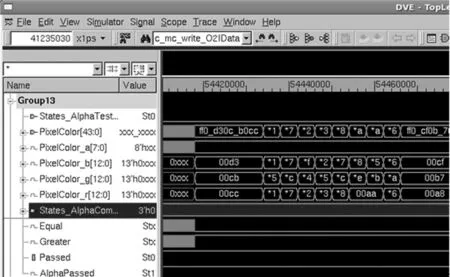

在Linux环境下用Synopsys公司的vcs软件进行功能仿真,仿真波形图如图9所示。PixelColor_a、PixelColor_r、PixelColor_g和PixelColor_b分别是进入alpha测试的像素颜色的RGBA分量,States_AlphaReference和States_AlphaCompare分别是alpha参考值和alpha比较参考函数。

图9 alpha测试仿真波形图

当States_AlphaTestEnable为0,即alpha测试关闭alpha时测试直接通过。当States_AlphaTestEnable不为0时,根据输入像素的alpha值和alpha比较参考值States_AlphaReference比较得到比较中间结果Greater和Equal的值,并根据alpha比较参考函数States_AlphaCompare得到alpha测试比较结果Passed,若Passed为1表明alpha测试通过。

3.2 alpha混合

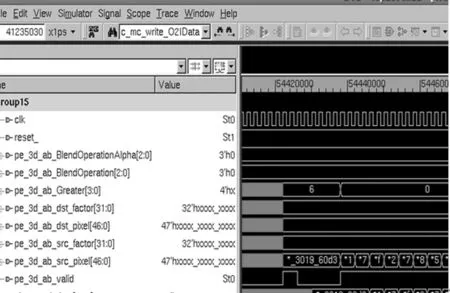

alpha混合实现的半透明效果物体透明可极大地提高场景的真实性,alpha混合就是源像素和目标像素的组合。在Linux环境下用Synopsys公司的vcs软件进行功能仿真,alpha混合仿真波形图如图10所示。pe_3d_ab_src_pixel是源像素颜色值,pe_3d_ab_dst_pixel是目标像素颜色值,pe_3d_ab_src_factor和pe_3d_ab_dst_factor分别是源像素混合因子和目标像素混合因子,pe_3d_ab_BlendOperationAlpha和pe_3d_ab_BlendOperation分别为alpha混合函数和颜色混合函数。

图10 alpha混合的仿真波形

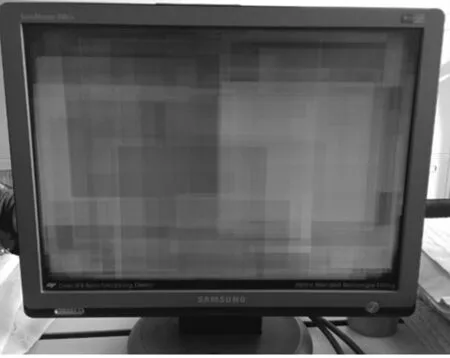

当源像素和目标像素输入alpha混合模块后,首先将其拆分为R、G、B、A值和混合因子混合,然后分别对各分量进行混合,混合完成后将个颜色组合并输出像素颜色值ab_pe_3d_data,并输出颜色使能ab_pe_3d_valid。图11显示了在一个有无数不同颜色透明矩形映射到屏幕上得效果,各矩形互相叠加,但是在屏幕上的叠加区域一个像素点显示多个像素的颜色,因此alpha混合可以实现半透明的效果。

图11 alpha混合效果图

3.3 模板测试

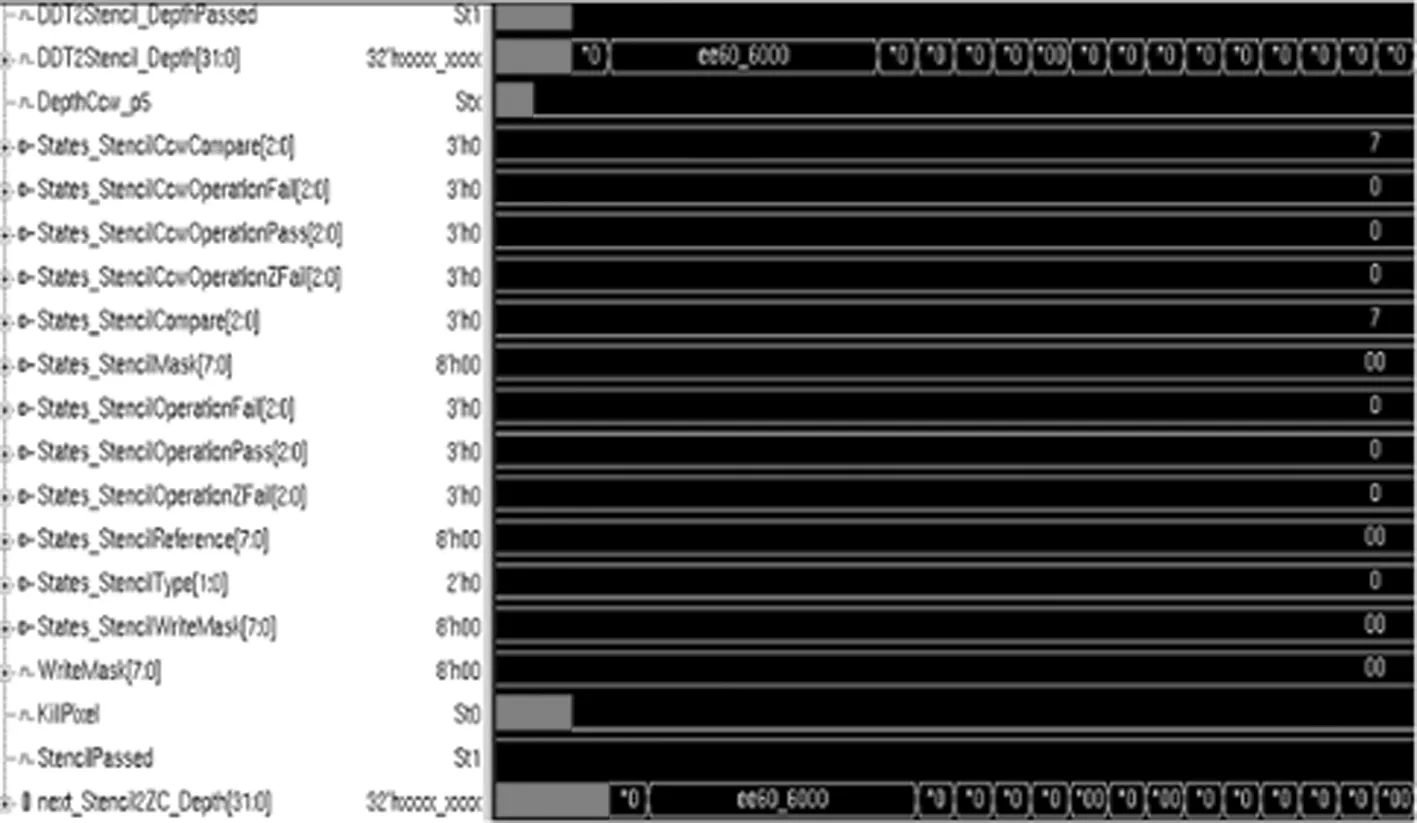

模板测试可以将要绘制的图形限制在屏幕的某个特定区域内,比如使用镂空的纸板喷漆一样。在指定区域绘制图像,当此区域场景变化时只需重新绘制此区域的图像,屏蔽其它部分,减少图形绘制量,提高图形处理器的速度。在Linux环境下用Synopsys公司的vcs软件进行功能仿真,仿真波形图如图12所示。在输入接口中,DS_Enabled为模板测试使能位,DDT2Stencil_Depth是输入像素的深度值,States_StencilType是输模板类型,States_StencilMask是模板掩码,States_StencilReference是模板参考值,States_StencilCompare是模板,States_StencilCompare是模板比较函数,States_StencilOperation是得知测试结果后模板缓冲区的修改函数,States_StencilWriteMask表明模板缓冲区是否可写,DDT2Stencil_DepthPassed是表明深度测试是否通过。

图12 模板测试仿真波形

当DS_Enabled为0时,表明模板测试被禁用,模板测试直接通过。当DS_Enabled为1时,模板测试开启。首先根据输入像素深度值得到像素的模板值,并与模板参考值相比较得到比较中间结果Greater和Equal的值,并根据模板比较参考函数Compare得到模板测试比较结果Passed,若Passed为1表明模板测试通过。

当像素无法通过模板测试时,应用Fail函数修改模板缓冲区的值,当像素通过模板测试但是未通过深度测试时,Zfail函数就会应用,当两者都通过时,应用Pass函数修改模板缓冲区的值。当模板缓冲区可写时,修改模板缓冲区的值并输出像素的深度值next_Stencil2ZC_Depth,同时输出像素保留标志位KillPixel。

3.4 深度测试

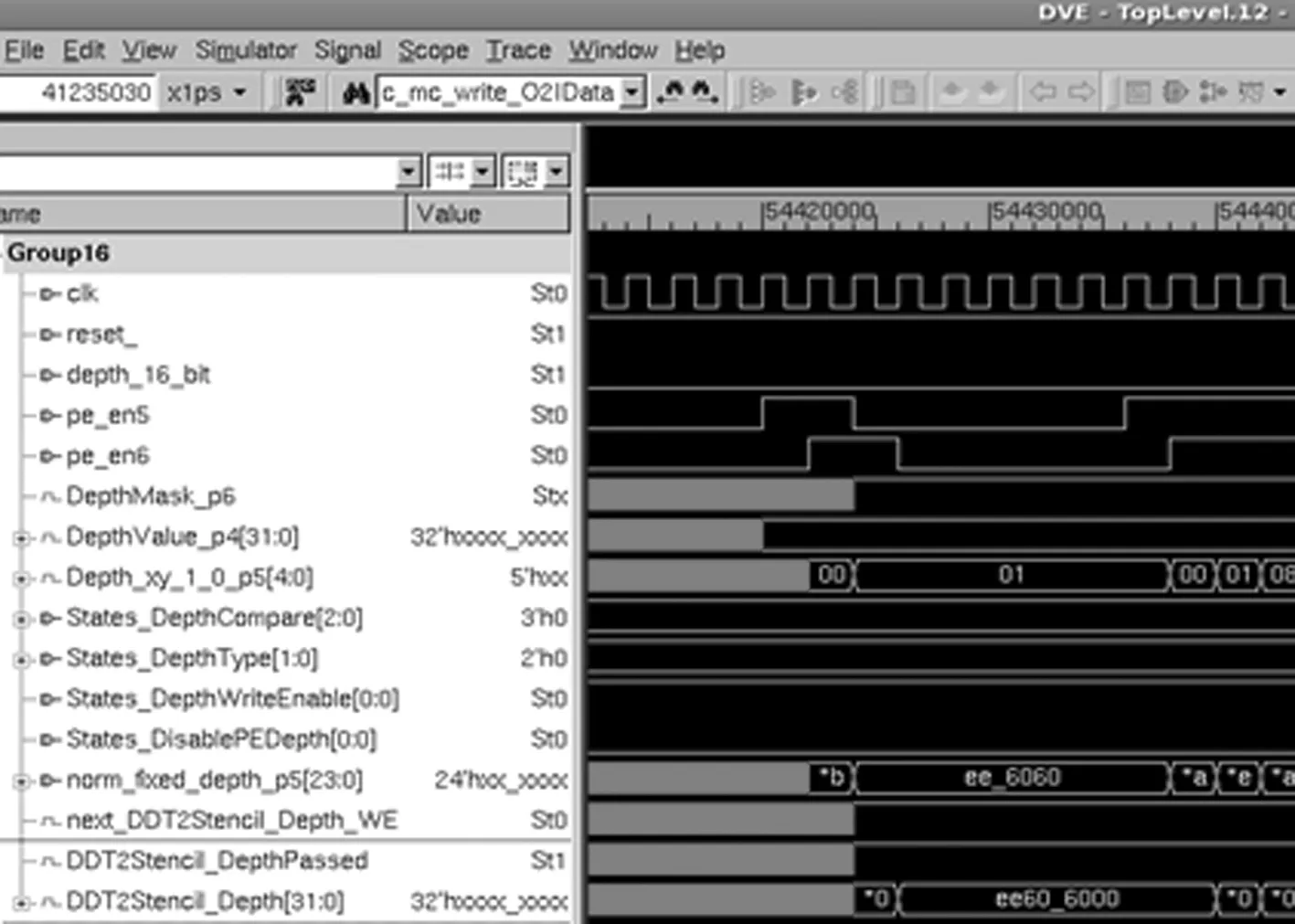

对于图形处理器,深度测试的目的就是去除那些被遮挡的像素,减少绘制的像素的数量,提升系统性能。根据深度测试的流程图,设计深度测试的Verilog HDL代码。在Linux环境下用Synopsys公司的vcs软件进行功能仿真,仿真波形图如图13所示。

图13 深度测试的仿真波形

在输入接口中,States_DisablePEDepth为深度测试使能位,States_DepthWriteEnable是深度写使能,DepthMask_p6是深度字节掩码,States_DepthType为深度类型,Depth_xy_1_0_p5为深度有效位,States_DepthCompare为深度比较函数,States_DepthType为深度类型,DepthValue_p4为目标像素深度值。

当States_DisablePEDepth为1时,深度测试关闭,测试直接通过;为0时,深度测试开启。根据输入像素的深度值和深度比较参考值比较得到比较中间结果Greater和Equal的值,并根据深度比较参考函数States_DepthCompare得到深度测试比较结果Passed,若Passed为1表明深度测试通过。DDT2Stencil_Depth输出通过测试的像素深度值。像素未通过测试时,丢弃该像素。

图14显示了在一个大厅中镜头随圆球移动的效果。物体的深度测试开启后,圆球背后的物体都被遮挡,无法被看到,只有前面物体可以显示出来,因此深度测试可以实现剔除被遮挡物体的效果。

图14 深度测试效果图

4 结语

像素引擎直接影响着输出画面的效果是GPU研究的重点,本文详细介绍了像素引擎的主要功能,画出了各功能模块的流程图,采用Verilog HDL语言设计了各功能模块。最后用Synopsys公司的vcs软件对各个功能模块进行了功能仿真,并在S2C公司的QuadE Virtex-7 TAI Logic Module开发验证平台验证像素引擎的功能。在Linux系统下运行一些程序,以验证像素引擎的功能的完整性,并根据验证结果不断修改设计,验证结果表明该像素引擎能够有效实现国产GPU的像素处理的所有功能,达到了设计要求。

[1] 徐伟.基于嵌入式系统的二维图形处理加速器[D].西安:电子科技大学,2012.

[2] KAINULAINEN J. Stencil Shadow Volumes[D]. Helsinki: Helsinki University of Technology,2002.

[3] 占卫华.龙芯平台GPU驱动实现与浏览器Flash性能优化[D].北京:中国科学院研究生院,2012.

[4] 钟煜,朱敏,陈雪,等.基于DSMI算法和GPU加速的大规模视频检索系统[J].计算机应用研究,2011,28(11):4373-4375.

[5] 唐兵.GPU优化的3D游戏室外大场景的渲染[D].金华:浙江师范大学,2010.

[6] 赵改善.地球物理高性能计算的新选择:GPU计算技术[J].勘探地球物理进展,2007,30(5):399-404.

[7] SHREINER D. THE KHRONOS OPENGL ARB WORKING GROUP. OpenGL Programming Guide[M]. Seventh Edition.北京:机械工业出版社,2010:7-9.

[8] HOLTEN-LUND H. FPGA-Based 3D Graphics Processor with PCI-Bus Interface, An Implementation Case Study[C]//Norchip Proceedings,2002:316-321.

[9] KILGARD M J. Realizing OpenGL: Two Implementation of One Architecture[J]. Graphics Hardware,1997:45-55.

[10] Jon P. Ewins, Phil L. Watten, Martin White, et al. Codesign of Graphics Hardware Accelerators[J]. Graphics Hardware,1997:103-110.

[11] 李实.2014年国产ARM SoC芯片巡礼(上)[J].微型计算机,2014,8(上):56-60.

[12] 李实.2014年国产ARM SoC芯片巡礼(下)[J].微型计算机,2014,8(下):54-58.

[13] 长沙景嘉微电子[EB/OL]. http://www.jingjiamicro.com/index.html.

[14] STALLINGS W. Computer Organization & Architecture[M]. Seventh Edition.北京:清华大学出版社,2006:91-94.

Pixel Engine in GPU Design and Implementation

DING Zhenqing XIONG Tinggang QIN Xingang

(Wuhan Digital Engineering Institute, Wuhan 430205)

With the spread of various of amusement equipments and date processing equipment, 3D graphic technique has gradually been used in all kinds of fileds. Aiming at the shortage of GPU research, this paper designs a full function Pixel Engine with alpha test, stencil test, depth test and alpha blend. Then, this paper designs the function module for Pixel Engine by Verilog HDL and generates the internal circuit diagram. Last, this paper does emulation for the function module and validates its function in develop board. The verification result indicates that Pixel Engine can complete all the function of domestic GPU Pixel Engine, and it has met the design requirements.

computer graphics, GPU, pixel engine, pixel test, Cache

2015年4月11日,

2015年5月29日

丁振青,男,硕士,研究方向:计算机图形学、FPGA设计、云计算。熊庭刚,男,博士,研究员,硕士生导师,研究方向:计算机体系结构。秦信刚,男,高级工程师,研究方向:计算机图形学、FPGA设计、系统总线设计。

TP301

10.3969/j.issn.1672-9730.2015.10.029

验证结果表明,该像素引擎能够有效实现国产GPU的像素处理的所有功能,达到了设计要求。