扩展收敛域任意对数CORDIC算法与FPGA实现

2015-03-07陈旭文刘桂雄唐文明

陈旭文,刘桂雄,唐文明

(1.揭阳职业技术学院,广东 揭阳 522051;2.华南理工大学,广东 广州 510640)

扩展收敛域任意对数CORDIC算法与FPGA实现

陈旭文1,刘桂雄2,唐文明2

(1.揭阳职业技术学院,广东 揭阳 522051;2.华南理工大学,广东 广州 510640)

针对经典自然对数坐标旋转数字计算机(coordinate rotation digital computer,CORDIC)算法在应用上存在问题,研究扩展收敛域任意对数CORDIC算法与FPGA实现。通过区间压缩方法,对收敛域外的数据进行转换,实现收敛域扩展至全收敛域,并应用换底公式扩展到任意底数的对数运算。仿真试验表明,采用15级流水线结构,以10为底的对数CORDIC运算最大时延小于17个时钟周期,最大计算误差为0.00027。该算法应用于40mm玻璃钢的超声检测中,其TCG回波图能有效抑制杂散波,提高信号的分辨力,运算速度比传统方法快,对超声相控仪器的开发具有应用价值。

扩展收敛域;对数;区间压缩;FPGA

0 引 言

坐标旋转数字计算机(coordinate rotation digital computer,CORDIC)算法,是1959年Volder[1]提出的通用迭代算法,它用一系列固定角度的不断偏摆迭代以逼近所需旋转角度,控制向量在线性坐标系、圆坐标系和双曲坐标系下的旋转和定向操作,由简单加法、移位操作实现各类初等函数求值运算。对数函数的计算是在双曲坐标系向量模式下完成。硬件实现对数函数求值有很多方法,如传统方法包括查表法、泰勒展开式法、多项式逼近法、抛物线合成法等。Mitchell[2]用若干条连接相邻整数点的直线拟合,提出一种底数为2的对数近似算法,算法判断简单,容易用FPGA实现,但只能保证整数部分的准确度。很多文献表明:查表法随结果准确度提高或输入值范围增大,需大量的存储单元;泰勒展开式法需要复杂的求导运算以及大量的乘法器与除法器,速度慢效率低;多项式逼近法复杂且准确度不高。近年来,在研究CORDIC算法的FPGA实现方面,国内外学者做了很多有益的研究[3-5]。Maharatna[6]提出一种无需扩展因子的SF-CORDIC算法,省去z通路和扩展因子的计算,但仅适用于旋转角度已知且位宽较小情况。牟胜梅等[7]提出一种统一的指数/对数迭代求值方法,虽面积开销减小,但收敛域太小。黄晓可等[8]提出一种改进的SF-CORDIC算法实现指数和对数运算,省去扩展因子的计算,但需要三阶以上的麦克劳林展开式近似,以提高准确度,系统运算相对复杂。以上改进算法虽取得巨大突破,但存在收敛域小或计算复杂等不足。本文提出一种运算简单、收敛域更广的双曲系统对数CORDIC算法的FPGA实现方法,并可广泛应用于FFT变换、超声检测 (time complement gain,TCG)、信道编码系统等领域,具有较高的实用价值。

1 改进型对数函数CORDIC算法机理

1.1 经典自然对数函数CORDIC算法

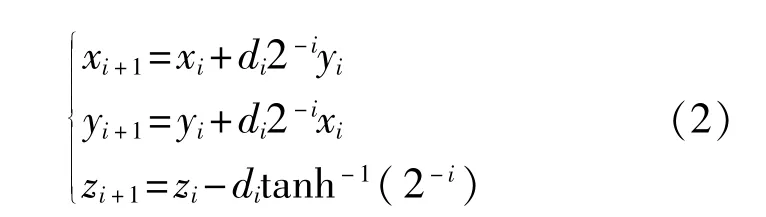

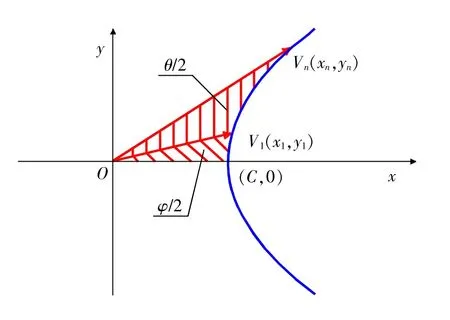

双曲坐标系下的CORDIC算法有旋转模式和向量模式两种。图1为双曲函数坐标旋转模型图,双曲线x2-y2=c2上点V1(x1,y1)沿着上半轴曲线移动到点Vn(xn,yn),可表示为

向量模式下,设旋转方向为di,校模因子为K,令θ=tanh-1(2-i),则zi+1=zi-ditanh-1(2-i),式(1)可转化为

为满足迭代序列收敛,迭代序列i的取值从第4项开始,每个3k+1(k∈Z+)项必须重复一次,即i=1,2,3,4,4,5,…,13,13,14,…,通过yi控制微旋转方向,使得yi→0。经过n次旋转后,有:

图1 双曲函数坐标旋转模型

从而获得自然对数CORDIC算法的表达式。

1.2 自然对数函数CORDIC算法的收敛域扩展

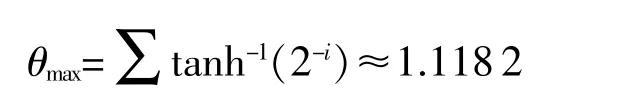

根据式(3)可知双曲线坐标CORDIC算法的收敛范围为

故经典对数函数CORDIC算法的收敛域[9]为

由于zin的范围较小,实际应用意义不大,必须对收敛域进行扩张处理。

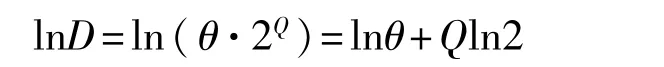

当zin超出收敛域时,可令D=θ·2Q,则:

其物理意义是:若整数Q能确定,则Qln2可转换为定点数,可把ln(θ·2Q)的计算等效转化为lnθ的计算,即把收敛域外的输入值运算转化为收敛域内的迭代,通过区间压缩方法实现对数函数CORDIC算法的收敛域扩展。

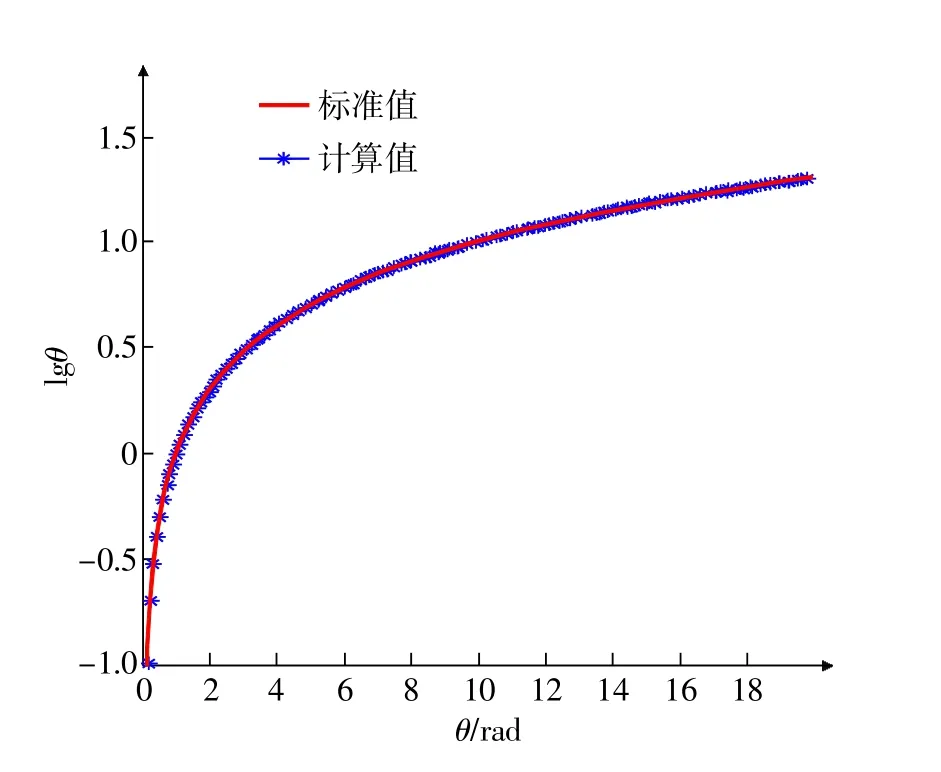

图2 自然对数CORDIC算法在扩展收敛域的Matlab系统仿真图

图2给出了自然对数CORDIC算法在扩展收敛域的Matlab系统仿真图。可以看出,通过对收敛域的扩展,自然对数CORDIC算法在收敛域以外的区间里,都与理论值基本重合,实现任意输入角度的运算,这对提升对数CORDIC的应用具有实际意义。

1.3 任意对数函数CORDIC算法的推广实现

图3 底数为10的对数函数CORDIC算法Matlab系统仿真图

2 对数函数CORDIC算法的FPGA实现

2.1 FPGA实现结构

为保证高准确度和快速运算的要求,必须把小数转化成整数,即通过扩大2N倍(N的大小决定运算的准确度)对小数进行定点化,以保证快速运算。FPGA的实现只需两个乘法器,即可实现整数Q和小数θ定点化值求解。

考虑准确度和速度的矛盾问题,在FPGA实现上采用查找表和流水线法相结合的解决方案,即对部分固定角度通过查找表进行存储,只占用极少存储空间,有利于提高运算速度,同时保证一定运算准确度。

2.2 性能分析

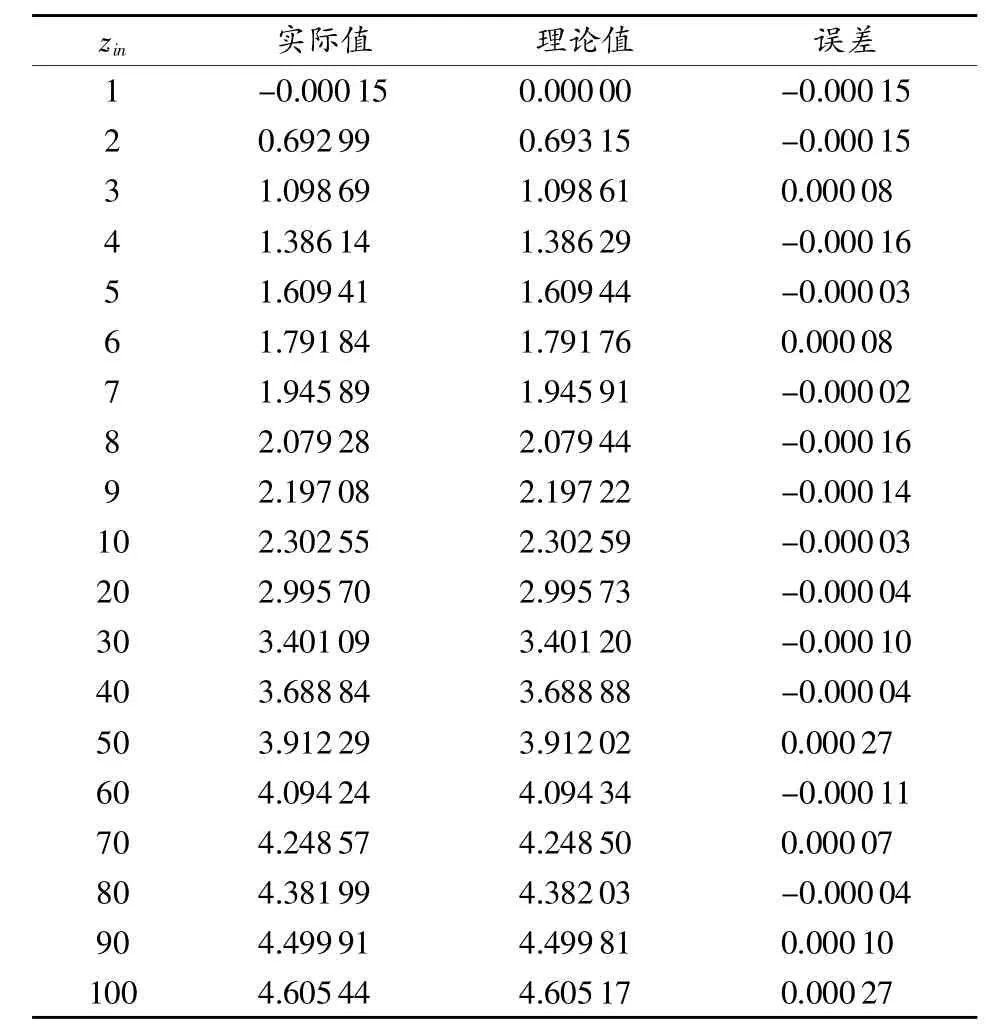

为验证对数CORDIC算法的系统资源、运算准确度和时间延迟等性能,本文以10为底的对数为例,采用15级流水线算法结构,即扩大216进行定点化运算。基于Modelsim进行FPGA仿真,图4给出了FPGA仿真的时延波形,设置时间周期T=10 ns(T为时钟周期,主时钟频率为100 MHz),算法时间延迟t1=17T,考虑初始时延等情况,算法总时延t<25T(250ns)。表1列出了收敛域zin∈[1,100]部分输入值的对数运算结果,最大运算误差为0.00027,达到10-3数量级,可以满足实际应用要求。

2.3 应用测试

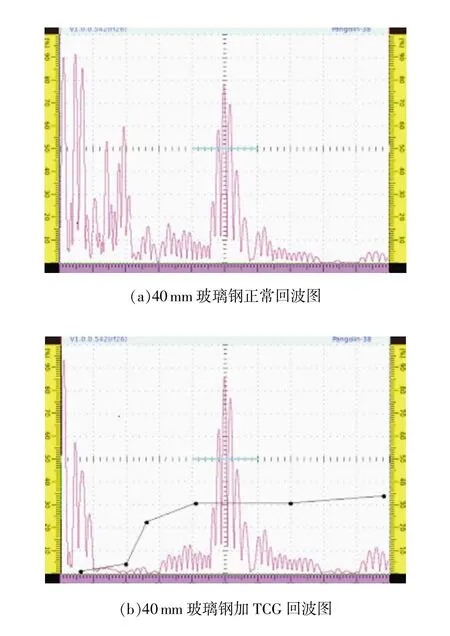

超声检测中,超声回波增益用分贝dB表示,与放大倍数Au成对数关系,即dB=20lgAu,超声仪器传统TCG补偿通常靠CPU调用C语言库函数来实现其中的对数函数,运算耗时较长。如何解决运算准确度和运算速度的矛盾成为超声仪器极待解决的技术难点。基于FPGA应用扩展对数CORDIC算法,可准确、快速计算出任意增益的大小,图5为超声回波增加TCG效果对比图,其中图5(a)为40mm玻璃钢正常回波图,图5(b)为40mm玻璃钢加TCG回波图,可知增加TCG功能后能有效抑制杂散波,提高信号分辨力。测试证明:本算法运算准确度能够满足工业超声检测要求,运算速度比传统方法更快,这对超声相控仪器的开发具有较大应用价值。

3 结束语

1)通过区间压缩方法,对收敛域外的数据进行转换,并通过定点化技术,实现收敛域扩展至全收敛域,解决传统自然对数收敛域太窄的问题,并用换底公式扩展到任意底数的对数运算,极大地提高对数CORDIC算法的应用范围。

2)任意底数对数CORDIC运算仿真结果表明最大时延小于25个时钟周期,运算准确度达10-3数量级,完全满足目前超声相控阵仪器实际应用要求。

图4 FPGA仿真的时延波形

表1 收敛域zin∈[1袁100]部分输入值的对数运算结果

图5 超声回波增加TCG效果对比图

3)对数函数CORDIC算法的FPGA实现彻底解决信息处理中运算准确度、时间延迟、系统资源等关键技术问题,在超声检测中实现TCG功能的重要算法有重要的实用价值。

[1]Volder J E.The CORDIC trigonometric computing technique[J].IRE Transon Electronic Computers,1959,8(3):330-334.

[2]Mitchell J N.Computer multiplication and division using binary logarithms[J].IRE Trans Electronic Computers,1962,11(8):512-517.

[3]刘美娟,许建华,张超.基于CORDIC算法的对数放大器的FPGA实现[J].仪器仪表学报,2008,29(4):328-331.

[4]林若波,刘桂雄,唐文明.应用补码的通项式正余弦CORDIC算法FPGA实现[J].中国测试,2014,40(3):102 -106.

[5]牟胜梅.面向可重构系统的几个常用算法及其实现技术研究[D].长沙:国防科技大学,2008.

[6]Maharatna K, Banerjee S, Grass E, et al.Modified virtually scaling-free adaptive CORDIC rotator algorithm and architecture[J].IEEE Transactions on Circuits and Systems for Video Technology,2005,11(11):1463-1474.

[7]牟胜梅,李兆刚.一种面向FPGA的指/对数函数求值算法[J].计算机工程与应用,2014,47(33):59-61.

[8]黄晓可,刘洛琨,汪涛,等.基于改进SF-CORDIC的指数和对数函数求值算法[J].计算机应用与软件,2014,31(2):279-282.

Arbitrary logarithm CORDIC algorithm based on expansion convergence domain and FPGA implementation

CHEN Xuwen1,LIU Guixiong2,TANG Wenming2

(1.Jieyang Vocational and Technical College,Jieyang 522051,China;2.South China University of Technology,Guangzhou 510640,China)

Aiming at the problems of classic natural logarithm CORDIC algorithm on application,the convergence domain of extension arbitrary logarithm CORDIC algorithm and FPGA implementation is discussed.Using interval compression method to convert the extraterritorial data of convergence domain,the whole convergence domain is extended,and the arbitrary base logarithm operation is extended on the application ofthe soled formula.Simulation results show that using 15 stage pipeline structure,the maximum delay of logarithm CORDIC algorithm with base 10 is less than 17 clock cycles,and the maximum error is obtained 0.000 27.Ultrasonic testing on the 40 mm glass steel,the TCG echo can effectively suppress the spuriouswave,improve the signalresolution,and the operation speed isfasterthan traditional methods, which has important application value on development of ultrasonic phased array instrument.

extended convergence domain;logarithm;interval compression;FPGA

A

:1674-5124(2015)07-0108-04

10.11857/j.issn.1674-5124.2015.07.025

2015-02-08;

:2015-03-17

国家重大科学仪器设备开发专项(2013YQ230575)

陈旭文(1976-),男,广东揭阳市人,讲师,硕士,主要从事计算机应用研究与教学工作。