基于Simulink 的绝对位置传感器的FPGA 实现

2015-03-06陈文艺雷武亮

陈文艺,周 林,雷武亮

(1.西安邮电大学 物联网与两化融合研究院,陕西 西安 710061; 2.西安邮电大学 通信与信息工程学院,陕西 西安 710061)

近年来,基于图像的光电编码器得到广泛应用。本文中绝对位置传感器即是通过图像传感器直接对编码盘进行图像采集,再通过FPGA 对采集的数字图像进行实时处理以获取绝对位置信息[1-2]。而传统的FPGA 设计方法来做图像处理由于其算法和实现的分离导致设计周期长,而采用基于Simulink 的FPGA 设计方法,不仅有利于快速验证算法,切在算法仿真通过后可快速自动转换为Verilog HDL 语言完成实现[3]。

关于模型HDL 转换,Simulink 中有成熟的第三方产品,如Altera 的DSP Builder,Xilinx 的System Generator均可将模型自动转换为HDL 设计,然而该方法不仅需要重新安装第三方软件,且功能模块使用过于依赖厂家,而本文中提出的基于Simulink 的HDL 设计不需要再安装软件,且灵活性高[4-5]。只要只用规范的语言,用户还可自定义功能模块,更有利于满足变化的用户需求。

1 系统模型

由图1 可知,通过从图像传感器得到需要的分辨率图像,经图像采集模块送入绝对位置计算模块计算绝对位置[6]。本文提出的方法即用于实现绝对位置计算模块的实现。利用Simulink 建模来实现绝对位置计算模块,并在其仿真验证通过将其转换为HDL 模型。该模块主要功能有:将采集的二维图像信号转化为一维灰度信号,并对灰度信号按列方向加权平均后进行滤波差分,通过光强质心法和迭代最小二乘拟合算法最终得出绝对位置值[7]。

图1 系统模型

2 基于Simulink 的HDL 设计

由图2 可知,在使用Simulink 进行硬件设计时大致分为以下几个步骤:

(1)在Simulink 中利用其涵盖众多的功能模块实现功能设计。此时为了保证功能的正确性一般都使用浮点型数据。

(2)验证功能设计的正确性,为功能模型(浮点模型)向定点模型转换做准备。

(3)对定点模型进行仿真并与浮点模型做比较,分析误差。

(4)将定点模型转化为Verilog HDL,并进行联合仿真。

图2 基于Simulink 的HDL 设计流程

下面将分浮点模型,定点模型,HDL 模型3 个层次做介绍。并选择绝对位置计算模块中子模块:脉冲中心位置计算Center 模块来进行实际转换。

2.1 浮点模型

并非Simulink 中所有模块都满足向HDL 的转换,所以在进行浮点模型设计时应对此有一个初步的了解。在Simulink Hdllib 模块库中查看支持向HDL 转换的功能模块

虽然Simulink 功能模块众多,但也无法满足千变万化的实际需求,所以当某个功能需求无法找到一个合适的模块来实现,则此时可使用Matlab Function 封装一个模块,即使用M 语言编程来实现简单一定的逻辑功能。

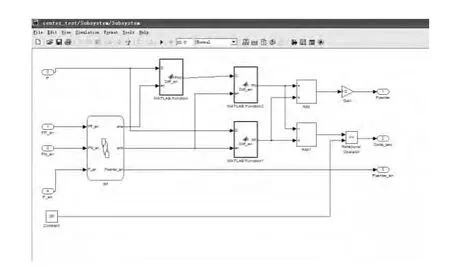

Center 模块主要计算一维灰度信号中每个脉冲中心的像素位置值,并判断每个脉冲所表示的编码值,其浮点设计如图3 所示。

图3 Center 模块浮点设计

2.2 定点模型

对浮点模型进行定点转换,首先要对模块所有的数据进行分析,因在定点转化时位数的限制将带来精度的损失。所以应根据需求要使用合适的数据位宽和舍入量化算法来达到资源与精确度之间的平衡[8]。

对于Simulink 中含有的功能模块而言,将其转换为定点模型不论是手动分配字长还是采用Fixedpoint tools,对模型整体进行分析自动分配字长和小数位这一过程都相当简单,而对于Matlab Function,由于其是用户根据自己需要用M 语言写的模块,所以对该模块进行定点数转换相对较为复杂,但只要遵循一定的规则,转换亦可顺利完成:(1)定义的变量均要使用定点数对象。(2)注意变量的运算法则,如Product-Mode,RoundMode,SumMode,OverflowMode 等根据实际需求进行改变。(3)某些运算函数不适用于定点模型的设计,此时或可考虑使用其他满足的函数或使用定点运算法则来实现。例如mod 模运算函数,其不支持定点模型,那么可以通过将定点对象运算法则中OverflowMode 属性设置为wrap 来实现模运算功能。

通过对Center 模型中Simulink 自带的加法器,比较器的数据属性,计算属性进行修改,并对其中的Matlab Function 模块中数据重新建立定点对象,运算法则改为定点数运算法则之后实现定点模型的转换:图中可见模块间数据已变为定点数据类型。

图4 Centere 模块定点模型

2.3 HDL 模型

并非所有的定点模型皆可转换为HDL 模型,这一点考虑为是否使用了不支持HDL 转换的模块或定点数对象算法的错误设置。而在浮点模型设计之初就考虑到这个问题将给整个过程大幅节省时间。

定点模型转换为HDL 模型主要分为两大内容:一是对定点模型的转换;二是对转换后的HDL 模型进行仿真,以下分两个过程:

(1)定点模型设计成熟时,使用Configuration Parameters对待转换的模块进行编译,此时Simulink 会检测是否有不支持转换的模块,模块的设置是否正确,有没有函数使用错误,定点对象运算属性是否设置正确等。Simulink 成熟人性化的报错有助于用户快速纠正设计中的错误。

(2)生成Verilog HDL 成功后,就是对生成代码的仿真验证。

对生成的代码进行验证可使用两种方法:一种是在硬件设计软件中对生成代码文件添加激励进行仿真;另一种是采用Simulink 与Modelsim 的联合仿真。推荐使用联合仿真,因为采用联合仿真,数据是在Modelsim 中运算,结果输回Simulink,可直接观察波形,便于验证。

在对Centere 定点模型进行检测时,根据提示修改了Stateflow 状态机属性后得到Verilog HDL 设计及联合仿真模型如图5 和图6 所示。

图5 Center 模型Verilog HDL 文件

图6 Center 联合仿真模型图

联合仿真结果如图7 所示,其中每张图的第1 行为HDL 模型输出,第2 行为定点模型输出,第3 行为二者相减比较值,可见HDL 转换正确。

图7 联合仿真

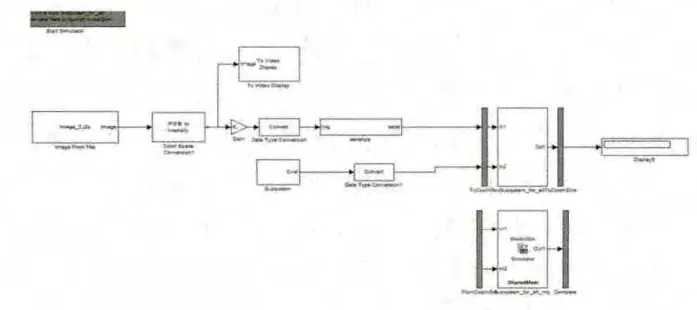

按照相同的方法进行转换后完成对整个绝对位置传感器模型的转换,得到HDL 设计文件,如图9 所示。并如图8 对其建立联合仿真模型以验证转换。

图8 绝对位置计算模块联合仿真模型

图9 绝对位置计算的HDL 设计

由于浮点数据类型向定点数据类型的转换导致数据精度一定的丢失,定点模型输出为50.131 6 mm,原模型输出为50.143 3 mm,定点模型最终输出与原模型误差在0.01 mm 数量级,误差在允许范围内,而定点模型转换为HDL 模型时不存在精度丢失问题,如联合仿真结果图10 所示,HDL 模型输出与定点模型输出一致,故第3 行中二者差值为0。

图10 HDL 与定点模型输出比较

3 结束语

本文提出了一种基于Simulink 的硬件设计方法,其使用Simulink 强大的模块功能及灵活的实际运用性先建模实现功能模块的建立,仿真验证后依据Simulink 中定点数的使用规范,建立定点对象,设置定点对象的运算属性从而将浮点模型转换为定点模型,通过对定点模型进行HDL 转换检测,修改验证通过后自动生成Verilog HDL 语言,建立Simulink-Modelsim 联合仿真模型,利用联合仿真的便利性验证转换并完成了硬件设计。

[1] Yukinobu Sugiyama,Yoshinori Matsui.A 3.2 kHz,14-bit optical absolute rotary encoder with a CMOS profile sensor[J].IEEE Sensors Journal(S1530-437X),2008,8(8):1320-1326.

[2] Wang Yang,Qiu Cheng,Zhu Hengjun.An absolute angular encoder based on m sequence[J].Journal of Electronic Measurement and Instrument,2007,21(2):77-80.

[3] 诸葛俊贵.基于Matlab 模糊控制器HDL 代码的自动生成[J].电子科技,2012,25(1):42-47.

[4] 张慧娟.HDL Coder 和HDL Verifier 支持HDL 代码生成和验证[J].电子技术应用,2012(5):20-21.

[5] 王少飞.基于模型的设计在FPGA 上的一种实现方法[D].成都:电子科技大学,2012.

[5] 陈文艺,杨辉.一种单码道绝对式光学编码器的编解码方法[J].光电工程,2013(6):142-149.

[4] 熊金旺,贾平,刘晶红.利用图像传感器的光电轴角编码器编码研究[J].测控技术,2009(12):6-9.

[8] 刘杰.基于模型设计的自动定制IP 策略[J].浙江大学学报:理学版,2013,11(6):627-633.