三相电压锁相环模块化自动代码生成

2015-03-06杨文焕夏明豪

吴 帅,杨文焕,陈 斌,夏明豪

(上海理工大学 光电信息与计算机工程学院,上海 200093)

在有源电力滤波器(Active Power Filter,APF)、静止无功补偿(Static Var Generator,SVG)、光伏发电、风力发电等系统中,都要准确地对三相电网电压信号进行锁相。目前,软件锁相环一般采用DSP 实现,由于软件锁相环控制算法复杂,所以要占用CPU 一定的资源,并产生滞后影响整个控制系统的响应速度;而采用FPGA 实现锁相环控制以纯硬件的方式并行处理,不仅比软件锁相环运算速度快,而且一旦代码固化完成不会出现程序跑飞的错误,大幅提高了系统的稳定性。然而传统的FPGA 开发流程需要编写大量代码,对开发人员的要求比较高,SG(System Generator)采用基于模型的设计方式,使得对HDL 语言不太精通的系统工程师也可以进行FPGA 的设计开发,SG 在数字信号领域快速普及,但在工业控制领域较少使用。

本文对锁相环基本结构和工作原理进行简单的介绍,然后详细介绍了锁相环每个部分的FPGA 实现,最后在基于Xilinx 的FPGA 控制板上进行试验并给出试验结果,证明了模块化自动代码生成方法的可行性。

1 三相锁相环PLL 基本原理

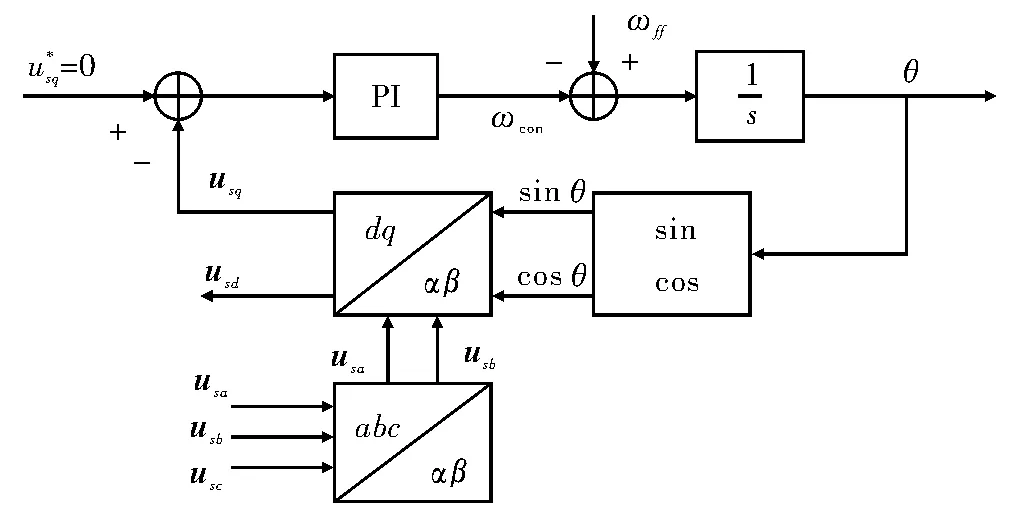

如图1 所示为矢量相位差示意图,电网电压空间矢量us的幅值不变,usq的值随着us与旋转坐标d 轴之间夹角的变化而变化。当usq=0 时,d 轴与us重合,此时计算出旋转坐标d 轴的相位角θ,电网电压矢量us的相位角为θ1,θ1=θ。所以锁相环原理为通过控制dq 坐标系下d 轴分量usq=0,从而实现对电网电压相位的锁定。图2 为该控制算法的实现框图。

图1 矢量相位差示意图

图2 锁相结构框图

2 使用SG 实现PLL 建模

常规使用硬件描述语言的FPGA 开发流程分成代码描述、综合、执行和下载4 个步骤。传统的FPGA 开发流程需要编写大量代码,然后将代码转换成具体的硬件来实现,工作量较大。SG 是Xilinx 公司进行数字信号处理开发的一种设计工具,它将Xilinx 开发的一些模块嵌入到Simulink 的库中,模块化使得设计变得很方便;可在Matlab/Simulink 软件平台上进行系统建模和仿真,并直接导出硬件描述语言及位流文件下载到FPGA;也可以生成HDL 代码作为ISE 中工程的一部分,经过ISE 综合生成位流文件下载到FPGA 芯片。

如图3 所示为SG 环境下锁相环软件仿真整体模型,系统包含SG 与Simulink 接口IN/OUT 模块、Scale 模块、abc-dq 坐标变换模块、PI 模块、积分模块(Subsystem1)以及所有SG 系统中都必须包含的System Generator 模块。

图3 锁相环SG 模型

2.1 FPGA 边界定义模块

SG 是FPGA 实现和算法开发之间的桥梁,通过IN/OUT 模块来定义Simulink 仿真模型中FPGA 的边界。IN 模块标志着FPGA 边界的开始,能够将输入的浮点数转换成定点数。OUT 模块标表示FPGA 边界的结束,将芯片的输出数据转化成双精度数。

2.2 Scale 模块

Scale 模块将A/D 芯片采集的电压信号进行标幺化处理,abc-dq 模块中的运算含有乘法运算,标幺化后的数据均是小数,方便abc-dq 模块中乘法运算数据格式的定义。

2.3 abc-dq模块

根据坐标旋转式(1)用SG 模块搭建abc-dq 坐标变换模型,其中正余弦计算模块选用计算精度较高的Cordic Sincos 模块

2.4 PI 模块SG 模型建立

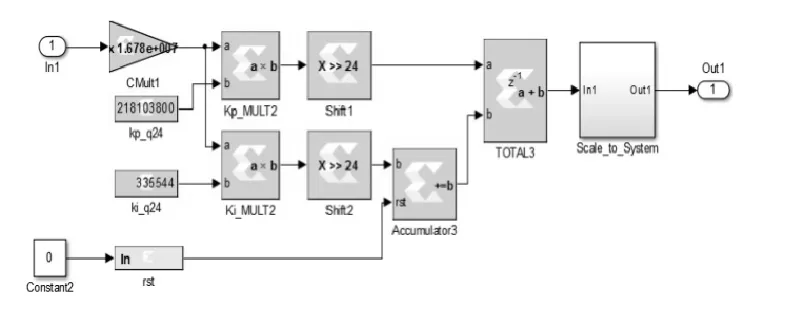

PI 模块SG 模型如图4 所示,比例环节采用Mult模块实现,积分环节用Accumulator 模块实现。Scale_to_System 模块对PI 模块输出进行限幅。

图4 PI 模块SG 模型

2.5 积分模块

积分模块(Subsystem1)即图5 中1/S 模块,这里用加法器和寄存器模块实现积分功能,并将输出结果控制在-π ~π 之间。

图5 积分模块

3 仿真和板级试验结果

图6 所示为SG 环境下仿真结果,图中显示为电网A 电压信号和锁相环输出相位信号,通过调节PI 环节Kp、Ki的值,锁相环锁能在一个周波内准确快速地锁住电网电压A 相的相位角。

图6 SG 模块仿真结果

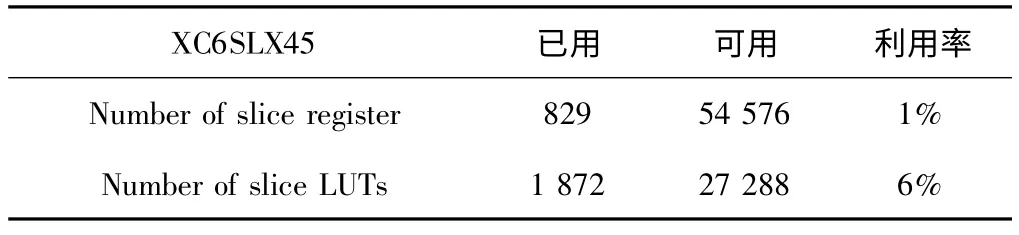

通过SG 可以将搭建好的PLL 模型自动生成HDL代码,并导入ISE 工程中进行板级硬件验证。FPGA 控制板主芯片为XC6SLX45,采用ADS7861 芯片对经过电压霍尔采集到的电网电压信号进行A/D 转换,采样频率为12.8 kHz。采样信号进入FPGA 进行锁相,利用ChipScope 工具对电网电压信号和锁相环输出相位信号进行观测比较。在ISE 工程中除了自动生成的PLL 代码外还需要A/D 芯片驱动程序、ChipScope IP核等辅助程序。表1 为该工程的资源利用情况,统计结果表明,在XC6SLX45 实现PLL 锁相的硬件资源占用率较低,剩余足够的资源实现系统的其他控制算法。

表1 三相PLL 在XC6SLX45 实现资源利用情况

将整个ISE 工程综合并生成.bit 文件经JTAG 口下载到FPGA 芯片,并将运行所得信号通过JTAG 口采集到ChipScope 窗口中显示,电网电压信号和锁相环输出的电压相位角如图7 所示,锁相环可以准确的锁定电压信号相位角。

图7 板级实验波形

4 结束语

分析了3 项PLL 的工作原理,利用SG 对PLL 的abc-dq 模块、PI 模块进行建模,编写了A/D 驱动程序。对生成的HDL 代码进行仿真和硬件验证,ChipScope 对实验结果进行分析表明,基于SG 的三相电网锁相环可以实时跟踪电网电压的频率和相位,证明了利用SG可以简便快速的实现控制算法。目前,基于SG 的设计方法已在控制系统实现中展现了强大的潜力,新的开发方法、设计流程会是复杂控制算法实现的一个方向。

[1] Arruda L N,Silva S M,Filho B C.PLL structures for utility connected systems[C].IEEE Conference Record,2001:2655-2660.

[2] Kaura V,Blasko V.Operation of a phase locked loop system under distorted utility conditions[C].IEEE Transactions on Industry Applications'97,1997:703-708.

[3] Lund T,Aguirre M,Torralba A.Making use of CORDICs and distributed arithmetic to produce a field-programmable fuzzy logic controller in an FPGA[C].Industrial Electronics Society Seville,2002:3205-3208.

[4] Wu Po,Guo Yuhua,Wen Liangyu.Improvement and implementation of one phase power phase-locked loop based on FPGA[J].Power Electronics,2007(4):80-82.

[5] Koh K H,Lee H W,Suh K Y.The power factor control system of photovoltaic power generation system[J].Proceedings of the PCC Osaka,2002(2):643-646.

[6] 邹亮.锁相环技术发展的研究及应用[J].科技资讯,2009(35):147-153.

[7] 纪志成,高春能,吴定会.FPGA 数字信号处理设计教程—System Generator 入门与提高[M].西安:西安电子科技大学出版社,2008.

[8] 姜立东.VHDL 语言程序设计及应用[M].北京:北京航空航天大学出版社,2004.

[9] Xilinx Inc.Xilinx system generator for DSP v3.1 reference guide[M].San Jose:Xilinx Inc.,2003.

[10]Xilinx Inc.Xilinx system generator for DSP tutorals[M].San Jose:Xilinx Inc.,2003.