宽带数字下变频和重采样处理Matlab仿真与FPGA实现

2015-03-06伍小保王冰

伍小保,王冰

(中国电子科技集团公司第三十八研究所,安徽合肥230088)

宽带数字下变频和重采样处理Matlab仿真与FPGA实现

伍小保,王冰

(中国电子科技集团公司第三十八研究所,安徽合肥230088)

宽带数字下变频(DDC)和重采样处理可应用于成像雷达和电子对抗宽带侦查等领域的新型宽带数字接收机设计中,讨论了基于多相滤波结构的宽带DDC和重采样滤波处理的高效实现方式,并通过一个设计实例进行Matlab仿真和FPGA实现,给出了仿真和实现结果,该方法可应用于当前新型宽带数字接收机宽带数字解调设计。

宽带数字下变频;重采样;FPGA;多相滤波高效结构

0 引言

随着成像雷达对分辨率的要求越来越高,相应信号带宽以及数字化的带宽也越来越高[1];电子对抗系统为了提高截获概率要求系统的瞬时带宽也要足够高,相应数字化的带宽也越来越宽[2]。

传统宽带接收系统由于ADC器件以及数字处理器件性能的限制,一般采用模拟I/Q解调后数字化的方式,或者针对LFM信号的系统采用去调频体制来实现宽带到窄带的变换后再数字化[3]。传统宽带接收机由于模拟通道的幅相误差以及其特性随温度的变化造成接收机性能指标受到限制,因此需要通过数字解调的方式提升指标[4]。

随着ADC器件的发展,目前已有12 b/4 GHz(TI公司的ADC12J4000)或10 b/5 GHz(E2V公司EV10AS152A)采样率货架产品出现,同时FPGA资源也已可以满足高速并行数字信号处理的需求,使得宽带高速数字直接解调和滤波处理得以实现。

1 宽带DDC和重采样原理

1.1 宽带DDC处理

常规DDC处理流程是采样/混频/滤波/抽取结构[5],宽带DDC处理一般采样率比较高,因此该结构数字混频和数字滤波处理要求速度非常高,目前FPGA无法直接在高数据率进行处理,不适合宽带高速DDC处理,同时抽取在滤波之后,造成大量运算结果浪费,该结构不适合宽带DDC处理,需要设计适合宽带DDC处理的高效结构[6]。

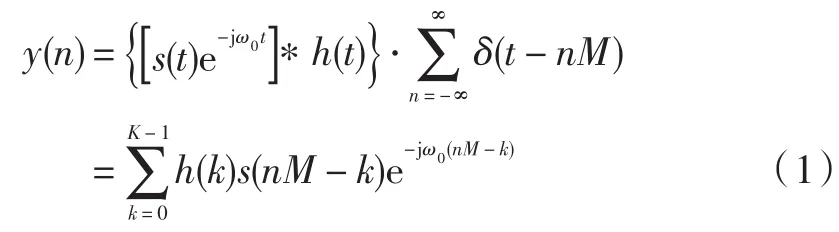

设DDC抽取比为M,数字本振为exp(-jω0t),FIR滤波器冲击响应为h(t),t=0,1,2,…,K-1,常规DDC输出为(采样/混频/滤波/抽取):

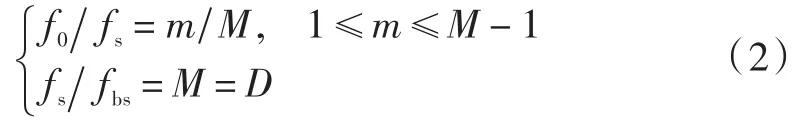

如果采样信号中心频率f0,采样频率fs,基带信号采样率fbs和抽取率D满足关系:

此时数字本振序列exp(-jω0t)可表示为:

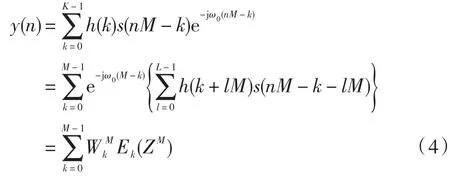

设滤波器系数个数K=M*L,考虑到数字本振序列周期和抽取比相同,DDC输出为:

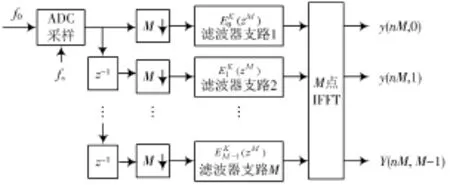

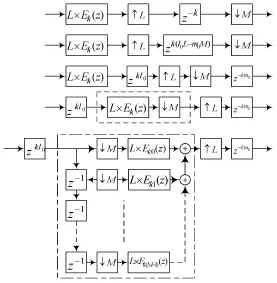

通过选择合适的中频、采样频率抽取比和滤波器系数,保证数字本振周期和抽取比相同,分配到每个多相滤波器支路上的本振信号为常数,因此混频可以放到多相滤波后面,整个DDC实现结构变成采样/抽取/多相滤波/数字混频,功能框图如图1所示。

图1 多相滤波混频后置DDC结构功能框图

多相滤波混频后置DDC结构又称为重采样多相下变频结构,由式(2)可知:

因此当下变频的中心频率f0固定为基带信号采样率fbs的整数倍时,可以保证经过重采样处理后这一中心频率的信号将映射到基带零频上。当该结构用做单信道宽带下变频和减采样处理时,通过抽取/多相滤波后加复数乘积实现相位旋转来获得;当有几路信道进行下变频时,在多相滤波器后应用一组并行的复数相位旋转来完成多路信道下变频输出;当通道数为M=log2N时,滤波后的相位旋转多信道输出可以通过IFFT/IDFT实现,具体实现结构如图2所示。

图2 改进的多相滤波混频后置DDC结构功能框图

1.2 重采样处理

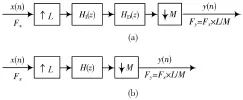

宽带系统中频f0的选择需要根据系统模拟通道的体制、频率窗口的计算、系统瞬时带宽、当前ADC模拟带宽等多个因素来决定;ADC的采样率fs选择需要考虑满足采样定理或者最佳采样定理的要求,这样可以简化数字混频处理,同时也可降低抗混叠滤波器的实现难度,另外采样频率的选择与中频的选择要互相兼顾;DDC处理输出信号采样率fbs一般要求和信号带宽BW相匹配,过低的采样率对后续信号处理会造成SNR损失,过高的采样率会增加后续信号处理的运算资源。中频采样设计时,一般要求fs/fbs的比值为一个整数,但当要求fs与f0匹配而同时要求fbs与BW匹配时,宽带系统会存在fs/fbs比值为分数的情况,这时需要进行重采样处理来获得最终需要的基带采样率。重采样率为L/M的分数采样率变换可以通过图3所示的结构来实现。

图3 重采样实现原理结构和简化结构

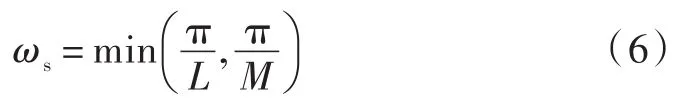

从实现结构看重采样处理是通过(内插器+镜像抑制低通滤波器)+(抗混叠低通滤波器+抽取器),其中镜像抑制低通滤波器和抗混叠低通滤波器可以合并为一个低通滤波器来实现,该滤波器的通带截止频率ωs为:

因此合并的低通滤波器传递函数的幅度相应为:

其中L为补零内插时需要补偿的增益损失。

对于抽取比或内插比为很大的数时,滤波器的通带截止频率非常小,因此滤波器阶数将非常高;重采样由于需要内插处理,因此一般是在基带低数据率复数信号下进行;对于宽带系统,基带数据率也非常高,因此内插比不能很大,否则对资源要求非常高;如果直接利用图3所示结构进行重采样处理,由于先进行内插处理,宽度DDC的重采样滤波压力将非常大。综上所述,宽带DDC的重采样处理在系统设计时分数比的分子和分母都是比较小的互质数,同时还必须采用高效的实现结构来实现。

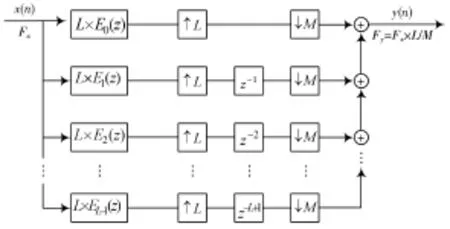

对于图3中所示的简化结构利用FIR滤波器的多相分解(按照内插比来分解)可以获得如图4所示结构。

图4 重采样滤波器多相分解实现

利用Nobel恒等式,多相滤波器和内插可以互换位置,同时抽取可以移到多相分支内部,修改后的结构如图5所示。

图5 改进重采样滤波器多相分解实现

根据数论理论,两个互质的整L和M,存在整数l0和m0满足下式:

利用该等式,延迟单元可以表示为:

图5中一个多相分支利用式(8)对延迟单元进行替代,同时利用Noble恒等式关系进行变换、利用FIR抽取滤波器的多相分解结构进行变换,可以获得如图6所示的高效实现结构。

图6 重采样滤波多相结构第k分支高效实现的分解

从图6可以看出,滤波在最低采样率时进行处理,运算效率最高,与图4相比大大降低了多余运算处理,特别是对于宽带高数据率DDC处理,计算效率大大提高。图4~图6是针对减重采样(L/M<1)的实现结构进行的推导,对于增重采样(L/M>1)的情况,只需要将图6结构的抽取和内插位置互换,同时将抽取和内插相对多相分支滤波器的位置也互换即可。

2 宽带DDC和重采样设计

仿真设计参数要求如下:

(1)信号中频频率:900 MHz;

(2)ADC采样频率:1 200 MHz;

(3)信号带宽:400 MHz;

(4)基带输出采样率:500 MHz。

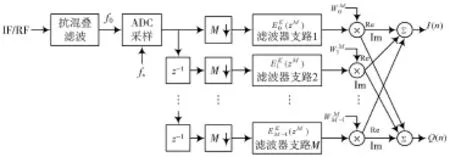

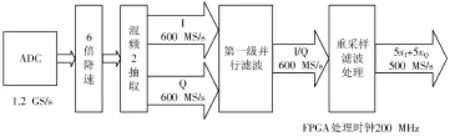

从仿真设计参数要求看采样频率和信号中频满足最佳采样定理,因此数字混频可以得到简化,输出基带采样率为500 MHz与ADC采样频率不成整数倍关系,因此需要进行重采样处理。重采样处理在复数域进行,因此先进行混频滤波处理,获得600 MHz采样率的基带I/Q信号,然后再进行5/6重采样处理,最终输出500 MHz基带I/Q信号。该宽带DDC实现功能框图如图7所示。

图7 重采样宽带DDC处理结构功能框图

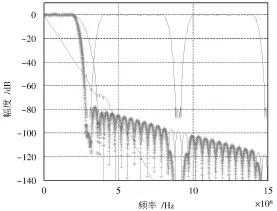

DDC仿真时,为了满足DDC数字混频镜像信号抑制、重采样内插镜像信号抑制的需求,设计的第一级FIR滤波器阶数为47阶,第二级重采样FIR滤波器的阶数为63阶,级联滤波器的幅频和相频特性如图8所示。

图8 DDC和重采样滤波器级联响应

FPGA实现时整个宽带重采样DDC的处理时钟是200 MHz,ADC输入数据6倍降速产生6路200 MHz的中频信号,经过数字混频(符号变换)和抽取后得到两路各600 MHz数据率的I/Q信号(分三路并行输出),第一级FIR滤波器采用3倍资源复用来实现600 MHz的FIR滤波处理,输出I/Q各三路200 MHz的第一级滤波数据,送入图5和图6所示结构的5/6重采样滤波器处理,最终输出500 MS/s的基带I/Q信号。

3 Matlab仿真与FPGA设计结果

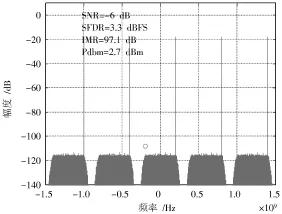

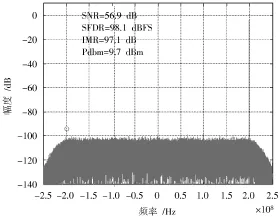

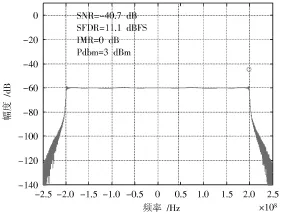

宽带重采样DDC处理的仿真结果如图9~图14所示。单个通道整个处理需要的乘法器数量为352个,对乘法器的需求量比较大,主要是由于面积和实现速度间权衡的结果。

图9 点频输入信号(频偏199 MHz)

图10 第一级滤波输出频谱

图11 宽带重采样内插输出频谱

图12 宽带重采样滤波输出频谱

图13 LFM信号宽带重采样输出频谱

图14 LFM信号宽带重采样输出脉压结果

4 结语

宽带数字下变频(DDC)和重采样处理可应用于成像雷达和电子对抗宽带侦查等领域的新型宽带数字接收机设计中。本文讨论了基于多相滤波结构的宽带DDC和重采样滤波处理的高效实现方式,并通过一个设计实例进行Matlab仿真和FPGA实现,给出了仿真和实现结果。该实现方法的优势和特点是可以减少FPGA的资源利用,降低实现成本和系统功耗。该方法和仿真实现目前已成功应用于某宽带侦查接收机宽带数字正交解调处理和重采样处理。

[1]刘永坦.雷达成像技术[M].哈尔滨:哈尔滨工业大学出版社,1999.

[2]胡来招.雷达侦察接收机设计[M].北京:国防工业出版社,2000.

[3]CAPUTI W J.Stretch:a time transformation technique[J]. IEEETransactionsonAerospaceandElectronicSystems,1971,7(2):269-278.

[4]TSUI J.宽带数字接收机[M].杨小牛,陆安南,金飚,译.北京:电子工业出版社,2002.

[5]伍小保,章仁飞,王冰,等.数字阵列雷达数字下变频器ASIC芯片设计[J].雷达科学与技术,2008(6):496-500.

[6]HARRIS F J.通信系统中的多采样率信号处理[M].王霞,张国梅,刘树棠,译.西安:西安交通大学出版社,2008.

[7]MILIC L.Multi-rate filtering for digital signal processing:Matlab applications[M].New York:Information Science Reference,2009.

[8]MOU Z J.Symmetry exploitation in digital interpolators/decimators[J].IEEE Transactions on Signal Processing,1996,44(10):2611-2615.

Matlab simulation and FPGA implementation of wideband DDC and resample processing

WU Xiaobao,WANG Bing

(The No.38 Research Institute of CETC,Hefei 230088,China)

Broadband digital down-converter(DDC)and resample processing can be applied in the design of new wideband digital receiver in the fields of imaging radar and broadband reconnaissance in electronic countermeasure.The efficient realization way of resample filtering processing and broadband DDC based on polyphase filtering structure are discussed in this paper. A design instance is adopted to perform Matlab simulation and FPGA implementation.The simulation and implementation results are provided.This method can be used in the design of broadband digital demodulation of the new broadband digital receiver.

broadband DDC;resample;FPGA;efficient structure of polyphase filtering

TN957.51-34

A

1004-373X(2015)23-0006-04

10.16652/j.issn.1004-373x.2015.23.002

伍小保(1974—),男,安徽无为人,硕士,高级工程师。主要从事雷达数字化收发系统设计和中频信号处理相关工作。

王冰(1969—),男,安徽六安人,硕士,研究员。主要从事雷达/成像雷达、通信和电子对抗收发系统设计相关工作。

2015-07-16