微震动同步数据采集器的设计

2015-02-28嵇达龙韩瑞瑞顾正东李绍鹏

嵇达龙,韩瑞瑞,孙 磊,顾正东,李绍鹏,陈 迅

(江苏科技大学电子信息学院,江苏镇江212003)

岩体在变形的整个过程中几乎都伴随着裂纹的产生和扩展,其积蓄的能量以应力波的形式释放,从而产生微震动事件.整个过程中的微震动信号从初始阶段就包含了大量关于岩体受力变形破坏以及岩体裂缝活动的有用信息.通过监测、分析微震动事件,可以推断岩体发生破坏的程度、位置,从而实现对岩体破坏的预测预报.上世纪90年代,微震动监测逐步发展并成为一项新的物探技术.由于微震监测范围灵活,定位精度较高,逐渐成为边坡、隧道、矿山和大坝等领域中岩质或混凝土工程结构稳定性监测的主要技术手段.在国外微震监测技术已发展成为采矿安全管理的一个有机组成部分,如在南非、加拿大、澳大利亚等国,已将微震动监测技术广泛应用于矿山安全检测,建立了200余套微震动监测系统.而国内还处于起步阶段,从加拿大、南非等国家进口了少量微震动监测系统,用于凡口铅锌矿、冬瓜山铜矿等少数矿山企业[1-3].随着我国矿山开采深度的日益增加,在高应力作用下诱发的岩爆灾害严重制约矿山生产.微震监测技术通过实时监测岩体破裂情况,可以及时圈定灾害危险区,从而在很大程度上实现灾害的预测和防治,对减少伤亡事故具有十分重要的意义.

文中针对微震动信号的特点,结合高精度数据同步采集、高精度时钟同步、网络通信等技术,设计了微震动信号同步数据采集器,并在此基础上构建了一套完整的微震信号数据同步采集系统.实际应用表明,该系统在信号的测量精度、时钟同步精度等方面具有优异的表现,可满足实际应用的需求.

图1 系统结构Fig.1 System structure

1 系统构成

系统主要由速度、加速度传感器、同步数据采集器、网络交换机、数据服务器和授时服务器几部分构成(图1).其中速度、加速度传感器分别安装在各个监测断面和矿井坑道内,通过差分信号电缆将传感器采集的模拟信号传送到同步数据采集器,每个同步数据采集器具有12个数据采集通道,可以根据实际需要接入速度传感器和加速度传感器,用于岩层断面微震信号的获取.在矿井坑道内,根据需要安装多台同步数据采集器,以扩展监测点覆盖范围.每个同步数据采集器通过工业以太网接入,安装在矿井井口的网络交换机上,网络交换机上行数据端口通过光缆与远端服务器相连,实现数据远程传输.为了保证系统的同步授时,每个同步数据采集器通过专用的网络端口接入网络交换机,通过交换机接入远端的授时服务器,以实现全网同步数据采集器的时钟同步.

系统运行时,速度和加速度传感器将采集的反应微震动的速度和加速度的信号转换成电信号、以差分信号的形式送到同步数据采集器.同步数据采集器完成速度和加速度信号的数字量化、采集数据时间戳的标记以及数据网络传输等主要工作.每个同步数据采集器都有时间计数单元,为了保证所有同步数据采集器的时间的一致性,所有的同步数据采集器都需要与授时服务器通信.一般系统的时钟同步可以采用GPS同步授时,但该系统主要用于矿井内,无法收到GPS信号,不能使用GPS授时的时钟同步方式.因此该系统中采用基于IEEE1588协议的网络时钟同步算法,实现每个同步数据采集器与授时服务器的时间同步,从而达到系统内所有同步数据采集器节点的时钟同步,为数据的同步采集提供高精度时间基准.

该系统中网络交换机选用锐捷RG-IS2712G交换机,其具有8个千兆电口,4个千兆光口,完全满足现场数据传输的需要,远端设有数据服务器和授时服务器.系统中的同步数据采集器为自主开发设计的系统关键设备,文中将对同步数据采集器的结构和设计进行着重说明.

2 同步数据采集器

同步数据采集器内部主要有模数转换单元、数据处理单元、数据传输单元、时钟同步单元4部分组成(图2).

图2 同步数据采集器结构Fig.2 Structure of data synchronous collector

现场的速度和加速度传感器采集的电信号以差分信号的形式通过电缆送到模数转换单元,模数转换电路由12片ADS1282模数转换芯片构成,该A/D芯片的转换位数为32位,最大采样速率为4ksps.电路的12片ADS1282采取4片构成一组,共分成3组完成对12路信号的模数转换.

数据处理单元采用FPGA可编程芯片实现,在FPGA内部将每片A/D芯片送来的32位串行数据转换成32位并行数据,存入FPGA内部设计的FIFO数据缓冲存储区.与此同时将每组数据采集对应的时间值作为时间戳一起存入FIFO数据缓冲存储区.FIFO数据缓冲存储器数据宽度为192位,深度为32个,当FIFO数据缓冲存储区满时,就向数据传输单元发出请求信号.

数据传输单元主要由一片STM32F429微控制器实现,该控制器采用32位ARM内核,从数据处理单元读取数据并通过以太网接口将数据通过网络发送到远端的数据服务器.此外还接收远端服务器发送的控制命令,实现对数据处理单元和A/D芯片的配置等工作.

时钟同步单元主要由一片STM32F107微控制器构成,该控制器也为32位ARM内核.这部分电路主要通过网络与远端的授时服务器通信,实现基于IEEE1588协议的网络时钟同步.

2.1 数据处理单元FPGA实现

数据处理单元主要由ARM总线接口、A/D数据接收缓冲单元、时间戳单元、A/D配置单元4个主要部分构成,电路采用Verilog语言编写设计(图3).

1)ARM总线接口.主要完成FIFO数据读取时序和ARM总线时序的转换,主要将ARM总线的读信号,根据ARM高位地址和片选信号,产生3个A/D数据接收缓冲单元所需的内部FIFO读信号,该FIFO读信号宽度需要严格限定为一个时钟周期.

2)A/D数据缓冲单元.该单元主要由A/D数据读取电路和FIFO存储器构成.A/D读取电路通过一个有限状态机实现,其由空闲等待、串行数据读取、FIFO写入3个主要状态构成.状态机在空闲等待状态下收到A/D芯片的数据转换完成信号后,锁存当前的64位时间戳数据,并将状态机切换到A/D数据串行读取状态,A/D数据串行读取状态由多个子状态构成,在主时钟的驱动下可同时对4片A/D进行数据读操作,每片A/D数据长度为32位,共计128位数据.在串行读取过程中同时实现了数据的串行转并行的转换.32位数据读取完成后,进入FIFO写入状态,在该状态下将串并转换后的128位数据和时间戳数据送到FIFO的数据写端口,同时产生宽度为一个时钟周期的FIFO写控制信号,将数据写入到FIFO存储器.每当FIFO内数据缓存满时,发出存储器满信号通知负责数据通信的微控制器将数据读出.

3)时间戳单元.由时间戳计数器和时间戳配置接口构成,时间戳计数器由64位的微秒计数单元和10位的纳秒计数单元两部分构成,该计数器在100MHz主时钟的驱动下实现10 ns的计数分辨率.

2.2 时钟同步

系统采用了IEEE1588时钟同步协议,该协议将UDP/IP数据包作为消息传递的载体.在系统中,根据发送和接收时间的角色分为主节点和从节点,网络中的所有同步数据采集器作为从节点,授时服务器为主节点.各同步数据采集器与授时服务器进行时钟同步消息的交换,实现与授时服务器的时钟同步,从而实现全网所有同步数据采集器的时钟同步.时钟同步的过程主要分为时钟偏移测量和传输延迟测量两个阶段,时钟偏移测量主要用于修正主从节点之间时钟的偏移;传输延迟测量主要完成从节点与主节点之间的报文传输延迟的测量,以提高修正精度.目前实现IEEE1588时钟同步协议的方式有:①采用 FPGA 的实现时钟同步[4-6];②采用支持IEEE-1588协议的微处理器实现时钟同步[7];③采用支持IEEE-1588协议的以太网物理层控制芯片[8];④采用纯软件方式实现[9].同步精度和实现复杂度两方面考虑,最终选择第二种方案,采用意法半导体的STM32F107VC微处理器实现时钟的同步.

如图4,在STM32F107VC的以太网MAC控制器单元内含有 IEEE1588处理单元,为实现IEEE1588协议的时钟同步提供了硬件支持.该硬件提供两个功能支持:①记录接收和发送以太网帧的时间戳:当以太网帧通过MII端口与物理层以太网驱动芯片进行收发时,IEEE1588硬件模块就会自动记录时间戳,时间戳和数据帧的状态信息一起,存放在相应的描述符里寄存器内;②提供粗调和精调的校正方法.

图4 STM32F107VC以太网接口Fig.4 STM32F107VC network interface

3 系统实现

如图5,数据同步采集器安装在封闭铸铁的壳体内,所有的输入输出信号通过壳体上的插座与传感器相连接.数据同步采集器本体按照IP65防护标准封装,且满足防爆要求.

图5 数据同步采集器实物Fig.5 Data synchronous collector

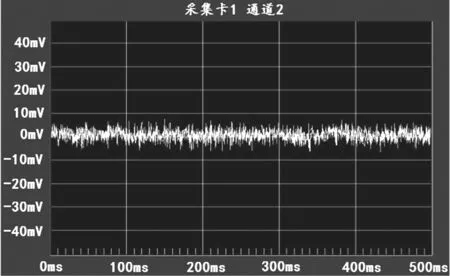

该装置将传感器置于无环境的震动的情况下,数据同步采集器采集的信号波形如图6,其本地噪声的峰值在20 uV以内.传感器接口输入5 V的标准正弦信号代替传感器,大信号激励情况下数据同步采集器采集结果如图7,实际测试转换信号最大幅度为±5 V,测量动态范围可达到约116 dB,完全满足微震动信号的采集要求.

图6 本底噪声采集数据Fig.6 Background noise data

图7 大信号输入采集数据Fig.7 Large signal data

为了测试同步时钟的误差,微震动同步数据采集器和授时服务器均设有同步时钟信号授时脉冲测试端,该测试端输出信号类似于GPS的授时脉冲信号,频率100 Hz,利用安捷伦DSO7052B示波器,同时观察微震动同步数据采集器与授时服务器的授时脉冲测试端,并测量两者之间的时间差.被测设备连续工作6h,每隔30 min捕获测量一次.测量结果如图8,系统的时钟同步误差在±600 ns范围以内,所设计的微震同步数据采集器的设计要求为误差±1000 ns.说明在STM32F107VC微处理器的基础上,实现基于IEEE1588的时钟同步方案,完全可以满足设计要求,达到亚微秒级的同步精度.

图8 时钟同步误差测试数据Fig.8 Clock synchronous error

4 结论

文中构建了微震动数据采集系统,并设计了基于FPGA和微控制器的数据同步采集器,测试结果表明其采集系统的时钟同步精度可达到亚微秒级,可以满足微震动监测的需求.

References)

[1] 李庶林,尹贤刚,郑文达,等.凡口铅锌矿多通道微震监测系统及其应用研究[J].岩石力学与工程学报,2005,24(12):2048 -2053.Li Shulin,Yin Xiangang,Zheng Wenda,et al.Rsearch of multi-channel micro-seismic monitoring system and its application to Faokou lead-zinc mine[J].Chinese Journal of Rock Mechanics and Engineering,2005,24(12):2048 -2053.(in chinese)

[2] 唐礼忠,潘长良,杨承祥,等.冬瓜山铜矿微震监测系统及其应用研究[J].金属矿山,2006(10):4l-44,86.Tang Lizhong,Pan Changliang,Yang Chengxiang,et al.Establishment and application of microseismicity monitoring system in Dongguashan coppermine[J].Metal Mine,2006(10):4l-44,86.(in chinese)

[3] 杨承祥,罗周全,唐礼忠.基于微震监测技术的深井开采地压活动规律研究[J].岩石力学与工程学报,2007,26(4):818 -824.Yang Chengxiang,Luo Zhouquan,Tang Lizhong.Study on rule of geostatic activity base on micro-seismic monitoring technique in deep mining[J].Chinese Journal of Rock Mechanics and Engineering,2007,26(4):818 -824.(in Chinese)

[4] 孔令彬,文赫胜,陈向文.IEEE 1588精密时钟同步关键技术研究[J].计算机测量与控制,2010,18(7):1585 -1586,1598.Kong Lingbin,Wen Hesheng,Chen Xiangwen.Research on key technology of IEEE1588 precision clock synchronization[J].Computer Measurement & Control,2010,18(7):1585 -1586,1598.(in Chinese)

[5] 谢型果.IEEE 1588时钟同步报文硬件标记研究与实现[D].武汉:华中科技大学,2008:1-41.

[6] 方菁.基于FPGA的电力系统时钟同步技术设计[J].武汉职业技术学院学报,2010,9(1):75 -78.Fang Jing.Design of power system clock synchronization technology based on FPGA[J].Journal of Wuhan Polytechnic,2010,9(1):75 -78.(in Chinese)

[7] 吴敏凉,石旭刚,张胜,等.基于IEEE 1588的同步以太网实现方式[J].单片机与嵌入式系统应用,2010(1):38-40.Wu Minliang,Shi Xugang,Zhang Sheng,et al.Synchronous ethernet implementation based on IEEE 1588[J].Microcontrollers & Embedded Systems,2010(1):38 -40.(in Chinese)

[8] 周飞,马强,栾军英,等.基于 DP83640的 IEEE1588协议实现方案[J].价值工程,2012,23:307-309.Zhou Fei,Ma Qiang,Luan Junying,et al.IEEE1588 protocol implementation based on DP83640[J].Value Enginnering,2012,23:307 -309.(in Chinese)

[9] 尤志坚.IEEE 1588协议分析与实现[D].上海:华东师范大学,2009:9-68.