电力线载波信道传输特性测量

2015-02-28杨少峰

杨少峰

(中国矿业大学信电学院,江苏徐州 221116)

把输电网用于通信的研究由来已久,即所谓的电力载波通信,最初是用于高压输电网的自动监控,后来研究范围逐渐扩大到抄表等多个领域,近年来针对家庭网的电力线高速接入则是电力载波通信的一个全新拓展[1-2]。人们对电力载波通信的热衷来自于几个方面,首先,输电网是多条平行金属线结构,理论上这种结构能在相当高的频率下保持低损耗和低噪声,而电能传输和电器噪声只在低频占用很小的带宽,完全可以把多余的带宽作为电能传输的副产品用于通信,与光缆及无线通信相比这种信道资源相当廉价;其次,电网是一个已经建成且分布极其广泛的整体网络,绝大部分电器都能接触到这个网络,通信建立相当方便;此外,电网中的变压器和电能表对通信频率起到阻隔作用,各级网络相互保持独立,这大大增强了电力通信的频率复用功能,也简化了网络维护[3-4]。

电力线的高速互联目的是在配电网和家庭电网上采用OFDM技术实现从几Mbit/s到十几Mbit/s的可靠传输用于internet接入。对这个研究方向,国外早在90年代初就开始了研究,并在近年不断推出各自的产品,最著名的有INTELLON、NOTEL、ABB等公司,并有若干电力公司成功做了internet接入实验[5-7]。国内在2000年左右陆续有单位开始介入这方面的研究,如清华和西交等几所高校,也有若干单位利用国外的芯片做了通信实验,但较系统的高速电力通信技术研究,仍然空白[8-10]。

在通信系统的信道性能研究中,基本参数主要有阻抗、信号衰减和干扰。而由于电力线上的负荷具有多样性和时变性,其信道特性突出地表现为线路阻抗小、信号衰减大、高噪声、干扰强和随机性大等特点,大大增加了通信过程的复杂性[11,12]。为了保证电力线的传输质量并提高通信速率,在选择恰当的信号调制、传送和解调方法时,需要对信道特性有详细的了解。因此,建立对电力线载波通信信道进行信道传输特性分析变得尤为重要。文献[13]对1.6 MHz~30 MHz频带内通过电力线路上传输信号的原理进行了研究,对电力线路的信道特性进行了分析,提出了电力载波具有离散高斯型背景噪声和时变衰减特性的信道模型。文献[14]针对低压电力线载波通信信道所处的环境噪声干扰特点和衰落特性,探讨了符合我国实际情况的典型信道传输模型。文献[15]分析了低压电力线的时变特性、阻抗特性、衰减特性和噪声特性等信道特性,实测了各种特性的波形。同时,针对这些特性,就怎样克服其不利因素,给出了相应的措施。

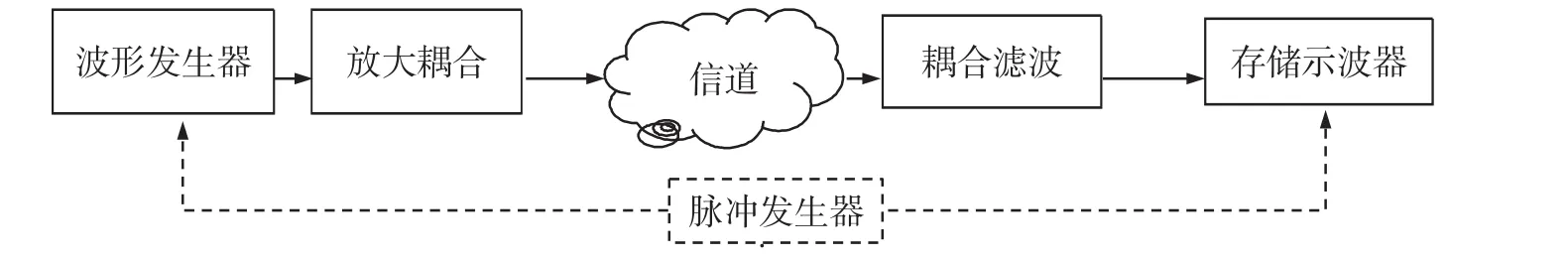

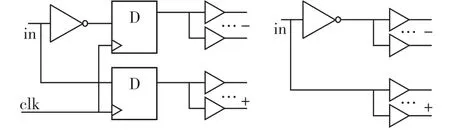

图1 时域测量框图

本文对电力线载波时域测量原理进行了介绍,并设计了一个电力线传输特性测量电路。在数据处理过程中,分析了分段平均和时域加窗对提高总体信噪比的作用,对测量方法进行了验证,并测量了实际的电力信道。实验结果表明,本文的方法有较强的抗噪声能力。

1 时域测量原理

如图1所示,在脉冲发生器的触发下,波形发生器不断产生信号,并馈入信道,再由存储示波器测量端口输出,通过比较确定波形经过信道后发生的变化可以反推出信道传输特性。那么什么样的波形信号适合用于传输特性测量呢,我们设信道传输函数h(t),信号x(t),则通过信道后得到y(t)=h(t)⊗x(t),(⊗表示卷积,下同),变换到频域,Y(f)=H(f)X(f);如果X(f)很宽,在关心频带内没有零点,就可以除得到H(f)=Y(f)/X(f)。频谱宽且在测量频域内没有零点的波形很多,最直接的是冲击函数δ(t),其H(f)恒值,频谱最宽,但冲击函数不易物理实现,所以信号处理时常用窄矩形脉冲代替冲击函数来分析传输函数。

2 时域测量的信号处理及硬件设计

2.1 时域测量的信号处理

配电网的噪声相当复杂,加上信号衰减随距离迅速增加,在很多情况下总体噪声功率会大于信号功率,测量数据不做处理难以满足这个要求。我们采用了两种方法来提高信噪比,即平均和时域加窗,处理过程如下:

(1)平均

所用存储示波器是Agilent 54621D,200 MHz、8 bit采样,一次采样可得4 Mbyte数据[40],采集到数据后,先要运用自相关精确计算m序列周期,再把数据对齐做平均,得到单周期数据,平均可以提高采样分辨率,并降低背景噪声。

(2)时域加窗

得到的单周期数据与发送的PN序列做相关(实际是反序做圆卷积),再滤波得到hcoarse(n),就是粗精度的传输函数,用公式表示:

(3)DFT后校准

对加窗的hcoarse做DFT得到Hrec(f),除以校准的Htrans(f),得到最终结果H(f)=Hrec(f)/Htrans(f)。注意H(f)只在相关频段有效,在频域高端由于信号功率很小相除后结果往往毫无意义,统计相应频段的群延时可分析信道多径性能。我们的测试最终针对OFDM通信仿真,要求h(t)的有效长度尽量短,所以在IDFT得到h(t)前要对H(f)加窗并对窗外H(f)做延拓。

2.2 硬件设计

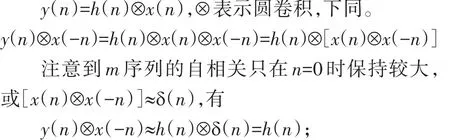

针对系统要求,我们设计了一个电力线噪声和传输测试电路,如图2所示。

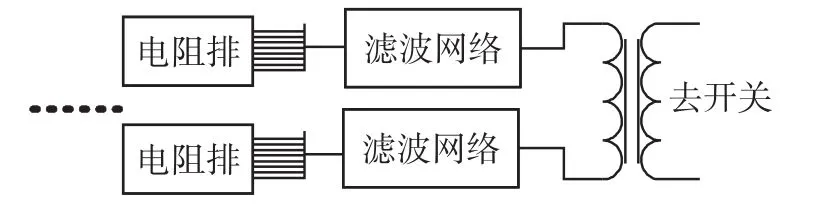

图2 测试电路框图

PN序列由CPLD产生,经平衡不平衡转换,去滤波电路,到耦合变压器,经开关矩阵接到输电网络,接收时,开关矩阵拨到另一个支路,经变压器、滤波网络到负载,负载输出到示波器。

(1)参数选择

首先确定测量频率,这个测量系统本身并不单单针对高速电力载波通信,对100 kHz~500 kHz频段仍然关心,所以系统要求频带大约从100 kHz~22 MHz,加上过渡带,希望能测量50 kHz~30 MHz频率范围内的噪声和传输特性,如果整频域测量,信号起伏比较大,加上示波器的AD位数有限,精度也较差,所以要求分段。考虑500 kHz以下频段的噪声类型与以上频段不同,而且应用类型也不同,同时测量会降低精度,再考虑滤波器实现难度,选择的分段方案是低端 50 kHz~900 kHz,高端900 kHz~30 MHz。电力信道上脉冲噪声的频域很宽,分段会给脉冲噪声分析带来不利,而且精度要求不高时,全频带测量更快速,所以0.05 MHz~30 MHz的滤波器仍然保留。这里的频率分段可以用频率分路器,但考虑到频段太宽,整体不易调节,系统中的各个滤波器都是单独设计的,所以各滤波器不能同时接到线上,要分开测量。

其次确定m序列,m序列发生器有两个重要的参数,一个是脉冲宽度,另一个是m序列级数。设脉宽w,级数m,可以得到周期长度T=w×m,这也是最大可测的多径时延,而频域分辨率或最低可测频率是周期的倒数1/T,最高可测频域则由脉冲宽度决定,例如取sinc函数的3 db宽度则最高频率fmax=0.44/w,对我们的系统要求测量 50 kHz~30 MHz,可以计算得到,w<44/30 us,或工作频率要大于30/0.44=68×106MHz,考虑常用晶振频率以及芯片速度,选50 MHz,这样可以比较稳定地测量到22 MHz,同时22 MHz~40 MHz频段也可测量。对m有log2(m)>50 MHz/50 kHz=1 000,得到m>10,长的m序列能更好地抑制窄带噪声,而对1 MHz以上的频段,电力线噪声主要是无线电广播噪声,属窄带噪声,所以我们最终选m=13,序列长8 k。这个配置能一次完成整个频域的测量,但考虑到分段测量时,50 MHz的工作频率对低频段测量泄漏太大,效率过低,应选另一组参数m=10,f=50/24约3 MHz,这在CPLD程序中是通过分频获得的。

(2)电路设计

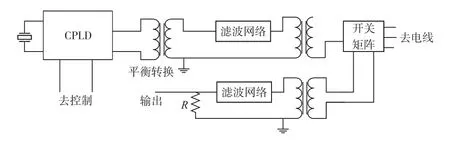

先选CPLD芯片,为简化设计,我们的电路没有使用功率放大器,m序列发生器产生的数字信号要有足够的功率来驱动负载,一般电力线的阻抗在高频约100 Ω,对应5 V的电源电压,最大驱动电流需要50 mA,TTL引脚输出的驱动能力一般小于8 mA,需要选取其他能提供较大驱动电流的芯片,我们最后选用了xilinx的XC9536-15[42],它单个引脚的输出电流达24 mA,抗烧毁电流50 mA,比较皮实,而且在同类芯片中它是较便宜的。但24 mA的电流仍然不能满足系统要求,而且0~5 V的电压范围也不够,为此我们采取了两个措施,先是用差分提高输出电压的摆幅,再把多个引脚并联增加输出电流。XC9536有44个引脚,其中34个引脚可编程使用,为了布线紧凑降低延时,选择两个边上的引脚作为输出,正负相各8个。实际输出电路如图3所示。

图3 输出脚差分并联

在很多文献中,不推荐使用以上这种把输出脚并联的做法,问题就在于输出脉冲不可能精确同步,脉冲到达总有前后,而且分布不可预测,一般芯片的输出引脚阻抗很低,例如XC9536的零电平输出阻抗小于10 W,如果脉冲边沿有冲突就会产生很大的电流把芯片击穿。为解决这个问题,我们采取了多个措施,首先在每个输出引脚串联一个180 W电阻,这样保证引脚电流小于5/180=28 mA;其次把差分引脚轮换排列,使芯片的散热比较均匀,最后把多余的引脚全部接地,保证接地可靠,灌电流通畅。设计时还在并联后加入一个上拉电阻,用来补偿引脚高电平输出较低电平弱的情况,串联电阻后系统输出阻抗增加,好在有8个输出并联180/8=22.5 W,加上差分,可以保证系统输出阻抗在50 W左右,准确的输出阻抗还和引脚电阻有关,不容易精确设定,电路设计有一个冗余的串联调节电阻。

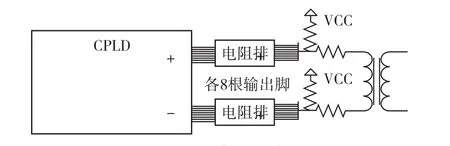

差分输出是提高输出电压能力的常用做法,设单电源工作的引脚输出0~aV,用差分输出可以扩大输出范围到-aV~+aV,同时输出阻抗增加一倍。我们的电路要求输出阻抗恒定,但数字电路的引脚在高电平输出时的阻抗较第电平输出时的阻抗要大很多,用差分输出也可以解决这个问题。XC9536本身并不带差分输出,设置差分时要仔细考虑芯片延时,XC9536-15的tCOI(寄存器输出时间)<0.5 ns,tOUT(输出缓冲时间)<4.5 ns,两者的和就是内部时钟上升沿到引脚输出的总时间t<5 ns,相信各输出延时的离散性要比这小得多,例如0.5 ns,甚至比边沿时间小,而50 MHz时钟的脉冲周期有20 ns,0.5/20=2.5%,这可以忍受。差分工作的编程要特别注意,组合输出是不允许的,一定要采用统一时钟控制的寄存器输出,如图4所示。

图4 组合输出和寄存器输出的比较

上图右电路的两个输出总是差一个反相器延时,而XC9536反相器延时达3 ns,这无法忍受。

CPLD输出后先做平衡不平衡转换,这地方还有另一种选择,如图5所示。

图5 另一种平衡不平衡转换选择

与原来电路相比少一个变压器,多一个滤波网络,原来的平衡转换功能在耦合变压器上实现,在PCB板上,用表贴元件构成的滤波网络体积比一个变压器小,变压器安装也不方便,理论上以上电路也是可以的,问题是这个电路从输出到平衡转换中间要经过滤波网络,而滤波网络元件很多,元件的容差范围不能保证整个频段都相位平衡,而差分电路对相位平衡非常敏感,要尽量保证平衡传输时线路简单,所以没有用这个电路。

电路中的滤波网络使用变形的带通Chebyshef LC无源滤波器,即5阶高通加6阶低通,要求网络的相位延时要尽量小,这一方面因为多径延时是重要的测量指标,同时,附加的多径延时也会降低数据处理的精度,此外对网络驻波也有较高要求。这是个滤波输出电路,要选用高精度、高Q值和大电流容量的电感电容。

电路最后用变压器串联电容耦合到电力线网络,这里使用了传输线变压器,因为信号相对频带很宽,一方面低频传输要求电感较大,如12 mH,另一方面高频传输要求漏感小,耦合系数大。这里接触到220 V工频,变压器绕制要非常小心,变压器的磁芯要选用高频材料,如锰鋅类。电路最后是耦合电容,要求损耗小。

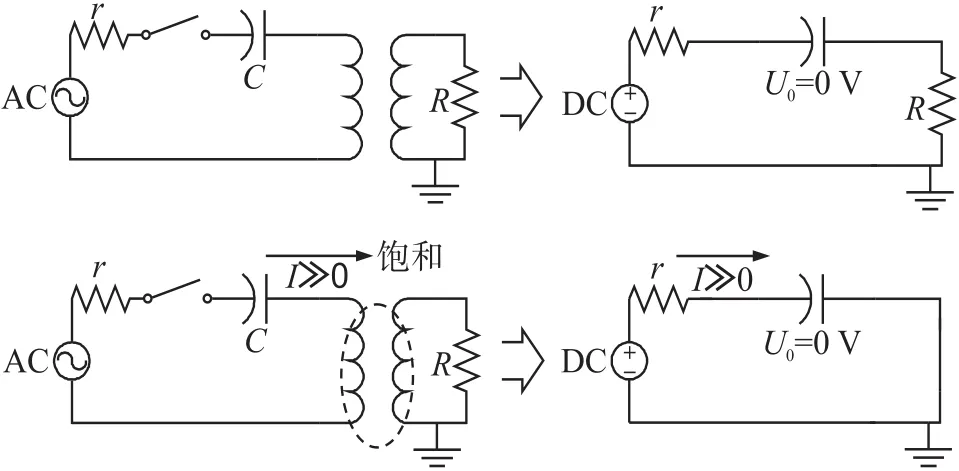

电力信道的脉冲干扰非常恶劣,同时电容耦合电路在加电时存在固有的电压冲击,图6展示上电时耦合器的等效电路。

图6 上电时耦合器的等效电路

在电路接通的瞬间,电容电压为零,在耦合变压器饱和前,电感很大等效为理想变压器,这时相当于r和R串联分压,而线路电阻r很小如0.n Ω,所以开机瞬间,负载可能要承受超过200 V的冲击,这个冲击在各级电路中消耗衰减,但输出端仍旧很大。如果负载较小,会产生较大电流,使耦合变压器的磁芯饱和,电感瞬时变小,相当于短路,耦合电容直接搭在220 V线路上,这时产生的冲击电流很容易烧毁电容。

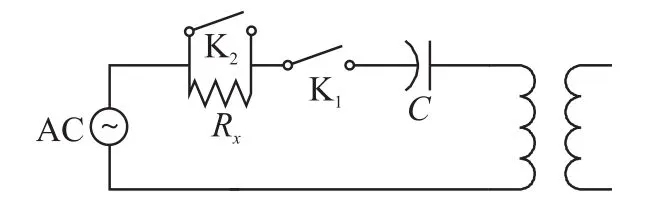

为了解决这个问题我们设计了一个开关序列,如图7,开机时先闭合K1,使C充电到与AC同步,因为这时有Rx电阻串联,电流较小,冲击不大,然后闭合K2,这时C有较大的初始电压,电压冲击较小。优化Rx使两次冲击大小相当,可以取得最佳效果。

图7 开关序列

电路后端也要加保护,特别是XC9536,其输出脚的极限电压只有-0.4 V~VCC+0.4 V,即-0.4 V~+5.4 V,相当小,在平衡转换前加钳压二极管并同上拉电阻构成第1级保护,再在滤波网络中间加一对肖特基稳压二极管构成第2级保护,二极管加在这里是因为,一方面冲击脉冲离耦合器越近就越尖锐,二极管保护的效果就越好,另一方面,离耦合器太近工频和低频噪声容易串到二极管,引起二极管电容变化,影响滤波网络参数,造成虚假的传输时变性。经过这些保护后,电压冲击减小到了安全水平。

图8是改进后电路的电压冲击,测量的是全通滤波器输出,没有加第1级保护,电压幅度仍然比较大,更高分辨率的图显示第2级保护二极管已起到限幅效果,相信K1闭合时耦合变压器输出脉冲幅度可能超过20 V,图中还可以看到由于机械跳动,一次开关动作可能会有几个依次衰减的大脉冲,这种现象也在噪声测量时被观察到。

图8 改进后电路的电压冲击

4 实验结果

4.1 测量方法的抗噪声能力仿真分析

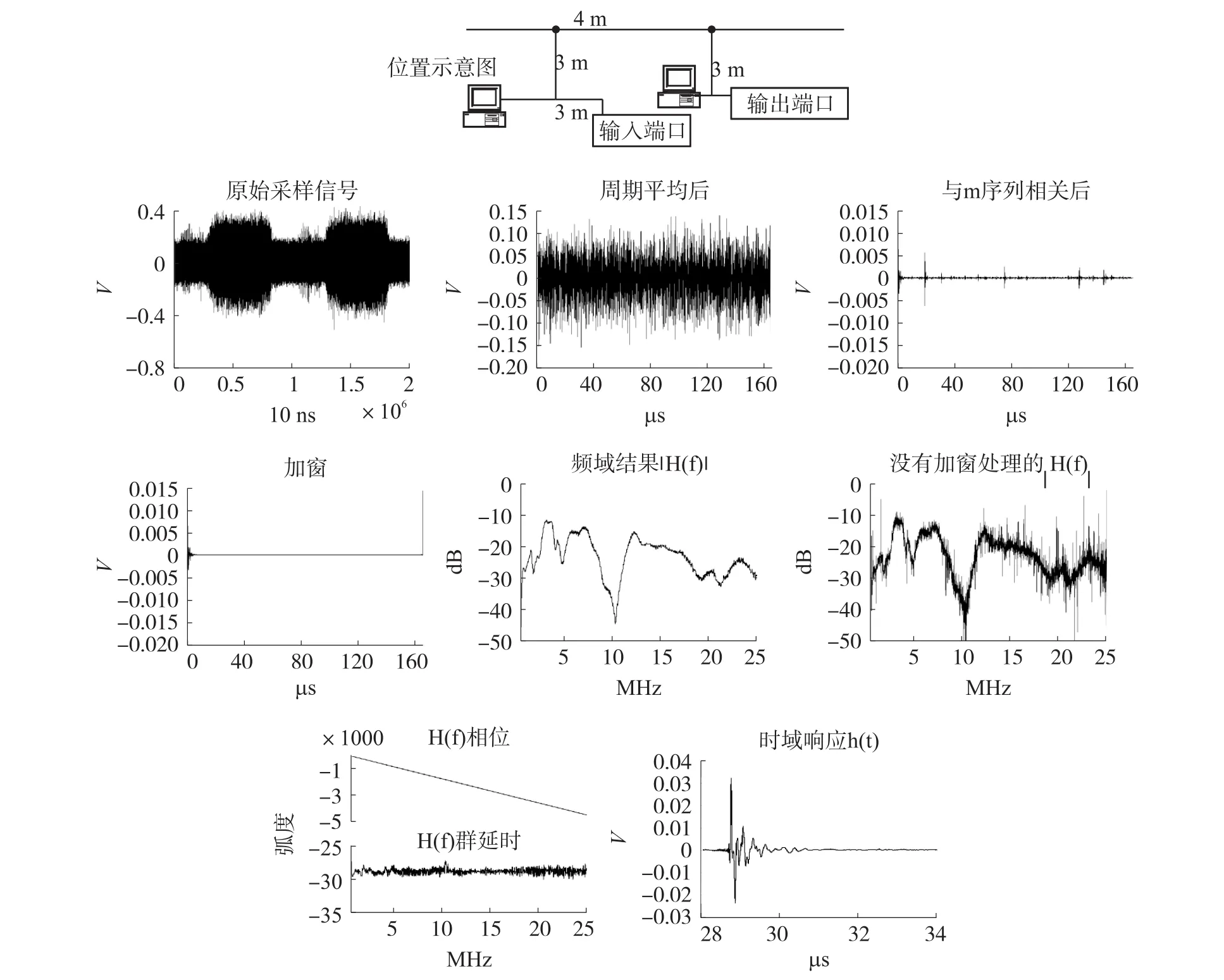

为研究测量方法的抗噪声能力,我们测量了实验室中两个插座间的传输特性,插座相距13 m,网络上有数台计算机,以下是0.5 MHz~25 MHz频段的测量和分析结果。

从图9中可以看到原始采样数据的噪声很大(主要是开关电源的噪声,噪声分布模式与50 Hz工频同步),但经过处理,测试结果保持良好的精度。可见,在配电网的实际噪声环境下用PN序列测量传输特性是可行的。

图9 实验室两个插座间的传输特性测量及其处理过程

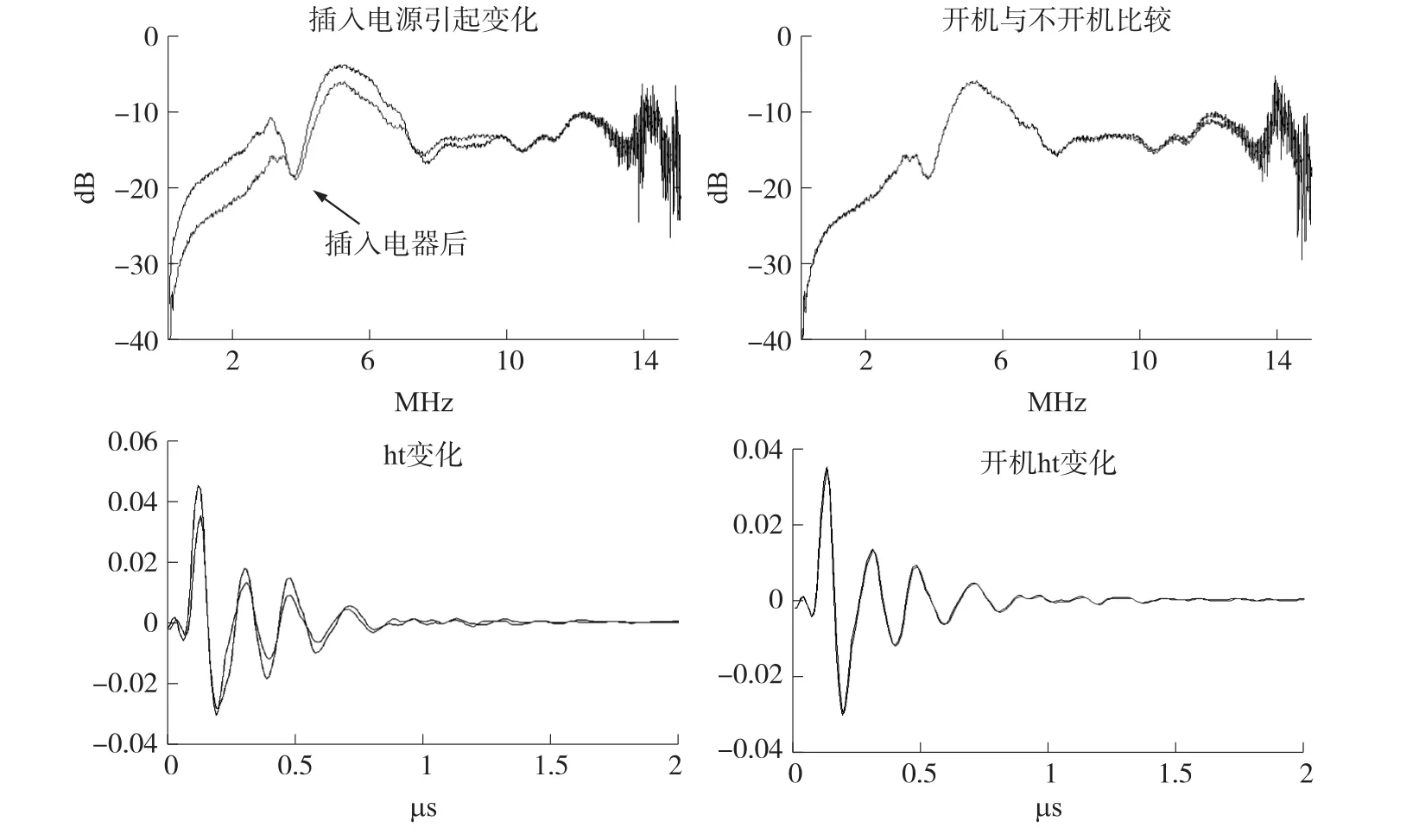

图10分析信道的时变性,两个端口相距5 m,在某个时刻接入一台计算机,并随后打开,观察这个过程中传输特性的变化,计算机标称功率约200 W,采用非全关断式电源设计,如图10所示。从图中可以看到,插入电源线引起的影响比较大,开关电源设计比较合理,开机的影响较小,但输入电感较小,低频衰减较大。

图10 接入电器对传输的影响

4.2 阻抗测量

信道阻抗和传输特性紧密相关,调制解调器的模拟前端设计需要知道阻抗特性,电力信道的阻抗是时变的,为充分提高功率利用率降低信道传输衰减,也有设计采用时变耦合器,通过估计跟踪使耦合器与信道保持匹配[43]。因为是单点测量,同时阻抗测量对相位要求很高,最好的测量方法是使用矢量网络分析仪,采用一些技巧,也能在时域测量,但精度较低。测量框图如图11所示。

图11 时域阻抗测量

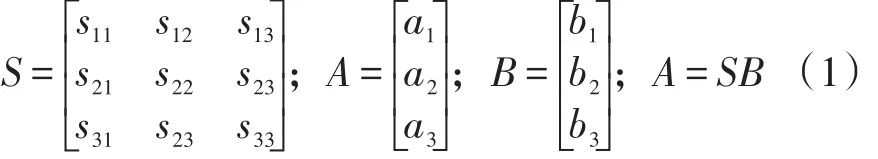

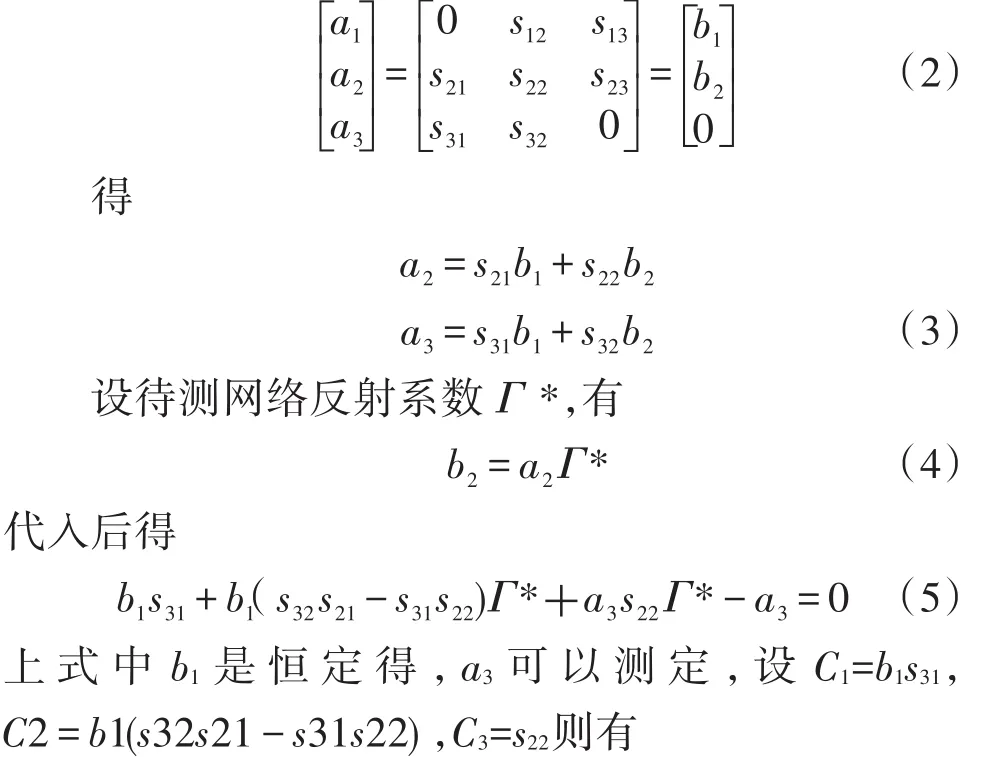

把输出网络与输入网络并联接在测量端口上,测试步骤是这样的:先在测试端口上接已知元件,如50 Ω电阻,测得几组校准值,再接上待测网络测得输出,最后计算出端口阻抗。注意到阻抗测量对相位要求严格,存储示波器要接同步。这个方法可以用串并联理论分析,但考虑到实际系统的测试端口比较复杂,往往有一段长线,存在寄生参数,串并联理论不精确,所以采用三端口网络精确描述,这个三端口网络包括整个耦合网络和端口,端口顺序见上右图。设三端口网络的散射矩阵S,输入波向量B,输出波向量A,有

又设,1、3端口匹配,这总是可以达到的,因为3端口是一个纯电阻负载,可以用它来做归一化阻抗,1端口实际在网络内部,通过分割也能得到相同的电阻负载做归一化阻抗,那么就有,s11=0,s33=0,以及b1恒定,b3=0,代入A=SB得到

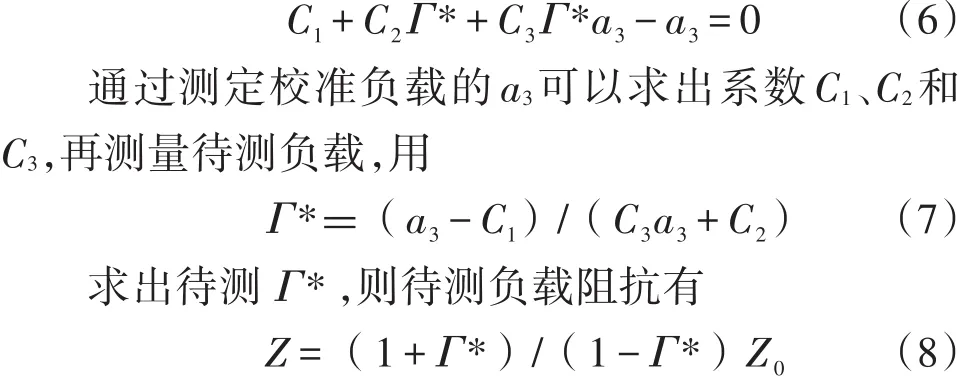

图12是一组测量结果,在8 MHz处,耦合器谐振,结果不准确。

图12 阻抗测量结果

5 总结

分析了时域电力线载波信道传输特性测量的原理,,并对它的数据处理过程做了详细分析,强调分段平均和时域加窗对提高信噪比的作用,最后设计了电路,通过测量已知电路证明方法是可行,同时实验室环境下的实测结果还表明,方法有较强的抗噪声能力。

[1]张艳,陈忠辉.PLC信道特性分析及建模仿真[J].电力系统通信,2012,33(238):46-50.

[2]闫磊,常海娇,许鸿飞.中压电力线载波通信现状及发展趋势探讨[J].2014,12(1):12-16.

[3]黄银龙,蔡伟,毛涛.具有格状网的电力线载波通信信道特性的分析[J].电力系统保护与控制,2014,42(11):1-6.

[4]戚佳金,陈雪萍,刘晓胜.低压电力线载波通信技术研究进展[J].2010,34(5):161-172.

[5]李建岐,陆阳,赵涛等.新一代电力线载波通信关键技术探讨[J].2013,12(11):1-5.

[6]赵刚.电力线载波通信的研究[J].广播电视信息,2013,252:67-69.

[7]孔思豪.电力线载波通信技术的发展和应用[J].企业技术开发.2013,32(20):129-130.

[8]候兴哲,徐信.一种低压电力线载波通信测试仪[J].自动化与仪器仪表.2013,(4):100-103.

[9]杨艳.关于电力线载波通信技术的分析[J].信息技术,2013,23:76-77.

[10]马建旭.高速电力载波通信信道传输特性的研究[D].东南大学,2013.

[11]张艳,陈忠辉.PLC信道特性分析及建模仿真[J].电力系统通信,2012,33(238):46-50.

[12]沈卓君,蒋存波,刘电霆.电力载波技术研究初探-电力载波原理及信道特性[J].桂林工学院学报,2003,23(4):420-422.

[13]孙秀娟,罗运虎,刘志海.低压电力线载波通信的信道特性分析与抗干扰措施[J].电力自动化设备,2007,27(2):43-46.

[14]赖征田.电力线载波信道特性研究及仿真[J].电力系统通信,2010,31(216):39-42.

[15]仲元昌,杨洁,曾孝平.低压电力线的信道特性[J].重庆大学学报,2002,25(9):29-31.

杨少峰(1966-),男,河南省洛宁人,讲师,研究方向为机电一体化,电力传输控制等。