基于门控结构的低功耗扫描测试方案*

2015-02-28祝雪菲张万荣万培元王成龙靳佳伟薛宝华

祝雪菲,张万荣*,万培元,王成龙,靳佳伟,史 岩,马 威,薛宝华

(1.北京工业大学北京市嵌入式系统重点实验室,北京 100124;2.北京市公安局公安管理局,北京 100034)

随着数字集成电路复杂度和集成度的不断增加,芯片上单位面积晶体管数目急速增长,伴随而来的是更高的测试频率以及更长的测试时间,这造成了测试过程中更为严重的高功耗问题[1]。测试功耗过高,是芯片可测性设计(DFT)过程中非常棘手的难题,主要体现在以下几个方面:首先,过高的测试功耗导致芯片温度升高,可能会导致芯片衬底、连线的结构发生损坏,所以需要高成本封装来增强散热能力;其次,过高的温度会影响信号的传输,容易造成测试响应数据的错误,甚至会导致整个测试的失败;第3,过高的测试电流会引发严重的电迁移问题,造成了金属线的损毁,引起芯片的失效或缩短芯片的使用寿命。第4,测试功耗还影响着芯片的封装成本,在封装过程中为了克服测试所带来的额外功耗,必须采用散热性好的高成本封装[2]。由此可见,测试功耗过高的问题给芯片测试带来了严重的威胁,如何降低测试功耗成为可测性设计技术中一个关键的设计考虑[3]。在芯片可测性设计中进行功耗优化对于改进电路可靠性和降低封装成本等问题是至关重要的。

1 扫描测试基本原理及其功耗分析

1.1 扫描测试基本原理

扫描测试具有结构简单、对芯片面积影响小、覆盖率高以及可以与EDA工具紧密结合的特点,是目前应用最为广泛的芯片可测性实现方法[4-5]。

Synopsys的DFT Compiler可以在综合过程中将测试电路中的普通触发器转换为自带多路选择器的扫描触发器,并将其级联成扫描链(Scan Chain),可以将测试激励串行移入扫描链中,并将测试响应串行的移出扫描链[6]。

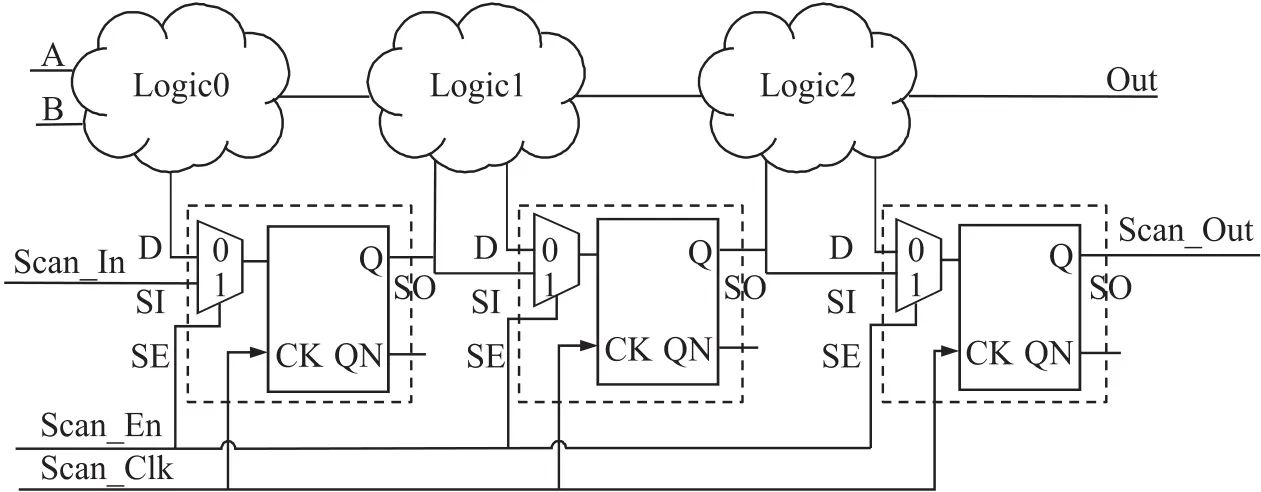

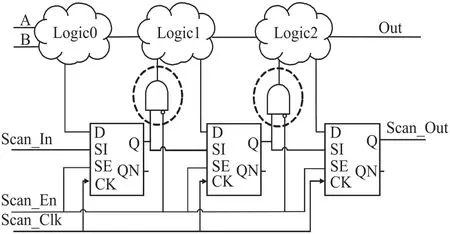

扫描测试基本原理如图1所示,虚线部分由多路选择和触发器组成,即扫描触发器。通过Scan_En信号控制多路选择器的使能端。正常模式时,Scan_En置0,多路选择器选通触发器的D端,扫描触发器等效于一个普通的、不带扫描功能的D触发器,屏蔽掉Scan_In的输入,按照电路本身的逻辑关系正常工作;测试模式时,Scan_En置1,多路选择器选通触发器的SI端,屏蔽掉D端的输入,把所有触发器与逻辑电路断开,形成移位寄存器结构,此时触发器的状态由Scan_In设置,并可由Scan_Out输出观察到。

图1 扫描测试电路

基于上述原理,整个测试过程为:

(1)设置Scan_En为1,通过Scan_In给移位寄存器串行移入测试数据,将扫描链上的扫描寄存器初始化;

(2)设置Scan_En为0,在原始输入端A、B施加测试信号,测试信号加载到组合逻辑上,并行检测原始输出的信号;

(3)运行一个或多个时钟周期,将组合部分测试响应锁存至扫描触发器中;

(4)设置Scan_En为1,通过Scan_In串行移入下一组测试数据,通过Scan_Out查看测试结果。

重复步骤(2)~步骤(4),直至所有测试数据都得以施加。

综上所述,扫描测试可以简单的分为两种模式:移位模式和捕获模式。移位模式下,测试数据从扫描输入端口,通过扫描链被逐位移入扫描单元,从而使它们得到需要的测试激励;而在捕获模式下,扫描单元将测试激励传递到组合逻辑电路并捕获得到测试响应,最后再通过移位模式下移位操作,将测试响应通过输出端口传出芯片并进行观察。

1.2 扫描测试的功耗分析

由上一节的介绍可知,根据扫描测试的不同阶段,可以将扫描测试分为移位模式和捕获模式,对应于扫描功耗也应分为移位功耗和捕获功耗[7]。移位功耗是由于移位过程中相邻扫描单元之间的测试向量逻辑值不同而引起的信号翻转造成的;捕获功耗则是在捕获一拍的前后,同一个扫描单元内测试激励与响应数据之间的逻辑值不同引起的信号翻转造成的。

移位功耗往往更受到设计人员的重视,主要是由于以下的原因:

(1)移位模式占据整个测试模式绝大部分时间,除捕获阶段的几个周期以外,整个测试阶段都工作在移位模式下,因此电路在测试模式下的平均功耗由移位功耗决定;

(2)在多个芯片并行测试的情况下,如果每个芯片的平均功耗升高,会造成能够同时测试芯片数目的减小,导致测试时间增加,测试成本上升;

色谱条件:流动相A为0.4% 醋酸-水(V/V),B为乙腈.洗脱梯度:0~15 min,5%~18% B;15~32 min,18%~28% B.流速0.8 mL/min,紫外检测波长280 nm,进样量:20 μL.柱温箱温度25℃.色谱柱:Waters Symmetry C18色谱柱(250 mm×4.6 mm, 5 μm, Waters, Ireland).

(3)由于移位过程持续的时间较长,在移位过程中产生的热量会不断积累,可能造成测试状态不稳定,造成测试结果错误,降低芯片的良率。同时,长时间的高温会加速芯片的老化,影响芯片的使用寿命。

因此,为了降低测试成本,保证测试结果的正确,提高芯片的良率,本文着重解决移位模式下功耗过高的问题。

2 门控扫描时钟方法

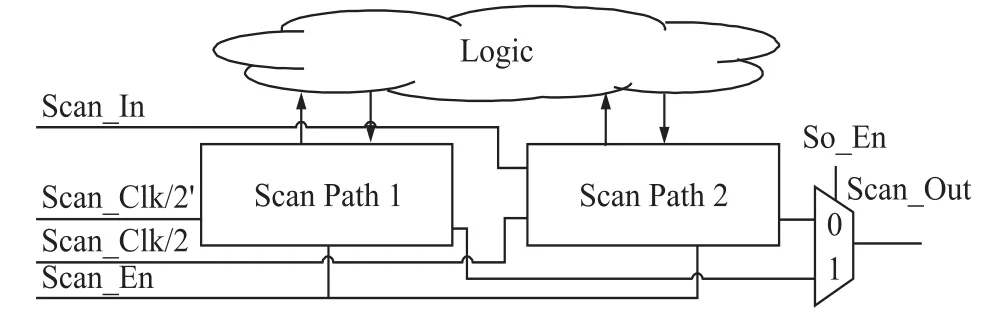

降低扫描链上的时钟频率,可以降低芯片的测试功耗。门控扫描时钟方法,使得扫描链上的扫描时钟频率变成测试时钟频率的一半,保持测试总时间不变,并且不改变测试覆盖率和不影响电路的性能,面积开销也可以忽略不计。具体的实现方法如图2所示。

图2 门控扫描时钟结构

Logic是组合逻辑,Scan_En是扫描使能端口,Scan_In是扫描输入端口,Scan_Out是扫描输出端口。两个扫描路径的时钟之一可以复用系统时钟端口,两条扫描路径的扫描输出通过一个多路选择器输出到原本的扫描输出端口。与图1传统的扫描路径结构相比,修改之处在于:(1)修改了扫描路径的时钟;(2)在扫描输出端插入一个多路选择器;(3)把扫描链上的扫描单元分成路径1和路径2。具体的扫描路径如图3所示。

图3 扫描路径

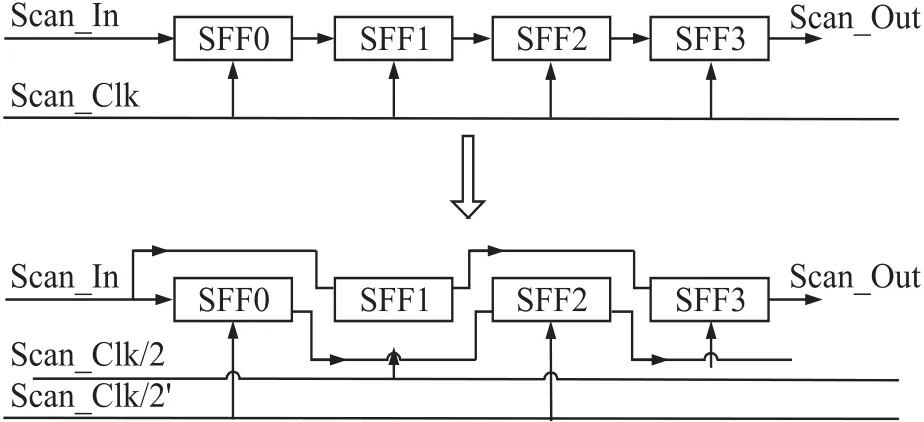

假设某条扫描链上包含4个扫描单元SFF0、SFF1、SFF2、SFF3,扫描时钟端口为Scan_Clk。测试时钟通过Scan_Clk端口施加。在本文提出的方法中,该条扫描链被分割成两条路径,称为路径1和路径2,分别包含SFF0、SFF1和SFF2、SFF3扫描单元,并分别采用扫描时钟Scan_Clk/2’和Scan_Clk/2进行控制。

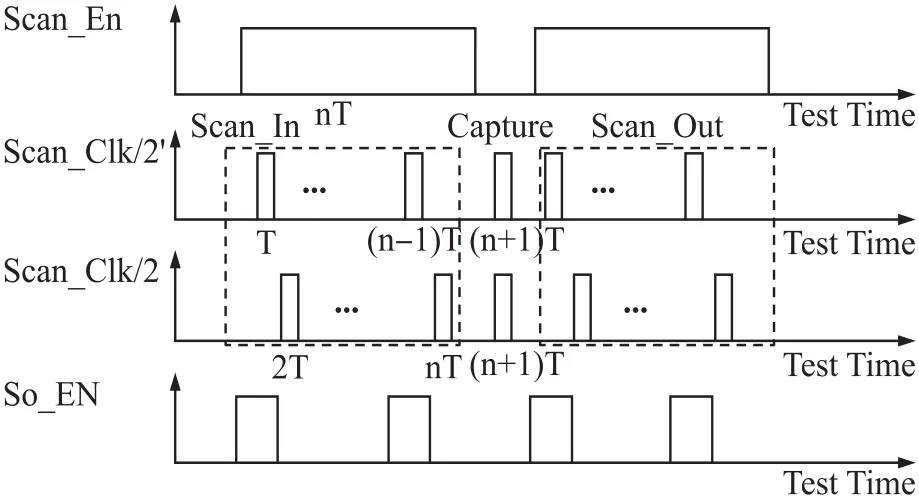

由于Scan_Clk/2’和Scan_Clk/2都与系统时钟同步,在扫描操作的时候,具有相同的时钟频率,都是测试时钟的一半,而且由于它们的相位差为半个测试时钟周期,路径1和路径2不会同时处于有效状态。测试期间的时序波形如图4所示。

图4 门控扫描时钟的时序波形

在扫描链上,在一个时钟周期T内,路径1处于移位状态,路径2处于闲置状态;而下一个时钟周期内,路径2处于移位状态,路径1处于闲置状态。而在捕获期间,该两个扫描时钟以测试时钟运行。在扫描移位输出的时候,通过控制信号So_En使多路选择器每个时钟周期交替输出路径1和路径2上的测试响应。由于在扫描移位期间,扫描链上只有一半扫描单元发生翻转,即该门控结构大大降低了扫描翻转的密度,因此扫描功耗大大降低。同时,在每个时钟周期上,连接到组合逻辑部分的输入只有一半发生翻转,因此组合逻辑电路上的功耗也降低。为了进一步降低组合逻辑电路上的功耗,本文还采用了门控组合逻辑方法,具体见下节。

3 门控组合逻辑方法

如果可以在扫描测试的移位过程中,有效地隔离开触发器的输出端和相连的组合逻辑,使得组合逻辑部分不随扫描单元逻辑值的变化而翻转,将会从根本上降低移位功耗。通过门控结构屏蔽移位过程中组合逻辑的输入是降低这一过程功耗的有效方法。

在所有扫描单元和组合逻辑之间添加阻隔逻辑,并使用Scan_En信号进行控制。这样当电路运行在移位过程中时,阻隔逻辑将这两部分分隔开来,使得组合逻辑部分不随扫描链中逻辑值变化而翻转。而当电路运行在捕获模式时,阻隔逻辑再将这两部分连通,这样就在不影响测试的条件下降低了测试功耗。具体的实现方法如图5所示。

图5 门控组合逻辑结构

门控组合逻辑结构是在触发器的Q端增加门控电路,使组合逻辑的输入在移位模式下处于固定值。Scan_En=1芯片处于移位模式,和此信号相连的与门输出则恒为0。对于组合逻辑,如果所有输入的信号全部固定,那么组合逻辑将处于稳定状态,不随扫描链中逻辑值变化而翻转,动态功耗为零,从而达到优化的目的。

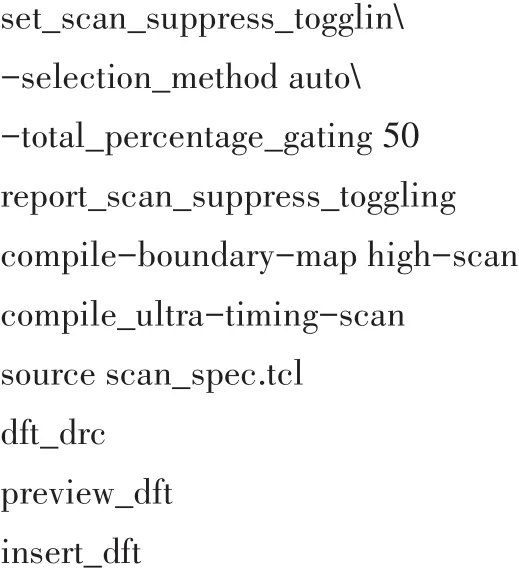

使DFT Compiler工具分析出需要插入门控结构的电路节点,并且选择与门或者或门进行插入操作。具体的语法是:

在这一命令中的total_percentage_gating的数值可以根据需求可以选择门控结构的替换比率,越大的替换率对于动态的功耗优化效果越明显,但同时额外增加的逻辑单元数量越多,若要保持芯片面积不变,可能会出现布线拥塞的问题。

通过report_scan_suppress_toggling可以报出具体的门控信息,折中考虑功耗与布线拥塞的问题,并且多次尝试得到满意的结果。

4 实践结果分析

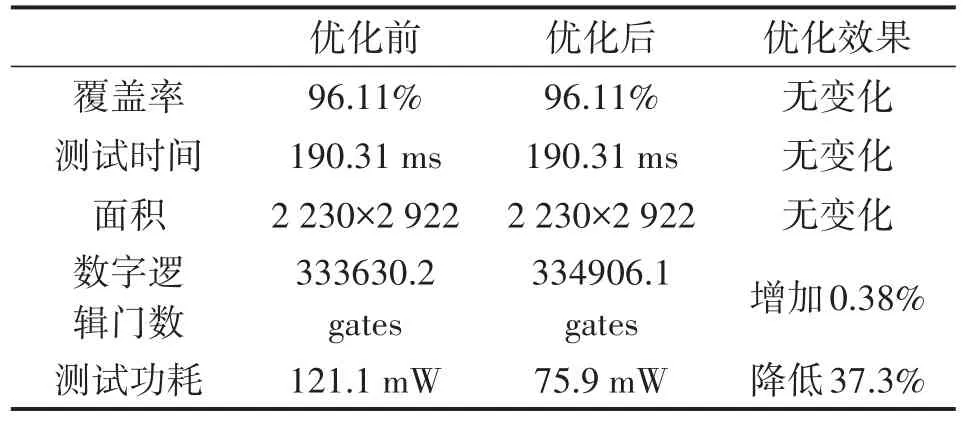

将以上提出的门控扫描时钟方法和门控组合逻辑方法相结合的测试方案应用于一款基于SMIC 0.18 μm logic Mixed-Signal工艺的电力线载波通信芯片的扫描测试设计,此芯片约20万门,共3条扫描链。使用的工具为Synopsys的DFT Compiler和IC Com⁃piler。通过门控结构的应用,扫描t测试整体功耗得到显著降低,尤其是扫描移位过程的功耗发生了巨大的变化。优化后芯片的整体参数如表1所示。

表1 优化结果

时间成本:采用门控扫描时钟方法不会增加测试时间。由于Scan_Clk/2’和Scan_Clk/2都与系统时钟同步,在扫描操作的时候,具有相同的时钟频率,都是测试时钟的一半,而且由于它们的相位差为半个测试时钟周期,因此在两个测试时钟周期内,共有两个的测试位被移入扫描链。这与传统扫描路径设计中每个测试时钟周期移入一个测试位,扫描移位时间是等同的。并且在捕获模式下,用的是系统测试时钟,也没有增加捕获时间。采用门控组合逻辑方法也不会增加测试时间,是因为该方法是对组合逻辑进行调整,没有影响到扫描时序路径。因此,门控扫描测试方案的测试时间等于传统扫描测试方案的测试时间。

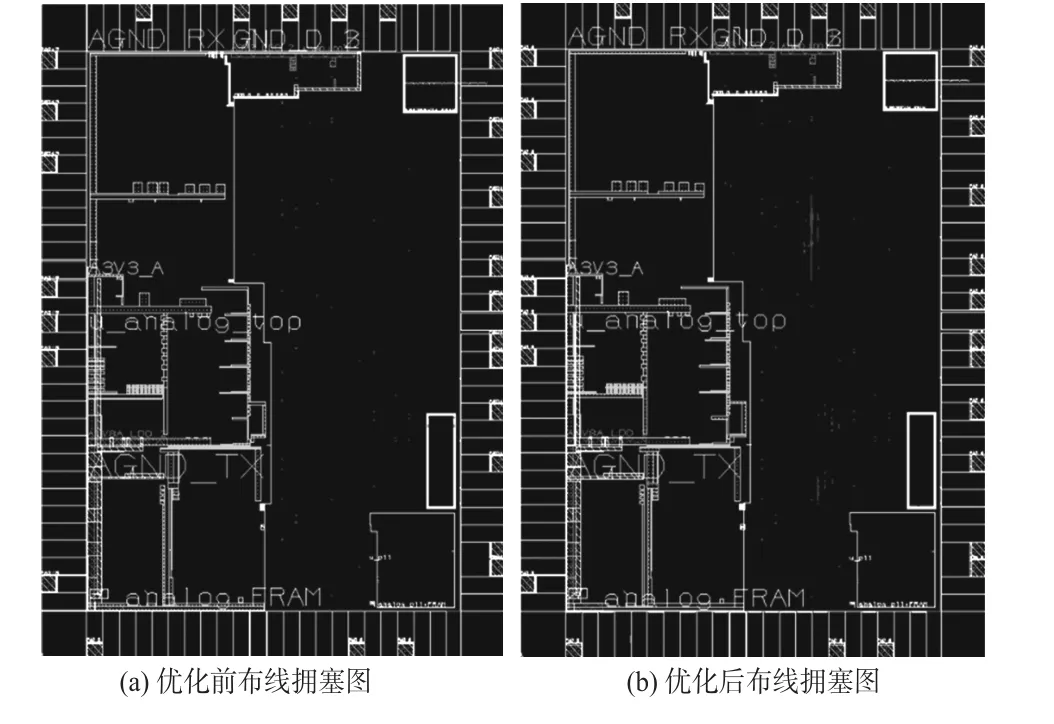

布线成本:采用门控扫描时钟方法增加了扫描时钟产生模块和多路选择器。扫描时钟产生模块可以由1个D触发器和4个逻辑门组成,而1个D触发器由10个门组成,1个多路选择器由4个门组成。增加的门数和整个芯片的门数相比是微不足道的。采用门控组合逻辑方法,在一些触发器的Q端增加门控电路,即1个与门或者或门,折中考虑后本设计把total_percentage_gating的数值设为25%,增加了约1 260 gates。因此,增加的总的逻辑门约占总的数字逻辑门的0.38%,在保持芯片面积不变的情况下,导致布线资源占有量有所增加,布线拥塞情况如图6所示。从图6可以看出增加的布线资源占有量并未导致布线拥塞区域严重恶化,对芯片的后期设计影响并不严重。

图6 布线拥塞图

功耗方面:由于扫描测试的功耗可以近似看成平均分布于各个测试周期,因此随机选择几个周期进行比较。从图7功耗仿真波形图可以看出,采用门控扫描时钟方法,平均功耗从121.1 mW降为88.2 mW,降低了27.2%;然后采用门控组合逻辑方法,总的平均功耗从121.1 mW最终降为75.9 mW,共降低了37.3%,验证了门控扫描时钟方法和门控组合逻辑方法的可行性和正确性。

图7 功耗波形图

5 结论

本文提出了将门控扫描时钟方法和门控组合逻辑方法相结合的测试方案来降低芯片测试功耗,详细地阐述了该测试方案的原理,并成功应用于一款电力线载波通信芯片的可测性设计中。通过对比测试结果表明,该方案在不降低测试覆盖率、不增加测试时间的情况下,能够取得很好的功耗优化效果,可移植性强,可以高效地应用于多种芯片的扫描测试设计中。

[1]Wang S,Wei W.Cost Efficient Methods to Improve Performance of Broadcast Scan[C]//Proceedings of Asian Test Symposium.Sappo⁃ro,Japan,2008:163-169.

[2]陈志强.基于电力载波通信芯片的量产测试的设计与实现[D].北京:北京工业大学,2012.

[3]宋慧滨,史又华.面向低功耗BIST的VLSI可测性设计技术[J].电子器件,2002,25(1):101-104.

[4]虞致国,魏敬,杨兵.一种复杂SoC可测性的设计与实现[J].电子器件,2009,32(2):347-350.

[5]Crouch A L.Design-for-Test for Digital IC’s and Embedded core Systems[M].London:Prentice Hall PTR,1999:106-120.

[6]DFT Compiler Scan user Guide[K].Synopsys,2010:21-23.

[7]刘龑达,万培元,林平分.基于物理版图信息的低功耗扫描测试方法[J].中国集成电路,2014,23(7):29-34.

[8]Gerstendörfer S,Wunderlich H J.Minimized Power Consumption for Scan-Based BIST[J].Journal of Electronic Testing,2000,16(3):203-212.

祝雪菲(1991-)汉,河北人,现在北京工业大学硕士研究生,主要研究方向为数模混合集成电路设计,zhuxuefei1991@163.com;

张万荣(1964-)男,河北人,教授,博士生导师,研究方向为RF器件与RFIC、微电子器件与集成电路可靠性研究,wrzhang@bjut.edu.cn。