优化偏置点的SiGe功率放大器设计*

2015-02-28郝明丽陈延湖

孙 凯 ,郝明丽 ,陈延湖

(1.山东大学信息科学与工程学院,济南 250100;2.中国科学院微电子研究所,北京 100029)

近年来,随着智能手机、平板电脑和可穿戴设备的普及,市场对应用于无线局域网(WLAN)的无线通信模块的需求也越来越大。由于这些设备对体积有着严格的要求,高集成度的单芯片无线通信模块是最佳的选择。目前,无线通信模块中的低噪声放大器、混频器、锁相环等大部分组件都可以使用低成本的体硅CMOS工艺实现。但是,传统体硅CMOS工艺中MOS管击穿电压较低,在设计大功率的功率放大器时存在困难[1]。SiGe BiCMOS工艺是一种与体硅CMOS相兼容的工艺,不但具有体硅CMOS工艺高集成度和低成本的优势,而且提供异质结双极型晶体管(HBT)。SiGe HBT的高频特性良好,耐压更高,是设计功率放大器的优异器件[2]。因此,使用SiGe BiCMOS工艺设计功率放大器,进一步地实现无线通信系统的单芯片集成,一直是研究的热点。

目前,SiGe BiCMOS工艺在国外已经比较成熟,并且实现商业化,但国内还处于研究阶段。本文基于上海华虹宏力半导体制造有限公司最新开发的0.18 μm SiGe BiCMOS工艺,设计了应用于WLAN 2.4 GHz频段的高输出功率线性功率放大器。

1 工艺说明和器件选择

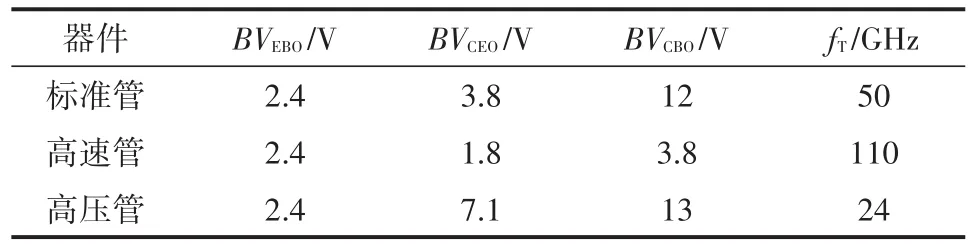

通常,SiGe HBT的击穿电压和特征频率之间存在折中关系[3]。本文使用的华虹宏力0.18 μm SiGe BiCMOS工艺就针对不同设计需求,提供了标准管、高速管和高压管。表1列举了几种不同类型HBT的击穿电压和特征频率fT的典型值。本文采用了其中的高压管,基极悬空时的击穿电压BVCEO为7.1 V,特征频率fT为24 GHz,满足3.3 V电源电压,2.4 GHz功率放大器的设计要求。该工艺还提供了硅通孔(TSV),硅通孔技术可以极大的减小接地引线寄生阻抗,非常有利于射频电路的设计[4]。该工艺的金属层有三层,材质为铝,其中顶层金属厚度为2.92 μm,较厚的金属层可以减小射频传输损耗。

表1 SiGe HBT器件参数

1.1 晶体管尺寸的选取

设计功率放大器的第1步是确定电路每1级晶体管的尺寸。为了在较低的电源电压下输出一定的功率,晶体管必须有足够的电流输出能力。确定晶体管尺寸和电流输出能力之间的关系至关重要。对于HBT器件来说,在大电流下主要受到Kirk效应的影响。Kirk效应使晶体管在大电流下电流增益下降,特征频率降低,高频性能变差。因此,产生Kirk效应时的电流通常会作为晶体管工作时的最大直流电流[5]。

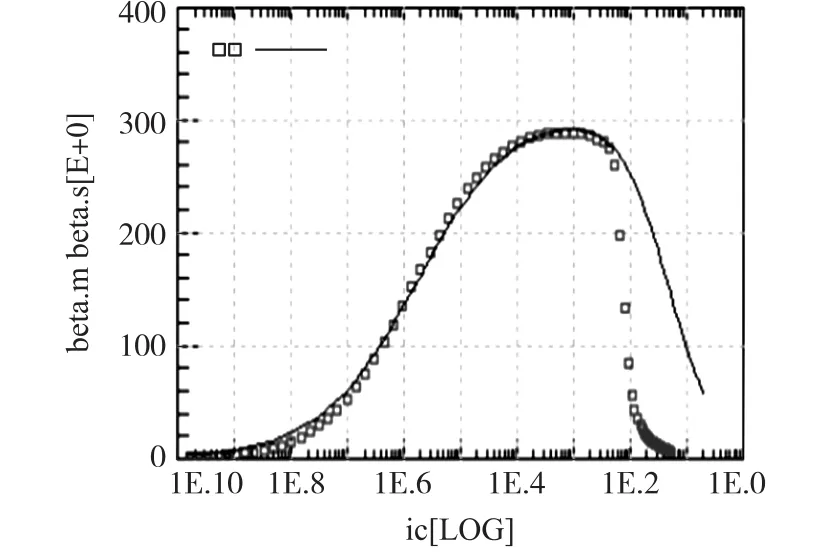

图1是工艺厂商提供的一个发射极指长9.9 μm,指宽0.6 μm的4指高压HBT共发射极电流增益随集电极电流变化的曲线。由于工艺厂商提供的器件模型是Gummel-Poon模型,对大信号时器件的模拟不够精确,所以可以看到在大电流下仿真结果和测试结果出现较大偏差。由图可知,当集电极电流大约为2 mA时,共发射极电流增益开始下降,出现了Kirk效应。此时,发射结上的电流密度约为0.084 mA/μm2。对于设计输出功率为23 dBm(200 mW)的功率放大器,采用A类放大方式近似计算,可得集电极直流电流

图1 共发射极电流增益随集电极电流变化曲线

其中,VCC表示电源电压,在本设计中为3.3 V。按0.084 mA/μm2电流密度可算出发射极面积为1 440 μm2,为留有余量,将面积定为2 000 μm2。

本设计采用了3级放大结构,前、后级之间晶体管面积按1∶4分配,以保证前级对后级有足够的驱动能力。最终确定的晶体管尺寸为:单个晶体管为4指结构,发射极每指指长为13 μm,宽为0.6 μm;第1级采用4个晶体管并联,发射极总面积为125 μm2;第2级采用16个晶体管并联,发射极总面积为500 μm2;输出级采用64个晶体管并联,发射极面积为2 000 μm2。

1.2 稳定性考虑

HBT功率放大电路在工作中面临两个稳定性问题:电稳定性和热稳定性[6]。电稳定性是指电路在某些偏置和终端条件下存在自激振荡的可能。热稳定性是多管并联晶体管因为自热效应产生的电流增益坍塌现象。当多管并联工作时,每一个晶体管都是一个热源,中心的晶体管温度高,边缘处的晶体管温度低。由于温度高的晶体管导通电压低,相同基极电压下流过的电流多,温度就会更高,形成了热电正反馈。这种热电正反馈最终造成电流增益的下降[5]。

图2 基极串联电阻的HBT

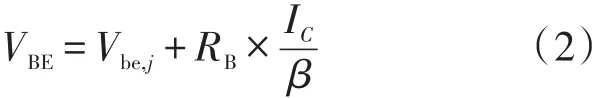

为解决电稳定性和热稳定性问题,在每一个晶体管基极串联了一个镇流电阻,如图2所示。对于电稳定性,晶体管基极的串联电阻削弱了从集电极反馈到基极的信号,因此避免了振荡的产生,提高了稳定性。对于热稳定性,假设基极串联电阻为RB,基射结电压为Vbe,j,则串联电阻和基射结总电压

若温度升高,使IC变大,则在基极串联电阻RB上的压降增加,减小了晶体管发射结电压Vbe,j,从而抑制了IC上升的趋势,增加了热稳定性。

由于基极串联电阻会降低增益,选用的电阻值不能过大。一般以能保证1 GHz以上频段电学绝对稳定为宜。基于工艺库器件特性,在本设计中,每个晶体管基极串联电阻为42 Ω。

2 电路设计

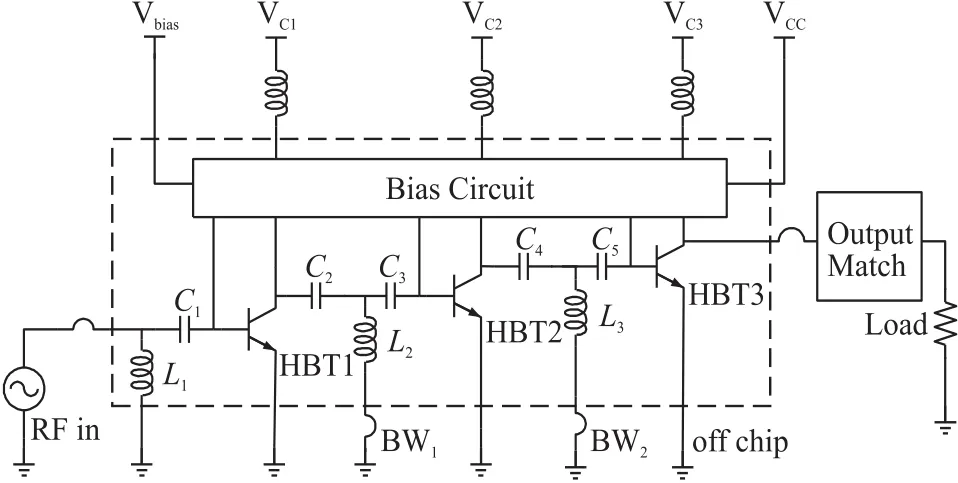

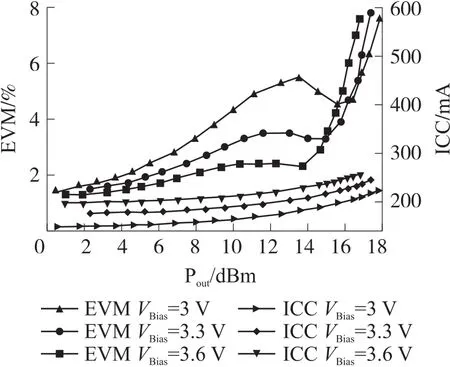

由于工艺厂商提供TSV,接地阻抗可以做到非常小,本设计采用了单端放大电路。为了具有足够的增益,电路采用3级放大结构。电路结构如图3所示。芯片内部集成输入匹配、级间匹配和偏置电路。将输出匹配电路置于片外,增加设计的灵活性,同时避免片上低Q值电感的使用,可以提高效率和输出功率。

图3 2.4 GHz功率放大器电路图

2.1 匹配电路设计

功率放大器电路设计中,匹配电路是最关键的部分之一。匹配电路的设计关系到功率放大器的增益、输出功率和效率等指标的好坏。设计匹配电路需要先确定每一级晶体管输入端和输出端的匹配阻抗。本文采用如下方案确定各级晶体管的匹配阻抗:

(1)通过负载牵引(Load-Pull)仿真得到输出级的最佳功率匹配阻抗,输出端匹配至此阻抗后,在输入端做大信号S参数仿真(LSSP),得到输出级输入端匹配阻抗[7];

(2)同样地,对第2级晶体管做Load-Pull仿真,得到第2级晶体管的最佳功率匹配阻抗,输出端匹配至此阻抗,然后在输入端做LSSP仿真,得到第2级输入端匹配阻抗;

(3)对第1级晶体管做双端口S参数仿真,得到第1级晶体管输入输出双共轭匹配阻抗。

确定阻抗之后,需要采用实际电路实现匹配。输入匹配电路采用了L形L-C结构电路。图3中电容C1既起到匹配的作用,又能起到隔直的作用。由于输入匹配对输出功率和效率的影响较小,匹配电感和电容全部采用片上元件实现,电感L1通过TSV形式接地。

1级、2级和2级、3级之间的级间匹配采用T形C-L-C结构。C-L-C结构的优势是电感L设计的灵活性,在本设计中匹配电路电感并没有通过TSV直接接地,而是通过键合线接地。如前文所述,工艺厂商提供的器件模型是Gummel-Poon模型,对大信号的仿真并不足够准确,因此Load-Pull仿真得到的阻抗也可能并不准确。通过接地键合线接地,给芯片留有调试的余地。由于键合线电感参与了匹配,因此它的建模仿真非常重要。

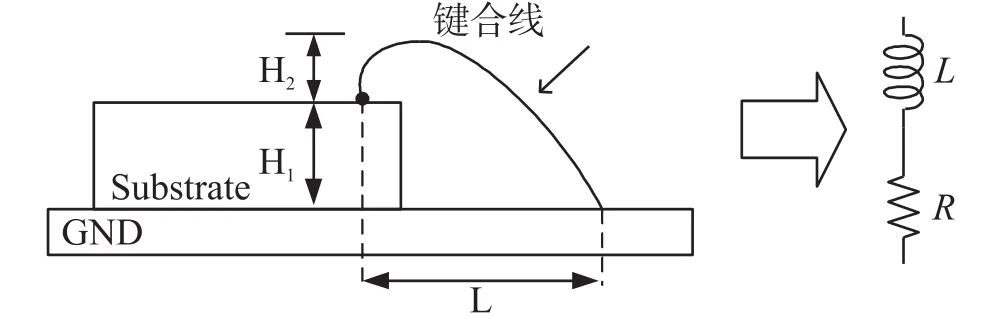

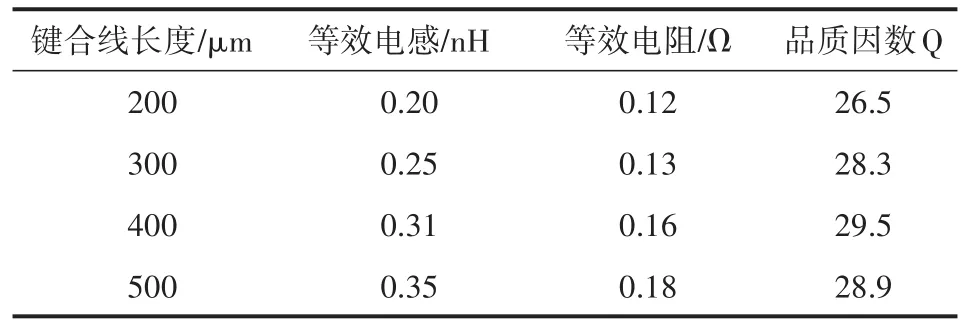

接地键合线的结构如图4所示。H1表示芯片厚度,本文使用的工艺芯片厚度为100 μm,H2是键合线弧高,典型值50 μm,L是弧长,典型值200 μm~500 μm,所用键合线直径为25.4 μm,材质为金。

图4 丝焊工艺键合线示意图和等效电路

键合线等效电路可采用LR串联模型来表示[8]。在 HFSS软件中,对长度为 200 μm~500 μm的键合线进行了仿真,结果如表2所示。在本设计仿真时,采用了200 μm长键合线。

表2 不同长度键合线等效电感、电阻和Q值(2.4 GHz)

2.2 偏置电路

偏置电路给功率放大器提供稳定的偏置电压,传统的分压式偏置电路不适用于功率放大器电路[7]。

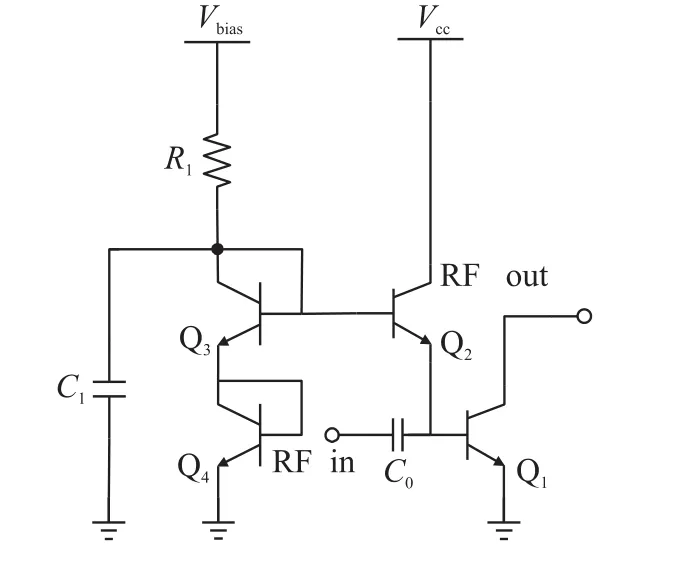

图5为采用的偏置电路原理图,Q2、Q3、Q4、C1和R1组成偏置电路,通过Vbias端口控制放大管Q1的静态偏置点。晶体管Q3和Q4以二极管形式上下串联连接,利用了pn结的电压钳位特性,起到电压源的作用,输出电压由Vbias和电阻R1决定。并联电容C1可进一步提高电压的稳定度,保证Q2基极电流变化时也能给Q2基极提供稳定的电压。

图5 偏置电路

Q2的选择至关重要,它直接决定了Q1基极偏置电压在输入功率变化时的稳定度。输入信号功率增加时,由于晶体管的非线性,Q1基极直流电流会增加。Q1基极串有隔直电容,因此Q1基极直流电流全部来源于Q2发射极。又由于Q1基极和Q2发射极电压变化完全相同,所以只有当Q2基极电流电压特性和Q1的发射极电流电压特性一致时才能使电流的变化也相同。故Q2发射结面积A2应满足下式:

其中Je是单位面积发射极电流,A1是Q1发射极面积,β1是Q1共发射极电流增益。

3 芯片测试和偏置点的优化

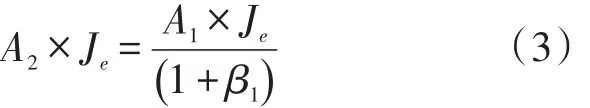

使用Cadence Virtuoso完成电路版图设计,芯片尺寸为1 400 μm×900 μm,版图照片如图6(a)所示。

测试所用PCB板如图6(b)所示,测试板的板材为Rogers 4003C。测试时,首先对输出匹配电路进行调试,输出匹配电路设计为Line-Shunt Capacitor形式。在3.3 V电源电压和3.3 V偏置电压下,芯片输入端输入功率为-2.5 dBm的2.45 GHz单音信号,在输出端调节并联电容大小和在传输线上的位置,使输出功率达到最大。最终,使用3 pF村田电容,使输出功率达到了23.1 dBm。

图6 WLAN功率放大器版图照片和测试板

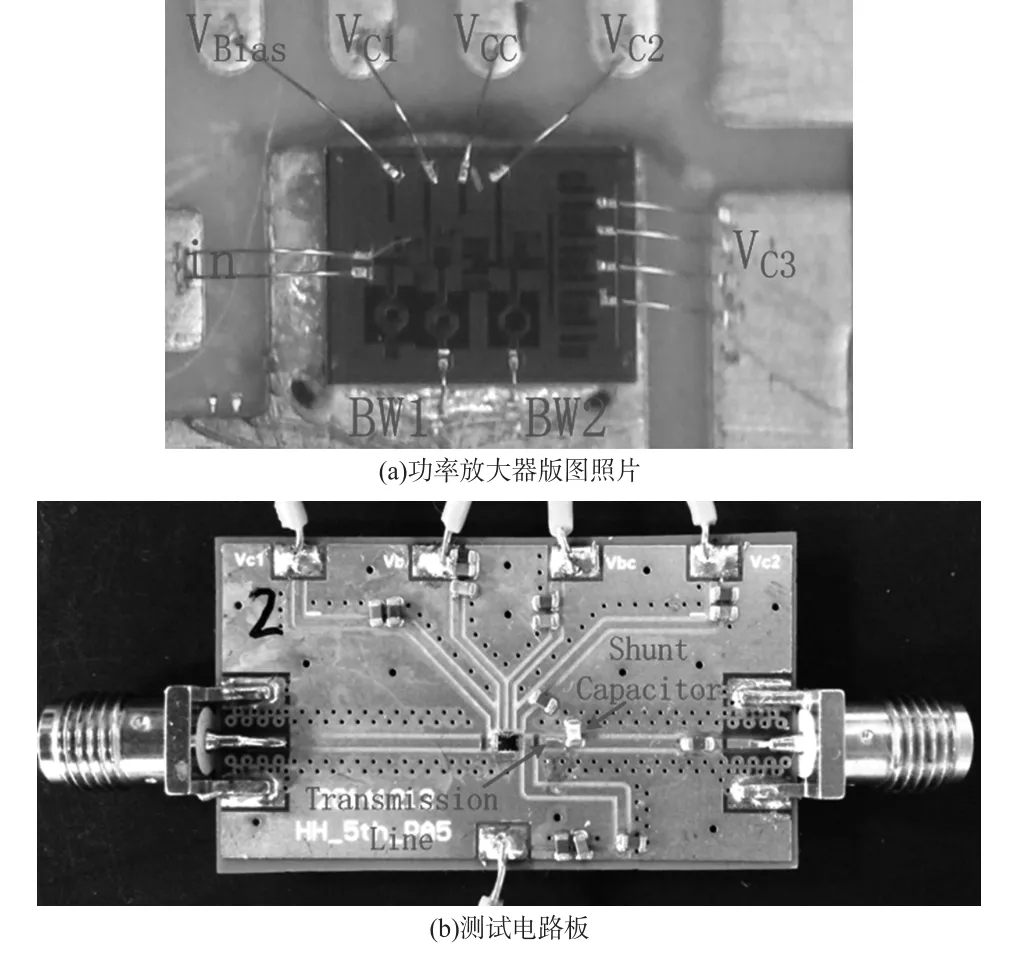

晶体管的偏置点对功率放大器的线性度和效率有直接的影响。偏置点的选择应该在满足线性度要求的前提下,最大化功率放大器的输出功率和效率。在不同偏置电压下,使用IEEE 802.11g 54 Mbit/s信号分别测试了误差矢量幅度(EVM)和消耗电流Icc随输出信号平均功率Pout变化的曲线,测试结果如图7所示。

图7 EVM和Icc随输出功率的变化

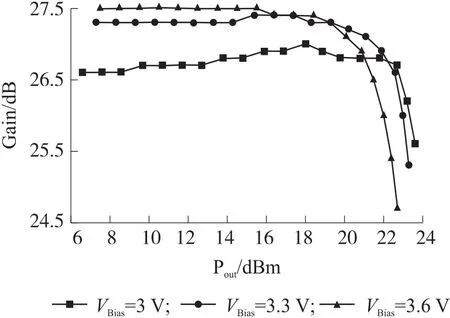

IEEE 802.11 g/n协议要求54 Mbit/s信号EVM须小于5.6%,由图7可知,在满足EVM协议要求的前提下,偏置电压为3 V时,输出功率最高,为16.6 dBm,同时消耗的电流也最小,为212 mA。由图7还可发现,在低功率处(小于13 dBm),偏置点越高,线性度越好;在高功率处(大于13 dBm),偏置电压高时,线性度迅速恶化,偏置电压低时,线性度会出现一定的改善。这一现象可通过图8功率增益随输出功率变化曲线解释。低功率时,在3 V的偏置电压下,功率增益一直在上升,而偏置为3.3 V和3.6 V的功率增益基本保持不变,所以低功率时较低的偏置电压导致了较高的EVM。到了高功率区,偏置为3.6 V的功率增益迅速下降,因此EVM快速变差,而偏置为3 V的功率增益变化比较平缓,因此在高功率区3 V的偏置电压下,EVM较小。

图8 功率增益随输出功率变化曲线

由以上分析可知,通过对偏置点的优化,可以在满足系统线性度要求的前提下,实现效率和功率的最大化。将偏置电压定为3 V,对仿真结果和测试结果进行了对比。

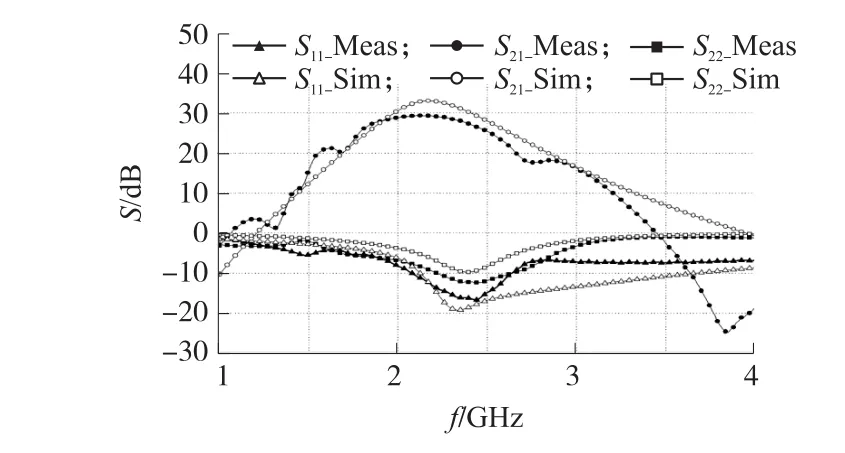

图9为小信号S参数仿真和测试结果。由图可知,S参数测试结果和仿真结果基本吻合。S11测试值在2.4 GHz~2.5 GHz范围内小于-14 dB,实现了良好的共轭匹配。S21测试值在2.4 GHz~2.5 GHz范围内相比仿真值降低了大约2.5 dB,原因是在仿真时未考虑外部元件和电路板的损耗。

图9 小信号S参数

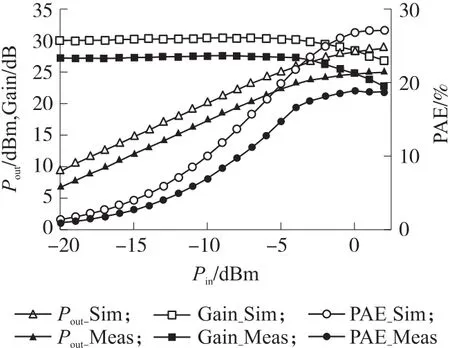

图10对比了输出功率Pout、增益Gain和功率附加效率PAE的仿真和测试结果。在低输入功率处,扣除掉2.5 dB的增益仿真误差后,测试结果和仿真结果非常接近。测试得到的输出1 dB压缩点为23.6 dBm,效率为18.1%。仿真输出1 dB压缩点为27.1 dBm,与测试结果相差3.5 dB,原因是模型在大信号下还不够精确。

图10 输出功率、增益和PAE随输入功率变化曲线

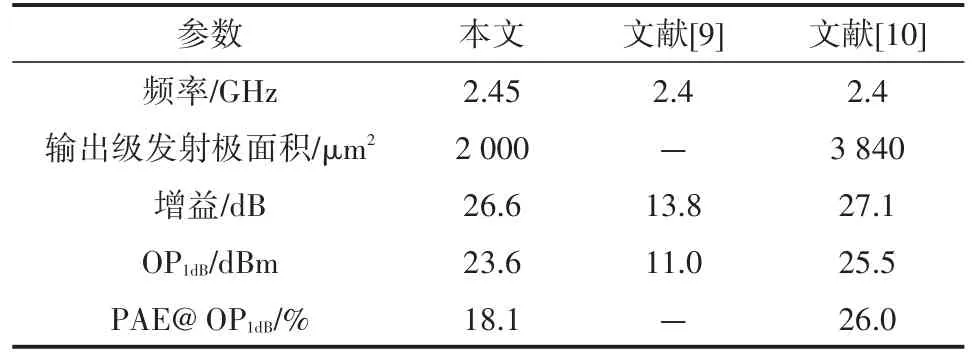

表3对比了本文的SiGe功率放大器和最近发表的其他文献功率放大器的性能。

表3 本文SiGe功率放大器性能和其他论文对比

4 结论

基于国内开发的0.18 μm SiGe BiCMOS工艺设计了应用于2.4 GHz WLAN的功率放大器。通过优化偏置点,提高了满足线性度要求的线性输出功率和效率。分析了测试与仿真结果的差异及其原因。在优化的偏置电压下测试结果表明,增益为26.6 dB,输出1 dB压缩点可达23.6 dBm。对于IEEE 802.11g 54 Mbit/s信号,EVM为5.6%时,输出功率可达16.6 dBm,显示出良好的线性度,满足2.4 GHz频段WLAN的应用需求。

[1]Niknejad A M,Chowdhury D,Chen J.Design of CMOS Power A mplifiers[J].IEEE Transactions on Microwave Theory and Tech⁃niques,2012,60(6):1784-1796.

[2]阮颖,陈磊,田亮,等.基于0.18 μm SiGe BiCMOS工艺的高线性射频功率放大器[J].微电子学,2010,(4):469-472,476.

[3]徐世六主编.SiGe微电子技术[M].北京:国防工业出版社,2007:2-5.

[4]Joseph A,Huang C W,Stamper A,et al.Ultra-Thin Chip Technol⁃ogy and Applications[M].New York:Springer,2011:445-453.

[5]RaghavanA,SrirattanaN,LaskarJ.ModelingandDesignTechniquesfor RFPowerAmplifiers[M].Hoboken:JohnWiley&Sons,2008:141-146.

[6]陈延湖,申华军,刘新宇,等.Design Consideration of the Ther⁃mal and Electro Stability of Multi-Finger HBTs Based on Different Device Structures[J].半导体学报,2010,(10):28-31.

[7]李文渊,顾洵.5 GHz无线局域网的锗硅异质结晶体管功率放大器[J].电子器件,2008,(6):1761-1764,1768.

[8]周永强,王立新,张万荣,等.射频功率晶体管内匹配技术中键合线的建模仿真与参数提取[J].电子器件,2011,34(4):363-366.

[9]尤云霞,陈岚,王海永,等.基于SiGe HBT的射频功率放大器[J].微电子学与计算机,2014,(4):144-147.

[10]阮颖,陈磊,张先仁.WLAN应用的SiGe功率放大器中功率单元优化设计[J].半导体技术,2014,(9):641-645.

孙 凯(1991-),男,汉族,山东大学硕士研究生,研究方向为射频集成电路设计,sunkai@ime.ac.cn;陈延湖(1977-),男,汉族,山东济南人,山东大学信息科学与工程学院讲师,硕士生导师,工学博士,主要从事微波器件及其集成电路研究,chenyanhu@sdu.edu.cn。