基于分级处理的星载数据总线综合测试方法

2015-02-27朱晓辉吕德东张阁

朱晓辉 吕德东 张阁

(中国空间技术研究院通信卫星事业部,北京 100094)

基于分级处理的星载数据总线综合测试方法

朱晓辉 吕德东 张阁

(中国空间技术研究院通信卫星事业部,北京 100094)

分析了星载数据总线测试的层次模型,提出了一种基于分级处理的数据总线综合测试方法,并设计了专用测试设备。该设备以定制的智能PCI板卡为核心,依托工控机平台,实现了星载数据总线的综合测试,并成功应用在某航天器测试中。应用结果表明:该方法能够在实现综合测试的同时很好地化解数据总线测试的实时性难题,其时序控制精度达到亚微秒级,全面提高了测试精度和测试效率,可为其它航天器数据总线测试提供参考。

星载数据总线;综合测试;分级数据处理;时序控制;大容量存储

1 引言

随着微电子技术和数字技术的不断发展完善,星载电子设备之间的通信越来越多地采用星载数据总线完成,其系统功能的实现也越来越依赖于数据总线通信的稳定可靠[1-3]。因此,在航天器系统测试中,对星载数据总线的测试也提出了越来越高的要求。

数据总线测试采用的一般方法,是使用总线仿真设备对数据总线进行采集监视,同时提供数据激励,以构成数据总线测试回路[4-5]。从设备组成看,按照处理器的不同,可以划分为基于嵌入式处理器的小型化嵌入式设备和基于PC机或工控机平台的桌面设备两类。对采用嵌入式系统平台的数据总线测试仪,其特点是实时性好,但功能相对单一,不能或仅能提供简单的激励源[6]。此外,由于数据存储容量有限,测试完毕需要导出数据进行事后处理才可供分析判读,并不直观[7]。对于采用桌面计算机平台的总线仿真器,则一般具备友好的图形化用户界面和基于PC的强大的数据后处理能力,但由于操作系统的限制,即使采用复杂的多线程操作、数据缓冲等软件设计方法,仍然无法从根本上克服多通道并发控制、实时响应和高精度时序控制方面的不足[8-9]。综合来看,高精度时序控制与复杂的系统功能之间的矛盾难以调和。

在现有的星载数据总线测试中,由于上述矛盾的存在,通常将有时序要求的内容列为单独的测试项目,使用不同的测试设备进行测试,而在整星总装、测试与试验(AIT)中则不对通信时序进行检查,存在测试覆盖不全面和效率较低的弊端。本文在分析测试需求的基础上,按照分级处理的思想,提出了统一的综合测试方法,并设计了专用测试设备,可为航天器数据总线的综合测试验证提供全面、高效的测试手段。

2 待测系统及测试方法

2.1 待测系统

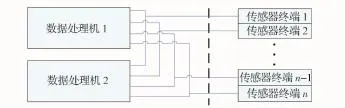

待测系统星载数据处理机与传感器终端之间采用RS-422数据总线的主从通信,其总线连接关系如图1所示。

图1 数据总线连接关系图Fig.1 Data bus connection topology

两台数据处理机分别通过总线采集多个传感器终端的数据,以数据处理机为主动方进行主从通信。每次通信开始,数据处理机向不同的传感器终端分时发送数据请求字,传感器收到数据处理机的数据请求后,应在协议规定的响应时间td(td<0.1 ms)内开始返回要求的有效信息;若传感器终端在td时间内未返回有效信息,则数据处理机判定此情况为一次通信故障,并停止此串口通信,直至下次发送数据请求。

在通信过程中,每个数据采集周期内数据处理机分时与每个传感器终端各通信一次。终端与处理机的通信时序见图2,协议对采集周期tp、各传感器之间的通信间隔ti和传感器终端响应时间td均提出了明确的要求。

图2 数据处理机与传感器终端通信时序示意图Fig.2 Time sequence of the bus communications between processor and sensors

2.2 层次化的测试需求

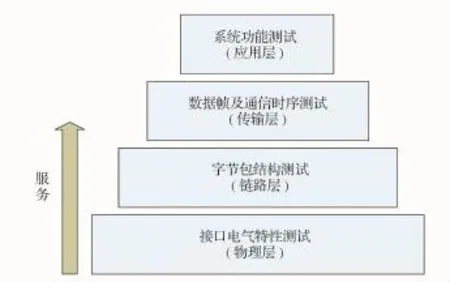

对上述星载数据总线的测试需求可以划分为4个层次,如图3所示。

1)物理层——接口电气特性测试

对通信接口电气特性进行测试,包括输出端的信号电平、上升沿、下降沿以及接口阻抗特性等。通常使用示波器等通用仪器,无需专用测试设备。

2)链路层——字节包结构测试

对通信接口的链路层协议的正确性进行验证,包括字节分包、起始位、停止位、校验位、码速率和编码方式等。即通过总线仿真设备向被测设备(目的端口)发送激励信号,采集被测总线设备(源端口)发出的信号并进行解析,检查链路层接口协议的匹配性。

图3 数据总线接口测试层次Fig.3 Layers of data bus interface testing

3)传输层——帧结构及通信时序测试

(1)对通信接口的传输层协议的正确性进行验证,包括请求字、帧头字节、数据字节的位置和顺序、校验字节等;

(2)通信时序测试:包括数据处理机的数据请求间隔ti和请求周期tp的测试,传感器终端对请求字的应答响应时间td的测试。

该测试在链路层测试的基础上将激励源、被测设备和数据采集终端构成闭合回路,对被测设备施加符合传输层协议的特定激励,可以更加充分地对被测设备在不同激励下的响应进行测试。对有时序要求的测试项目,则还需要总线仿真设备具有较高的实时性和时间分辨率。

4)应用层——系统功能测试

(1)总线侦听:被测对象属复杂系统,总线通信链路也可能受到热环境、电磁环境等的影响,故有必要对数据总线进行实时侦听和记录,以便在偶发异常时,能够为异常分析提供第一手资料,准确定位故障;

(2)功能测试:参与通信的各方均接入系统后,需要对基于总线的系统整体功能进行测试,具体测试项目根据系统功能设计确定,例如数据处理机根据传感器终端采集的信息,实时计算并向执行机构输出不同的控制信号,要求测试设备能记录不同工作模式下的测试数据并绘制曲线,最终通过统计数据得出是否符合要求的测试结论。

可见,应用层的系统功能测试通常需要测试设备具有遥控指令发送和遥测数据处理、大容量数据存储、较复杂的数据分析以及图形化显示等功能。

综上,在图3所示层次化测试需求中,下层为上层提供支持和服务,上层测试的前提是下层验证正确。因此测试宜采用自下而上的顺序,逐级验证。

2.3 传统测试方法的不足

根据图3所示层次化测试需求,不同层次有不同的测试要求,因此传统的数据总线测试需要在不同的测试阶段设计不同的测试项目。通常,先在单机设备测试阶段使用示波器完成物理层测试,再使用总线仿真设备验证链路层和通信协议;对于有时序要求的内容,列为单独的测试项目,使用专用测试设备进行测试;应用层的系统功能测试则在分系统或整星AIT阶段进行,通过指令-遥测回路间接验证总线通信的正确性,不再对通信时序进行检查。虽然各阶段独立的测试项目共同覆盖了所有的测试需求,但由于被测设备所处的环境不同,每个测试项目仅针对特定激励下的响应进行检查,所有单项测试结果均正常,并不等价于被测设备在复合激励下的响应正确。因此,传统测试方法的弊端集中体现在无法实现从接口协议、通信时序到系统功能的综合测试,存在测试覆盖不全面和测试效率较低的不足。

此外,传统测试方法的测试有效性也受到总线仿真设备自身性能的制约。对功能复杂又有实时性或严格时序要求的总线环境进行仿真,要求总线仿真设备既有较高的实时性,又有强大的仿真计算和存储能力。现有的总线仿真设备多基于PC平台和Windows操作系统实现,凭借较高的仿真计算和存储能力,可以实现仿真数据激励和响应数据记录,还可以完成曲线绘制和数据分析比对等辅助功能。但由于PC平台的非实时性,对有实时性或有严格时序要求的测试项目往往难以胜任。具有实时性的总线仿真设备一般使用嵌入式系统平台,由于功能相对单一,难以适应综合测试的需要,而且需要为航天器定制开发,价格昂贵、通用性差。

2.4 基于分级处理的综合测试方法

为解决以上问题,本文提出了基于分级处理的综合测试方法。首先,为实现综合测试,必须同时构建如图4所示的“总线激励-响应”和“遥控-遥测”两个测试回路,两个测试回路均由专用测试设备集中控制,统一调度。其次,为兼顾复杂的功能测试和高精度的总线时序测试,必须对不同的测试数据加以区别,分级处理:其中有实时性和时序要求的数据来自“总线激励-响应”回路,对该回路的数据必须及时处理,并保证响应内容和通信时序符合要求,故列为一级处理;而对于“遥控-遥测”回路,则数据率较低,没有实时性要求,可以列为二级处理,同时为了保证两个测试回路的一致性,二级处理还应包括对一级处理的处理模式、方法和判据条件进行设定;最后,两级处理的结果必须进行汇总,以便综合比对两个回路数据的匹配性,对测试数据进行归档存储和统计分析,完成合格判定及曲线图形绘制等工作,可列为三级处理。

图4 数据总线测试回路Fig.4 Loops in data bus test

要实现基于分级处理的综合测试方法有两个关键步骤:一是如何整合测试回路,实现综合测试;二是如何实现分级处理。

1)整合测试回路,实现综合测试

在传统的卫星测试方法中,“遥控-遥测”回路采用遥测前端设备和遥控前端设备实现,而“总线激励-响应”回路则由总线测试设备实现。要将两个测试回路加以整合,可以定制专用设备,将总线测试和遥控、遥测的功能集成为一台单机,以此实现用同一个CPU同时控制两个测试回路,实现综合测试的目的。但此法必然导致设备复杂度高、研制难度加大、成本增加等弊端,而且使原有遥控、遥测前端设备闲置,造成浪费。

经过分析不难发现,相比总线数据,卫星的遥控、遥测数据量相对较小,且实时性要求较低。因此,可以考虑以实时性相对较高的总线测试回路为重点,以松耦合的方式实现与原有遥控、遥测前端设备连接,用系统化的解决方案实现综合测试的功能。如图4所示,专用测试设备的核心功能是实现“总线激励-响应”测试回路,同时,通过以太网络接口与原有的遥控、遥测前端设备连接,可以接管“遥控-遥测”测试回路,实现两个测试回路的整合,在避免研制过于复杂的专用测试设备的同时,实现综合测试。

2)分级处理的实现

实现分级处理有两种方法:一是使用不同的处理器完成不同层级的处理任务;二是通过软件的线程调度和优先级设置,实现CPU时间片在不同处理任务之间的合理分配。前者实现成本高、难度较大,但可以实现更好的实时性和并发处理;后者实现起来相对简单、灵活,但其实时性受操作系统的局限较大。因此,为实现总线测试的多通道并发控制,满足较高的实时性要求,可采用现场可编程门阵列(FPGA)作为实时协处理器完成一级处理;而二级处理和三级处理则可以采用桌面计算机配合多线程软件的方法实现,兼顾性能与成本。

要实现综合测试,各级处理之间必须有数据交互。二级处理和三级处理通过同一个软件中的不同线程实现,通过软件进程通信机制即可解决数据交互的问题;而一级处理则由于采用了FPGA作为协处理器,其与桌面计算机的CPU之间还需要一个高效的通信接口,成熟的外部器件互联(PCI)总线无疑是较好的选择。协处理器控制下的数据总线通信有很好的实时性,但要完成与CPU之间的数据交互,还必须解决处理器速率匹配的问题。一个较好的方法是通过存储器构建数据缓冲池,使两个不同速率的处理器能够以异步读写的方式对存储器进行读写操作,从而实现速率匹配。

综上,按照上述方法,可以较好地化解实时性和复杂功能之间的矛盾,整合两个测试回路,实现对被测总线设备或总线系统的综合测试。

3 专用测试设备设计

3.1 需求分析

专用测试设备是实现前述测试方法的关键。综合起来,对专用测试设备需求可归纳为以下几项:

(1)总线数据采集和存储功能;

(2)实时数据解析功能;

(3)模拟数据源激励功能;

(4)动态激励计算功能;

(5)遥测接收及遥控指令发送功能;

(6)高精度时序控制能力;

(7)多通道并行处理能力。

3.2 总体设计

为满足以上需求,本文提出了智能数据总线接口卡配合PC系统平台的设计架构,如图5所示。

设备采用通用的桌面计算机平台,通过PCI总线智能接口卡扩展出8路独立的数据总线接口。利用PC强大的系统功能,可以完成仿真模型调用、数据库存取和数据统计分析工作,同时提供本地用户操作界面和与综合测试网的程控接口;作为设备核心的智能接口卡则通过板载大规模FPGA和同步动态随机存储器(SDRAM)实现实时数据处理和存储、多通道并发控制以及亚微秒级的高精度时序控制,满足测试系统的实时性要求。

3.3 关键设计环节

3.3.1 硬件电路设计

硬件设计工作主要是智能板卡的设计。为降低技术风险、提高设备可靠性,设计中选用了有较多应用的成熟技术。如选用美国PLX公司的PCI9054桥芯片实现PCI总线接口;选用美国XILINX公司的SPARTAN 6系列FPGA实现板载协议处理器;选用韩国Hynix公司的SDRAM实现32 Mbyte内存扩展等,其外围电路均有的成熟设计可供参考。

在数据总线接口部分,选用美国ADI公司的高速数字隔离器件对数据通道进行电气隔离;采用具备限压限流保护功能的第二级隔离DC/DC,单独为隔离后端的接口电路供电;严格按照规范的要求进行数据总线接口电路设计和阻抗匹配,同时满足电气特性和可靠性、安全性方面的要求。

3.3.2 FPGA设计

FPGA为8路数据总线配置了独立的先入先出存储器(FIFO),每路均包含接收FIFO、发送FIFO和已发送FIFO。其中,发送FIFO用于缓存待发送的数据,以保证总线数据发送的连续性;已发送FIFO用于缓存通过数据总线实际发出的数据内容及其发送时刻,为实际的数据激励留下准确记录;接收FIFO用于无损记录数据总线收到的数据内容及其到达的准确时刻。片内FIFO构成数据的一级缓存,当片内FIFO容量不能满足要求时,则通过片外SDRAM进行二级缓存。经过前两级缓存,可以有效降低上位机软件数据存取的实时性要求,从而能够将多次读写操作整合为块操作,提高了数据传输效率。

FPGA中的数据处理模块完成接收数据包的传输层协议解包、校验和发送数据的打包,一旦检测到错误的数据包将触发异常事件,通过状态寄存器上报上位机。

对有实时性要求的数据处理,均由PC系统前移至FPGA中的实时响应模块完成。该模块在数据处理模块的基础上,实现应用层的数据解析、逻辑判断和响应计算,上位机软件只需通过控制寄存器将响应事件、处理方法和相关参数等信息置入FPGA即可。当预定义的事件发生时,FPGA能够在微秒级时间内完成逻辑判断和数据处理,及时发出激励响应,并在事后通过状态寄存器和已发送FIFO向上位机报告事件和具体的响应内容及发出时刻。

3.3.3 上位机软件设计

上位机软件即图5中运行于PC平台的计算机系统应用软件,在接口卡FPGA和SDRAM的帮助下,上位机软件仅需在0.5~1 s的时间周期内完成与板卡的数据交互即可。其核心任务是将数据总线测试回路与指令/遥测测试回路统合在一起,综合判断,完成仿真模型的调用及测试数据的分析判读。除此之外,上位机软件还完成数据库存取操作,提供图形化用户界面,以列表和曲线的形式直观地显示数据分析的结果。

4 测试实施

上述专用测试设备通过智能板卡与PC平台配合,可实现基于分级处理的综合测试方法,目前已成功应用于星载数据总线测试中。现将测试实施情况简述如下。

4.1 测试回路构建

专用测试设备通过智能板卡实现8路独立的RS-422总线接口,具备多通道并发处理能力和高精度时序控制及测量能力,与被测总线设备相连即可构成“总线激励-响应”测试回路;另一方面,专用测试设备通过PC平台的网络接口和应用软件的指令/遥测数据处理模块,与遥测前端、遥控前端建立网络连接,可以实现遥控指令发送和遥测数据的接收处理,即“遥控-遥测”测试回路。两个回路均由运行于PC平台的应用软件统一控制、协同工作,测试数据也由应用软件进行汇总分析和统计,实现综合判读。

4.2 基于分级处理的综合测试实施

一级处理由智能板卡完成。在测试过程中,智能板卡有以下3种处理模式,分别完成不同的测试内容。

1)数据处理机仿真模式

该模式下,“总线激励-响应”回路模拟2台数据处理机,以便对传感器终端进行综合测试。测试过程中,智能板卡借助FPGA的数据处理能力不仅能完成总线链路层的协议分析和校验,还可以在传输层精确的模拟星上数据处理机的采集周期tp,测量各传感器终端的响应时间td,或缩短采集周期以进行压力测试。

2)传感器终端仿真模式

“总线激励-响应”回路可最多同时模拟8个传感器终端,以便对数据处理机进行综合测试。测试时,智能板卡除能对各层次的协议的正确性进行验证外,还能根据事先由上位机载入的判据条件和响应规则,实时判别来自总线的数据处理机指令,按照响应规则计算响应数据并发送给数据处理机。

3)侦听模式

“总线激励-响应”回路将不发送任何激励信号,仅对总线通信各方进行无损侦听,记录总线上各设备的通信数据内容和时间标签(精确到微秒),也可完成总线通信时序测试。

一级处理产生的测试数据全部暂存于智能板卡的板载缓存中,由上位机软件读取。二级和三级处理均由专用测试设备中的PC平台实现。其中二级处理的主要任务是集中控制“遥控-遥测”回路和“总线激励-响应”回路,按照测试流程发送遥控指令,采集遥测参数,同时通过PCI总线与智能板卡通信,同步控制“总线激励-响应”回路,设定一级处理的处理模式、响应规则和判据条件、模拟数据源等。三级处理负责定时读取前两级处理产生的输出数据,完成数据记录和图形绘制、数据比对和统计分析,最后综合得出判定结果。

4.3 应用效果

(1)通过一级处理实现了总线的实时响应和高精度时序控制。经实测,从收到满足判据条件的总线指令到返回仿真响应数据的时间,最快可在80μs内完成,完全满足不大于0.1 ms的设计指标;在时序控制方面,智能板卡的数据总线接口采用2.88 MHz的时钟驱动,理论上可以获得优于0.35μs的时间分辨率,考虑到时钟频率准确度和稳定性的影响,实测时序控制精度优于±1μs。

(2)通过二级处理实现了两个测试回路的统一控制,通过三级处理实现了测试数据的综合判读,使星载数据总线测试从若干独立的专项测试过渡到综合测试,且全过程测试数据可完整记录,测试效率和测试覆盖性显著提高。

5 结论

面对星载数据总线复杂的测试需求,传统的测试方法和测试设备存在测试覆盖不充分、效率较低、功能性能不够完备等诸多不足。本文在对测试需求充分剖析的基础上,提出了一种基于分级处理的数据总线综合测试方法,并据此设计了专用测试设备。该设备已成功应用于某卫星整星AIT测试中,不仅圆满完成测试任务,更使测试覆盖性、测试精度和测试效率得以全面提高,同时也验证了文中测试方法的有效性。本文主要结论可归纳如下。

(1)基于分级处理的数据总线综合测试方法满足了从链路层、传输层到应用层系统功能测试的多重要求,且能够实现测试数据的全程记录和统计分析,可为类似的星载数据总线测试提供借鉴。

(2)按照分级处理这一思路构建的基于智能板卡和PC平台的专用测试设备,能够很好地化解高精度时序控制与复杂的系统功能之间的矛盾,可为有类似要求的测试设备研制提供参考。

(References)

[1]Mughal M Rizwan,Roascio Danilo,Reyneri Leonardo M.Data communication bus interface for modular architecture of small satellites[C]//Proceedings of 2012 IEEE First AESS European Conference on Satellite Telecommunications.New York:IEEE,2012:1-6

[2]T Pittera,M D Errico.Multi-purpose modular plug and play architecture for space systems:design,integration and testing[J].Acta Astronautica,2011,69:629-643

[3]Bai Haowei,Pavan Allalaghatta,Brian Van Voorst,et al.Design of anext generation high-speed data bus[C]//Proceedings of the 1st Space Exploration Conference:Continuing the Voyage of Discovery.Washington D.C.:AIAA,2005:1-7

[4]王庆成.航天器电测技术[M].北京:中国科学技术出版社,2007 Wang Qingcheng.Electrical test technology of spacecraft[M].Beijing:China Sience and Technology Press,2007(in Chinese)

[5]张翰英.卫星电测技术[M].北京:宇航出版社,1999 Zhang Hanying.Satellite electrical test technology[M]. Beijing:China Astronautics Press,1999(in Chinese)

[6]黄以锋,景博,谢红星.基于AVR单片机的429总线测试仪的设计[J].微计算机信息,2008 24(26):42-43,5 Huang Yifeng,Jing Bo,Xie Hongxing.Design of 429 data bus analyzer based on AVR MCU[J].Microcomputer Information,2008 24(26):42-43,5(in Chinese)

[7]储成群,焦新泉,于君.一种大容量固态飞行数据记录器设计[J].计算机测量与控制,2011,19(1):227-229,239 Chu Chengqun,Jiao Xinquan,Yu Jun.A design of large-capacity solid-state flight data recorder[J].Computer Measurement&Control,2011,19(1):227-229,239(in Chinese)

[8]任立军,刘威.RS-422数据处理软件设计[J].测控技术,2012,31(4):90-92 Ren Lijun,Liu Wei.Design of RS-422 bus data processing software[J].Measurement&Control Technology,2012,31(4):90-92(in Chinese)

[9]龚健,华更新,孙越,等.基于多种并发机制的卫星电子设备地面测试软件设计方法[J].空间控制技术与应用,2012,38(3):47-51,57 Gong Jian,Hua Gengxin,Sun Yue,et al.A multi-concurrence mechanism based design method of ground testing software for satellite electronic devices[J].Aerospace Control and Application,2012,38(3):47-51,57(in Chinese)

(编辑:李多)

A Method of Integrated Test for On-board Data Bus Based on Leveled Data Processing

ZHU Xiaohui LYU Dedong ZHANG Ge

(Institute of Telecommunication Satellite,China Academy of Space Technology,Beijing 100094,China)

According to the layered model of on-board data bus testing,an integrated test method based on leveled data processing is proposed,and special check-out equipment is designed.A customized smart PCI board is the core module of the equipment.By installing this board in an industrial PC platform,an integrated test system for on-board data bus is established and applied to the test program of a certain satellite successfully.Application results show that besides performing the integrated test,the real-time processing can be realized.By applying the method proposed in this paper,a timing precision of sub-microsecond is achieved,hence both accuracy and efficiency of the test are improved.The test method and equipment design proposed in this paper provides a reference for data bus testing of other spacecraft.

on-board data bus;integrated test;leveled data processing;timing control;largecapacity storage

V554

:ADOI:10.3969/j.issn.1673-8748.2015.05.021

2015-05-11;

:2015-08-20

朱晓辉,男,工程师,研究方向为航天器测试技术与测试方法。Email:crown_zxh@163.com。