一种3.3 V低电源电压的1553B总线收发器设计*

2015-02-26于宗光魏敬和胡水根江南大学物联网工程学院江苏无锡4中国电子科技集团公司第58研究所江苏无锡4035

印 琴,于宗光,*,魏敬和,,胡水根(.江南大学物联网工程学院,江苏无锡4; .中国电子科技集团公司第58研究所,江苏无锡4035)

一种3.3 V低电源电压的1553B总线收发器设计*

印琴1,于宗光1,2*,魏敬和1,2,胡水根2

(1.江南大学物联网工程学院,江苏无锡214122; 2.中国电子科技集团公司第58研究所,江苏无锡214035)

摘要:提出了一种基于1553B总线的收发器系统结构,设计实现了低压单电源供电的1553B总线收发器,有效降低了收发器的动态功耗。仿真及测试结果表明,该电路能在3.3 V的低电压下实现所有的收发功能,总线占空比为100%时的最大动态功耗仅为0.5 W,相比于5 V供电的1553B总线收发器,其动态功耗大约下降了1.7 W。该收发器采用0.5 μm DPTM BCD (15 V)工艺流片,并已成功应用到低压的1553B总线产品中。

关键词:收发器;低功耗;低压供电; 1553B总线

MIL-STD-1553B是美国军方提出的一种在航空电子系统中为各种机载设备互联的网络接口标准。1553B总线以其高度的可靠性和灵活性在航空设备中得到了广泛的应用。航空事业的不断发展,对低电压1553B总线产品[1-3]提出了需求。

随着3.3 V低压的1553B总线协议处理器的广泛应用,需要3.3 V低电压的1553B总线收发器与之匹配,这样在同一块PCB板上就能用3.3 V的单电源提供电压,减小PCB板的面积。同时降低1553B收发器的电源电压能有效降低功耗,从而延长1553B产品的使用寿命,节约成本。针对这一需求,我们设计出了一种低电压的1553B总线收发器[7-8]。

项目来源:江苏省333工程科研项目(BRA2011115)

1 电路系统结构及功能描述

本文设计的3.3V低电源电压的1553B总线收发器包括了发送器、接收器及相关的配置和逻辑控制电路,电路系统结构[4]如图1所示。

图1 1553B总线收发器系统结构图

收发器的发送器部分,接收一对曼彻斯特Ⅱ编码互补数据信号TXIN和NTXIN,在使能信号TX_EN的控制下,经过缓冲器、整形网络和驱动电路的处理,在输出端产生一对1553B总线的差分数据信号TXOUT 和NTXOUT,产生的差分输出信号再经过隔离变压器,直接耦合或变压器耦合到1553B数据总线上。

收发器的接收器部分,接收一对来自1553B总线的双向调制曼彻斯特Ⅱ数据RXIN和NRXIN,经过限幅电路、缓冲电路和滤波电路等进行信号处理,在输出端产生一对曼彻斯特Ⅱ编码的互补数字信号RXOUT和NRXOUT[5-6]。

收发器的配置电路部分包括时钟基准和基准电流源:时钟基准由多谐振荡器产生一个内部稳定时钟脉冲,周期为240 ns;基准电流源提供发送器和接收器所需镜像电流基准。其逻辑控制部分包括内建自测试电路和移位寄存器电路:内建自测试电路是在电路内部增加附加电路,增加内部电路的可控性和可观测性,使电路易于测试;移位寄存器为42位,用以实现对基准电路部分的基准电流源电流幅度的调节、直接对发送器输出电流幅度的调节以及对接收器中可调电阻电路阻值的调节。

2 收发器的关键电路设计

2.1发送器中关键电路设计

发送器的输入信号为TTL电平,包括正向输入端、反向输入端和使能输入端3个信号。由于在模拟电路中无法直接对数字逻辑电平进行处理,因此需要先对输入的TTL电平进行转化。经过初步转化后的信号为标准的方波信号,整形电路主要实现对波形的调整,使之满足输出的曼彻斯特码的要求。

图2所示的是其中正向输入信号通路中的最后一级整形电路和驱动电路。本文设计的发送器对波形的调整是通过各级电路依次进行微调,最终实现对整个波形的调整,使之满足输出的曼彻斯特码的要求。另外,为了满足输出端所需要的驱动能力,在整形电路之后接有一个大的驱动MOS管,由MOS管的电流方程可知,驱动电流正比于MOS管的宽长比,所以增大MOS管的驱动能力,提高驱动电流,可通过调节MOS管的宽长比获得。经多次仿真调整,本设计采用的驱动管M16的宽长比最终确定为250 000∶1。如图2所示,与M16相串联的3个MOS 管M17、M18、M19在数字信号H、I、J的控制下选择性导通,以配合M16调节驱动电流使得输出信号TXOUT的波形平缓。

图2 整形网络电路

另外由图2结合图1可以看出,图2整形网络的输出信号TXOUT后接的负载是变压器,考虑到此发送器模块是单电源3.3 V电压供电,无法提供负电平,但为了使发送器输出到变压器上的电平达到7.4 V,本设计中采用变压器互感的方法提供负电平。

2.2接收器中关键电路设计

接收器的输入信号通过变压器连接到1553B数据总线上,输入信号的峰-峰值为10.6 V左右,而对于低压3.3 V单电源供电的收发器而言,将未经处理的曼彻斯特码直接作为后续电路的输入必然会引起电路稳定性和可靠性的一系列问题,所以接收器需要先对输入的曼彻斯特码进行限幅处理。

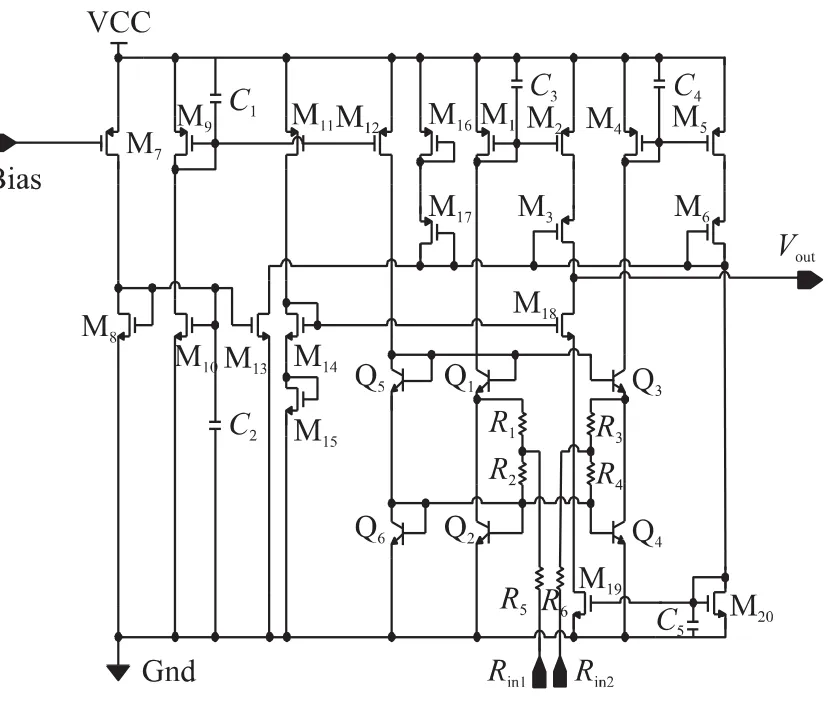

限幅电路如图3所示。其中Bias为前级偏置电路产生的偏置电压,RXIN和NRXIN为两个数值相等、相位相反的曼彻斯特码输入信号,考虑RXIN相对为低电位,NRXIN为高电位的情况。当RXIN的值足够大时,三极管Q1和Q2的VBE必然大于三极管的开启电压,处于导通状态,而三极管Q3和Q4的VBE小于三极管的开启电压,所以截止。由偏置电路产生的偏置电压通过M8、M10和M13构成的电流镜结构为M3及M6提供相同的偏置电压,同时由M9、M11、M12、Q5及Q6构成的电流镜结构保证了流过Q1、Q2的电流为恒定值,又因为Q1、Q2与M1、M2、M3一起构成的电流镜结构使得流过M2、M3的电流恒定,从而MOS管M2、M3上的压降恒定,3.3V的电源电压经两个恒定压降的MOS管得到的输出电压随之被限定在3.3 V以下。综上所述,该限幅电路主要是利用了三极管的电压钳制作用对输出电平进行限幅的。

图3 限幅电路逻辑

由于在接收器中限幅后产生的信号包含有较多的毛刺,为了有效的滤除限幅过程中带来的毛刺,需要在限幅电路之后接入一个高阶的低通滤波器。低通滤波器的结构如图4所示,它是由两个二阶低通滤波器相级联构成的四阶低通滤波器,其中接入滤波器的有效电阻值R1、R2、R3、R4受数字调制信号的控制,也就是说此滤波器的截止频率可以通过数字调制信号加以改变。

图4 滤波电路

3 电路仿真及流片

3.1电路仿真结果

基于上华0.5 μm DPTM BCD(15 V)工艺,我们采用Cadence的Spectre软件结合Synopsys公司的Hspice软件对1553B总线收发器进行了功能仿真。考虑到工艺库中未提供隔离变压器模型,在仿真之前需要对隔离变压器进行Spice建模,将隔离变压器分为4端电感描述主次级线圈电感值,然后用两个互感耦合器K1和K2定义主次级变压器电感耦合系数。仿真时的全局电源电压设为3.3 V,收发器的功能仿真波形如图5所示,从仿真波形图可以明显看出,本文设计的1553B总线收发器能在3.3 V低压下正常工作。

图5 收发器的仿真波形

3.2版图布局及流片测试结果

版图设计是收发器设计中的一个重要环节,直接决定芯片的成本和性能。图6所示为本文设计收发器的整体版图,版图为两路收发器的版图,面积为4.9 mm×4.3 mm。电源对地采用漏端跨阱的NMOS器件结构进行保护。阱/衬底接触设计成块状以增加接触面积,为防止闩锁效应,阱内外N-P管间距适当加大。

图6 收发器的电路版图

芯片在上华成功流片后,采用示波器测得的收发器的发送器波形和接收器波形如图7所示。其中图7(a)是由1553B协议处理器送入发送器的一对曼彻斯特Ⅱ编码互补数据信号TXIN和NTXIN的波形图,图7(b)是经过发送器处理之后产生的输出信号TXOUT的波形图,同时也是接收器的输入信号波形图,图7 (c)是接收器的输出信号RXOUT、NRXOUT的波形图。测得的波形图表明接收器最终的输出信号与1553B协议处理器送给发送器的输入信号一致,表明本文设计的收发器很好的实现了3.3V低压下的收发功能。

经测试,其各项性能指标满足设计要求。表1给出了3.3 V和5 V两种电源电压下,变压器耦合和直接耦合时收发器的上升下降时间的测试值、总线占空比分别为0%、25%、50%、100%时动态功耗的测试值,各测试值均在极限值范围内,符合设计标准。

表1 收发器的部分性能参数

图7 发送器和接收器的输入输出波形

将3.3 V电源电压与5 V电源电压下的动态功耗Pw进行对比,可以看出总线占空比为100%时,5 V电源电压下的动态功耗测试值为2.21 W,而3.3 V电源电压下的动态功耗测试值仅为0.54 W,大约下降了1.7 W,其性能在功耗方面得到了很大的改善,达到了设计目标。

4 结束语

文中阐述了一种3.3 V低电源电压的1553B总线收发器的设计。简要介绍了收发器中整形电路、限幅电路、滤波电路的结构及功能,并给出了电路的仿真及流片结果。从测试结果可以看出本文设计的收发器实现了所有的收发功能,各项参数符合1553B总线规范,功耗大幅降低,能有效延长1553B产品的使用寿命,节约成本。

参考文献:

[1]周密,金惠华,尚利宏.1553B总线协议IP核设计与实现[J].电子器件,2007,30(1) : 334-338.

[2]宣志斌,李飞.一种抗辐照1553总线收发器设计[J].电子与封装,2013,9(4) : 22-24.

[3]邓彬.1553总线收发器设计[D].西安电子科技大学,2013.

[4]DDC.BU-6474X/6484X/6486X data sheet[EB/OL].http: / / www.ddc-web.com,2011: 11-23.

[5]唐兴刚,贺克军.一款CAN总线收发器芯片的电路设计[J].微电子学与计算机,2011,28(5) : 125-129.

[6]王宏莎.CAN总线收发器电路的设计与研究[D].电子科技大学,2013.

[7]Zhou Li,An Junshe.Study on the Low Power Technologies of 1553B Bus[J].Signal Processing,Communication and Computing,2013,10 (11) :1-5.

[8]李小娟,陈定安,崔一平.622 Mbit/s大气激光通信机与10/ 100 Mbit/s自适应收发器的设计及集成[J].电子器件,2007,30(3) : 855-858.

印 琴(1989-),女,汉族,江苏泰兴人,硕士研究生,主要研究方向为集成电设计,18352513607@ 163.com;

于宗光(1964-),男,汉族,山东潍坊人,博士,教授,博士生导师,研究方向为集成电路设计开发,Yuzg58@ sina.com。

High-Speed Data Transceiver System Based on DDR2 SDRAM Ping-Pong Double Buffering

LIU Jie,SAI Jingbo*

(Beijing University of Technology,Beijing 100022,China)

Abstract:In the high-speed data transceiver system design,the first problem to be solved is the real-time data cache,However,the limited memory resources of FPGA can not meet the requirements of massive data cache,To solve the problem of system cache huge amounts of data,the system proposed ping-pong double buffering innovative design based on the DDR2 SDRAM.Design of two-way high-capacity asynchronous FIFO based on DDR2 SDRAM,selection logic operations to achieve a ping-pong between the two paths through the FPGA to achieve the cached data.Experimental results show that the Data transceiver system based on DDR2 SDRAM realized every road 512 Mbit cache space and 200 MHz of the bus rate and solved the problem of the huge amounts of data cache.

Key words:high-speed data transceiver system; ping-pong double buffering; DDR2 SDRAM Technology; asynchronous FIFO

中图分类号:TN492

文献标识码:A

文章编号:1005-9490(2015) 03-0646-04

收稿日期:2014-07-10修改日期: 2014-11-15

doi:EEACC: 6210; 721010.3969/j.issn.1005-9490.2015.03.036