一种低抖动电荷泵锁相环的设计*

2015-02-26张万荣江之韵胡瑞心卓汇涵陈昌麟赵飞义

白 杨,张万荣,江之韵,胡瑞心,卓汇涵,陈昌麟,赵飞义

(北京工业大学电子信息与控制工程学院,北京100124)

一种低抖动电荷泵锁相环的设计*

白杨,张万荣*,江之韵,胡瑞心,卓汇涵,陈昌麟,赵飞义

(北京工业大学电子信息与控制工程学院,北京100124)

摘要:采用动态鉴频鉴相器、基于常数跨导轨到轨运算放大器的电荷泵、差分型环形压控振荡器,设计了一种低抖动的电荷泵锁相环。基于SMIC 0.18-μm CMOS工艺,利用Cadence软件完成了电路的设计与仿真。结果表明,动态的鉴频鉴相器,有效消除了死区。新型的电荷泵结构,在输出电压为0.5 V~1.5 V时将电流失配减小到了2%以下。压控振荡器在频率为1 MHz时输出的相位噪声为-94.87 dB在1 MHz,调谐范围为0.8 GHz~1.8 GHz。锁相环锁定后输出电压波动为2.45 mV,输出时钟的峰峰值抖动为12.5 ps。

关键词:电荷泵锁相环;低抖动;常数跨导轨到轨运算放大器;环形压控振荡器

项目来源:北京市自然基金项目(4142007,4143059)

电荷泵锁相环(CPPLL)广泛应用于时钟生成、频率综合、高速串行通信和3G无线通信等领域。以其高速、低成本、低功耗和易于集成等优点,在当今电子时代发挥着不可替代的作用。CMOS技术的出现,使电荷泵锁相环实现了低功耗、小面积和低相位噪声的优势。但是在低成本、低功耗等情况下,如何实现低抖动的电荷泵锁相环已经引起了全球的研究热潮[1]。

传统的电荷泵锁相环存在抖动问题的主要原因有以下几方面:①鉴频鉴相器复位脉冲信号延迟时间不足产生死区、输出信号延迟时间不同造成控制电压周期性减幅振荡产生的电路抖动[2]。②电荷泵的电流失配产生电路杂波,电荷共享引起控制电压波动[3]。③压控振荡器的相位噪声引起电路的抖动[4]。

基于上述对电荷泵锁相环抖动产生的分析,采用了动态鉴频鉴相器结构、基于常跨导轨到轨运算放大器的电荷泵结构、差分型的环形压控振荡器结构,有效解决了抖动对电路性能产生的不良影响。

1 电荷泵锁相环基本原理

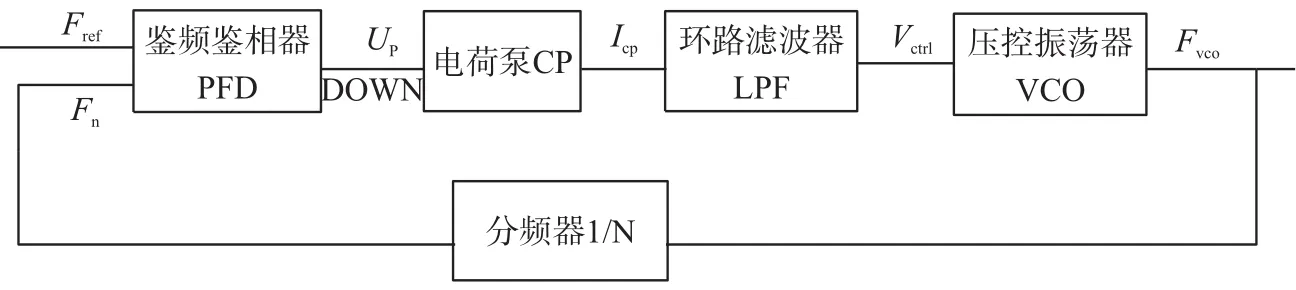

电荷泵锁相环电路的基本结构如图1所示,包括鉴频鉴相器(PFD)、电荷泵(CP)、环路滤波器(LPF)、压控振荡器(VCO)和分频器。

图1 锁相环的结构图

电荷泵锁相环的基本原理是:鉴频鉴相器(PFD)检测出输入参考时钟Fref与分频器分频之后时钟Fn的相位差和频率差,产生能够控制电荷泵(CP)充电状态和放电状态的相应电压信号UP和DOWN。电荷泵电路将UP信号和DOWN信号转换成充电、放电电流信号,对环路滤波器(LPF)内部电容进行充放电。环路滤波器将电荷泵输出的脉冲信号转换成直流模拟控制信号Vctrl。压控振荡器(VCO)根据控制电压Vctrl的大小调整输出时钟频率Fvco,使通过分频器后的信号频率与输入参考时钟频率尽量接近。整个环路形成了一个反馈系统,输出信号最终在频率和相位上与参考时钟信号同步,并达到锁定状态[5]。

2 电荷泵锁相环电路设计

本文所设计的电荷泵锁相环电路由鉴频鉴相器、电荷泵、压控振荡器、环路滤波器和分频器5个模块组成。下面具体分析各主要模块的电路实现。

2.1动态的鉴频鉴相器(PFD)

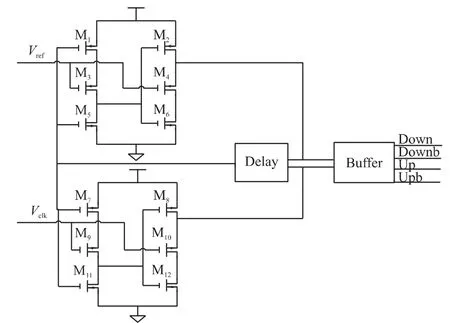

传统鉴频鉴相器当输入信号的相位差ΔΦ小于某个定值Φ0时,产生的窄脉冲由于结点电容的存在,会有一定的上升时间和下降时间,这样就没有足够的时间到达高电平,从而无法打开电荷泵开关注入电流,使环路增益降到零且输出相位不能锁定。这个±Φ0的区域被称为死区,死区会引起锁相环电路的抖动,影响整个电路的工作性能。因此本文设计了一种能够有效消除死区,降低电路抖动的动态PFD。其结构如图2所示,该结构由两个边沿触发的可复位D触发器、一个延迟单元和一个缓冲单元组成。其中,在D触发器的复位路径中加入了由异或门和反相器组成的延迟单元,使窄脉冲信号有足够的时间到达高电平,有效消除死区,减小电路的抖动。同时,缓冲单元在使用反相器的基础上加入了互补传输门,保证了信号UP和DOWN开、关电荷泵的延迟时间相同,防止了控制电压的周期性减幅振荡引起电路抖动[6]。此电路结构拥有速度快、无静态功耗、动态功耗低的优点。

图2 鉴频鉴相器结构图

2.2基于常数跨导轨到轨运算放大器的电荷泵(CP)

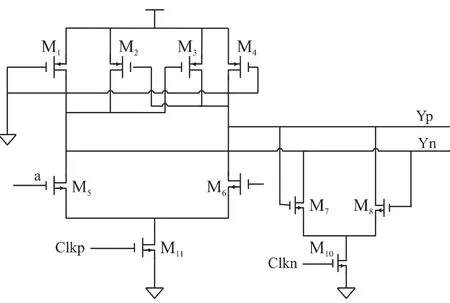

电荷泵是电荷泵锁相环中非常关键的模块,直接影响锁相环的整体性能。传统的电荷泵存在着电流失配和电荷共享的非理想因素。电流失配会产生电路杂波,电荷共享会引起电荷泵的输出电压波动,二者都会不同程度上引起电路的抖动[7]。本文提出的电荷泵结构如图3所示,本结构由电流参考支路(M7、M8、M9、M10)、电荷泵支路(M1、M2、M3、M4、M5、M6)、常数跨导轨到轨运算放大器(Amp1)和运算放大器(Amp2)组成。

图3 电荷泵结构图

为了抑制电流失配产生的影响,本文采用了以PMOS电流镜为负载的差分放大器Amp2与晶体管(M1~M10)负反馈连接的电路结构。这种结构能够有效地钳位结点X和结点Z的电压,使其满足Vx= Vz。则流过晶体管M8的电流I1与流过晶体管M1的电流I2相等,流经晶体管M9的电流I3与流经晶体管M3的电流I4相等。而流经同一支路的电流I3和I1显然也相等,所以流经晶体管M1的电流I2与流经晶体管M3的电流I4相等,消除了电流失配产生的电路抖动。

为了抑制电荷共享产生的影响,本文采用了将图4所示的常数跨导轨到轨运算放大器Amp1连接成负反馈的电路结构,使得电荷泵差分输出端电压当满足Vds-M1=Vds-M2=Vds-M3=Vds-M4时,开关M1、M3由同时导通到同时关断的过程中,电流源M5和电流源M6漏端的电压不变。因此我们解决了电荷共享引起的电荷泵输出电压波动的问题,保证了电荷泵可以产生稳定的输出电压,降低了锁相环的抖动,提升了锁相环的整体性能。

图4 常跨导轨到轨运算放大器结构图

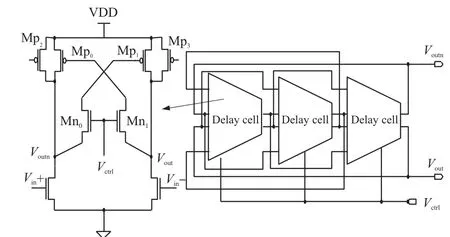

2.3差分型环形压控振荡器(VCO)

压控振荡器作为CPPLL中重要模块之一,直接决定了CPPLL的输出信号的准确性[9]。若VCO有足够大的频率调谐范围,电路可以实现良好的性能。为了获得较大的频率调谐范围、较小的芯片面积和较小的功耗,设计中采用了环形压控振荡器结构如图5所示。它是差分型的延迟单元构成的3级级联的结构。这种差分型的结构不仅对共模噪声具有良好的抑制作用,而且在延迟级数上表现出了很大的灵活性。此压控振荡器结构对锁相环抖动的降低具有突出贡献。

图5 压控振荡器结构图

延迟单元中负载管Mp0和Mp1交叉耦合,正反馈效应导致了开关信号的再生性,使输出信号接近满摆幅。延迟单元所具有的无电流源的轨到轨输出特性[10],使得该结构更适合在低电源电压下工作。可控管Mn0和Mn1接入到耦合回路中,通过改变耦合强度来改变频率。具体原理是:环振中传送的信号是完全开关信号,初始情况下Vout=0,Voutn= VDD。此时Mp0管的栅压为0,Mpl管的栅压在Mn0管的钳制作用下达到Vctrl-Vthn。当输入信号发生切换即由0变至VDD由VDD变至

图6 环路滤波器结构图

由分析可知,压控管Mn0和Mn1通过控制PMOS管的最大栅压,控制了反馈回路的强度。因为这些PMOS负载管的最小栅压为0,改变它们的最大栅压相当于改变周期内PMOS栅压的平均值,相应的就改变了流过PMOS管的平均电流。这样通过改变控制电压,就改变了延迟单元的延迟时间及对应的输出频率。同时,设计中引入了辅助输入对管Mp2和Mp3,其前馈作用可以有效增加环振的输出频率,达到增加VCO调谐范围的目的。为了使辅助通路信号传输不干扰主环路振荡,辅助输入对管增益强度应弱于主输入对管。

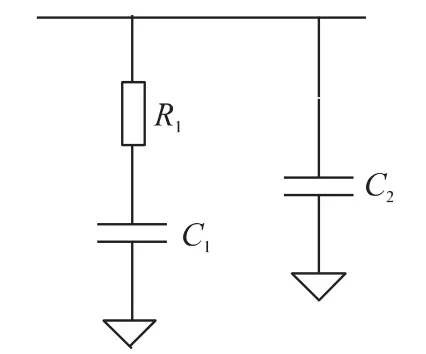

2.4环路滤波器和分频器

为了实现上述主要模块低抖动的性能,以及保证电荷泵锁相环工作性能良好,本文还设计了二阶无源低通滤波器和电流模逻辑的整数分频器。在电荷泵锁相环中,滤波器都为电流型[11]。本文的环路滤波器采用了二阶无源滤波器,如图6所示。它由一个电阻(R1)和两个电容(C1、C2)组成,C1= 100 pF,C2=15 pF,R1= 6 kΩ可以形成两个极点和一个零点。其中,R1主要决定电荷泵锁相环系统的环路带宽,C1主要决定电荷泵锁相环系统的稳定性,C2在系统传输函数中增加一个极点,有助于更好地滤除VCO控制电压上的高频成分。

分频器在锁相环电路中起到一个频率倍增的作用[12]。即压控振荡器输出的时钟通过分频器再与输入参考时钟相比较,就可得到一个频率加N倍的时钟信号,当然相位依然和参考时钟是同步的。本设计中的整数分频器是由如图7所示的基本单元构成的二分频电路,它是电流模逻辑(CML)差分电路的两级级联结构,CML分频采用差分对接入差分信号,具有抗干扰能力强、噪声低、摆幅小,功耗低的特点,但要注意和前级的输出幅度相匹配,如果峰峰值太大,则容易被削波,如果太小,则可能不会正确的分频。

图7 分频器基本单元结构图

3 电荷泵锁相环仿真验证

基于SMIC 0.18-μm CMOS工艺,通过仿真软件Cadence Spectre对设计的电路进行了仿真。CPPLL中电荷泵的充电电流和放电电流的匹配度仿真结果如图8所示,在输出电压为0.5 V~1.5 V时,充电电流和放电电流均能很好的匹配,电流失配小于2%,有效降低了电路的抖动。

图8 电荷泵的电流匹配度

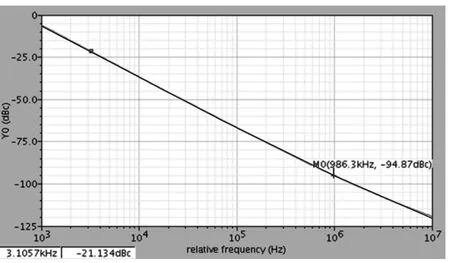

CPPLL中压控振荡器相位噪声的仿真结果如图9所示,在频率为1 MHz时压控振荡器的相位噪声为-94.87 dB@ 1 MHz。压控振荡器的调谐范围的仿真结果如图10所示,其范围为0.8 GHz~1.8 GHz。

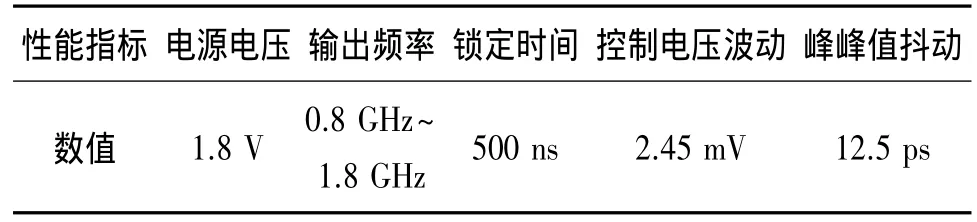

CPPLL锁定的仿真结果如图11所示,CPPLL 在500 ns之后被锁定,锁相环电路工作性能良好。锁定的CPPLL输出电压波动的仿真结果如图12所示,波动为2.45 mV,输出电压的波动得到了有效降低,对锁相环输出抖动的降低做出了贡献。

图9 压控振荡器的相位噪声

图10 压控振荡器的调谐范围

图12 电荷泵锁相环锁定的输出电压波动

电荷泵锁相环的整体性能指标如表1所示,CPPLL的控制电压波动为2.45 mV,输出时钟的峰峰值抖动为12.5 ps。电荷泵锁相环整体电路的抖动得到了有效降低。

表1 CPPLL整体性能指标

4 结论

本文基于SMIC 0.18-μm CMOS工艺,实现了一种低抖动电荷泵锁相环的设计。通过延迟单元的运用PFD很显然的消除了死区,减小了抖动。仿真结果显示,VCO的调谐范围为0.8 GHz~1.8 GHz,在频率为1MHz时的相位噪声为-94.87 dB@ 1 MHz。电荷泵的电流失配在输出电压为0.5 V~1.5 V时小于2%。电荷泵锁相环锁定后输出电压波动为2.45 mV,CPPLL输出时钟的峰峰值抖动为12.5 ps。

参考文献:

[1]王旭,朱红卫.一种用于时钟数据恢复的宽带锁相环设计[J].电子器件,2013,36(6) :828-832.

[2]Chen W H,Inerowicz M E,Byunghoo J.Phase Frequency Detector with Minimal Blind Zone for Fast Frequency Acquisition[J].IEEE Transactions on Circuits and SystemsⅡ:Express Briefs,2010,57 (12) :936-940.

[3]Yoshimura T,Iwade S,Makino H,et al.Analysis of Pull-in Range Limit by Charge Pump Mismatch in a Linear Phase-Locked Loop [J].IEEE Transactions on Circuits and Systems I:Regular Papers,2013,60(4) :896-907.

[4]Yang X,Lu X,Babakhani A.A Free-Space Optically Locked VCO with Picosecond Timing Jitter in 0.18-μm CMOS[J].Photonics Technology Letters,2014,26(12) :1180-1183.

[5]Ferriss M,Rylyakov A,Tierno J A,et al.A 28 GHz Hybrid PLL in 32 nm SOI CMOS[J].IEEE Journal of Solid-State Circuits,2014,49(4) :1027-1035.

[6]Szortyka V,Qixian Shi,Raczkowski K,et al.21.4 A 42 mW 230 fs-Jitter Sub-Sampling 60 GHz PLL in 40 nm CMOS[C]/ /IEEE International Solid-State Circuits Conference Digest of Technical Papers(ISSCC),San Francisco,America,2014:366-367.

[7]陈志华.一种2.4-GHz全集成双环路频率综合器的设计[J].电子器件,2014,37(3) :399-402.

[8]Wang Minsheng,Mayhugh T L,Embabi S H K,et al.Constant-Gm Rail-to-Rail CMOS Op-Amp Input Stage with Overlapped Transition Regions[J].IEEE Journal of Solid-State Circuits,1999,34(2) :148-156.

[9]Behzad Razavi.Design of Analog CMOS Integrated Circuits[M].Xi’an:Xi’an JiaoTong University Publishing Company,2002:348-351.

[10]Lee I-Ting,Tsai Yun-Ta,Liu Shen-Iuan.A Wide-Range PLL Using Self-Healing Prescaler/VCO in 65-nm CMOS[J].IEEE Transactions on Very Large Scale Integration(VLSI) Systems,2013,21(2) :250-258.

[11]高栋,张万荣,金冬月,等.一款应用于多频带的基于新型Cascode有源电感的高Q带通滤波器[J].电子器件,2013,36(5) :667-671.

[12]Xiu Liming,Lin WinTing,Lee TsungTa.Flying-Adder Fractional Divider Based Integer-N PLL:2nd Generation FAPLL as On-Chip Frequency Generator for SoC[J].IEEE Journal of Solid-State Circuits,2013,48(2) :441-455.

白 杨(1987-),女,蒙古族,辽宁人,北京工业大学硕士研究生,研究方向为射频器件与射频集成电路设计,baiyang0630@ 163.com;

张万荣(1964-),男,汉族,河北人,教授,北京工业大学博士生导师,研究方向为射频器件与射频集成电路、微电子器件与集成电路可靠性研究,wrzhang@ bjut.edu.cn。

A New CMOS Electronically Tunable Current Conveyor with Wide Tuning Range

HU Xuguang,WANG Weidong*

(School of Information and Communication Engineering,Guilin University of Electronic Technology,Guilin Guangxi 541004,China)

Abstract:A new CMOS electronically tunable second-generation current conveyor(ECCII) with wide tuning range was presented.By introducing the log-antilog current amplifier based on DDCC,the current gain was controlled electronically by adjusting the ratio of DC bias currents of the ECCII,In a certain range of the bias current,0<k≤10.The input stage adopts rail to rail structure by adding a cascode current mirror in the second level,increase the voltage tracking accuracy.Using SMIC 0.18 μm CMOS technology,the Spectre simulation results showed that vx/vyand iz/ixhad-3 dB bandwidth of 300 MHz and 155 MHz,Voltage tracking accuracy is 0.997,DC power consumption was 1.642 4 mW.The ECCII has comprehensive applications in the tunable current mode continuous time filters.

Key words:electronically tunable second-generation current; wide tuning range; log-antilog current amplifier; DDCC; current mode filters

中图分类号:TN433

文献标识码:A

文章编号:1005-9490(2015) 03-0516-05

收稿日期:2014-07-09修改日期:2014-08-03

doi:EEACC:121010.3969/j.issn.1005-9490.2015.03.010