新型宽可调范围CMOS电调谐第二代电流传输器(ECCII)

2015-02-25胡许光王卫东

胡许光,王卫东

(桂林电子科技大学信息与通信学院,广西桂林541004)

新型宽可调范围CMOS电调谐第二代电流传输器(ECCII)

胡许光,王卫东*

(桂林电子科技大学信息与通信学院,广西桂林541004)

摘要:提出了一种具有宽电流可调谐范围的新型CMOS电调谐第二代电流传输器(ECCII),通过引入基于差分差动电流传输器(DDCC)的对数反对数电流放大器,使电流增益通过偏置电流连续可调,在一定偏置电流下,调节系数0<k≤10。输入端采用的轨对轨结构通过在其第二级加入共源共栅电流镜,提高了电压跟随精度。采用SMIC 0.18 μm CMOS工艺参数,在±1 V的供电电源条件下,用Spectre对电路进行仿真。结果表明:vx/vy和iz/ix的-3 dB带宽分别为300 MHz和155 MHz,电压跟随精度为0.997,功耗为1.642 4 mW。经验证,该电路可用于设计可调谐连续时间电流模式滤波器,具有广泛的应用前景。

关键词:电调谐第二代电流传输器;宽可调范围;对数反对数电流放大器;差分差动电流传输器;电流模式滤波器

近年来,电流模式电路因其在带宽、速度、精度方面相比于电压模式电路有着更加明显的优势,受到越来越多学者的关注,其中一种有名的电流模式电路是第二代电流传输器,第二代电流传输器作为最有用的积木块被广泛应用于电流模式滤波器的设计。

然而,第二代电流传输器的电流输出端通常只具有单位增益,这使得其很难应用于可调谐性电路的设计。因此,具有电调谐性能的第二代电流传输器受到更多的研究,一些文献中提出了基于电流平方电路的ECCII[1-2],通过控制电流Ia调节Iz=(Ib/Ia) Ix,但是由于电路的固有弊端,|Ib|+|Ix|≤2Ia,而Ib又必须同时满足Ib≥Ix,使得输入电流的范围及传输精度都受到了限制,且电路的电流传输增益可调范围很小,另外一些文献采用了其他方式实现电流可调,虽然有所改进,但是电流传输增益可调范围依然不是很理想,本文通过引入基于差分差动电流传输器的对数反对数电流放大器,设计了一种新型的电调谐第二代电流传输器(ECCII),突破了以往电路的弊端,使得该电流传输器具有更宽的电流增益调节范围,并将提出的电路应用于电流模式滤波器的设计,验证了电路的实用性。

1 电路结构描述

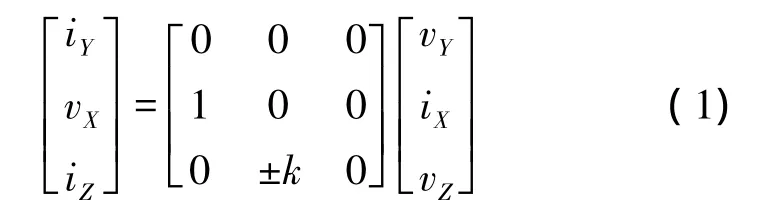

理想情况下,电调谐第二代电流传输器(ECCII)的电路符号如图1所示,其端口电流、电压关系如下矩阵方程所示:

由式(1)可知,ECCII的X端电压跟随Y端电压,Z端电流跟随X端电流,且Z端电流可被电调谐,调节系数为k。

图1 ECCII的电路符号

1.1基于差分差动电流传输器(DDCC)的对数反对数电流放大器

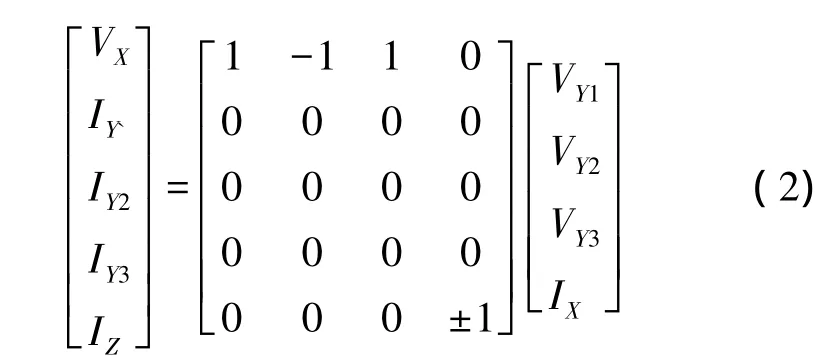

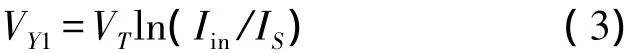

差分差动电流传输器[3](DDCC)端口电压,电流关系可用以下矩阵方程表示:

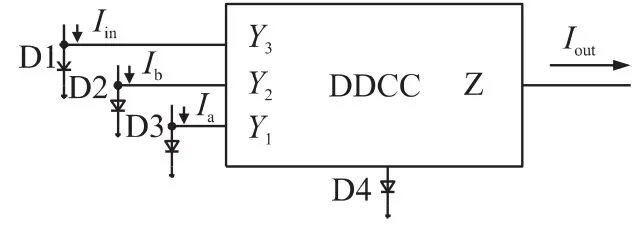

众所周知,当二级管工作在导通状态时,伏安特性曲线呈指数规律变化,利用这种特性,采用4个二极管与DDCC的X端、Y端口连接可实现增益可控的电流放大器,电路符号如图2所示。

图2 对数反对数电流放大器[4]

由图2可得:

联立式(3)~式(8)最终可得:

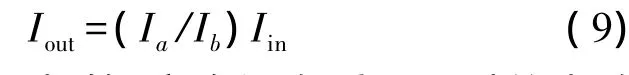

Ia、Ib只流经二极管,完全没有受限于以往电路的弊端,通过调节偏置电流Ia、Ib的值即可控制输出端达到更高的电流增益,提出电路采用全CMOS管集成,故二极管可利用NMOS或PMOS管实现,但PMOS作为二极管在工艺上实现起来比较复杂,故电路中采用NMOS管实现二极管功能,工艺上需要采用深N阱工艺将作为二极管使用的NMOS管隔离,实现其衬底电位自由选择,从而使衬底到漏极的PN结导通。图3给出了单个NMOS管作为二极管使用得到的伏安特性曲线,曲线呈指数规律变化.

图3 NMOS管作为二极管的原理图仿真

1.2电调谐第二代电流传输器(ECCII)

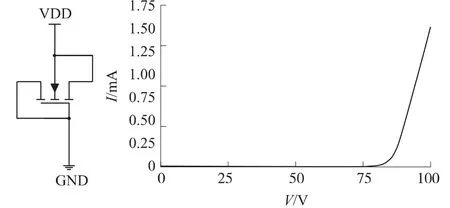

利用提出的电流增益可调电流放大器,可设计出电调谐第二代电流传输器[3-5],电路原理图如图4所示。电路主要由3个模块组成,轨对轨输入级、基于正负极性差分差动电流传输器(DDCC±)的电流放大器、偏置电路。

图4 新型电调谐第二代电流传输器(ECCII)

1.2.1轨对轨输入级

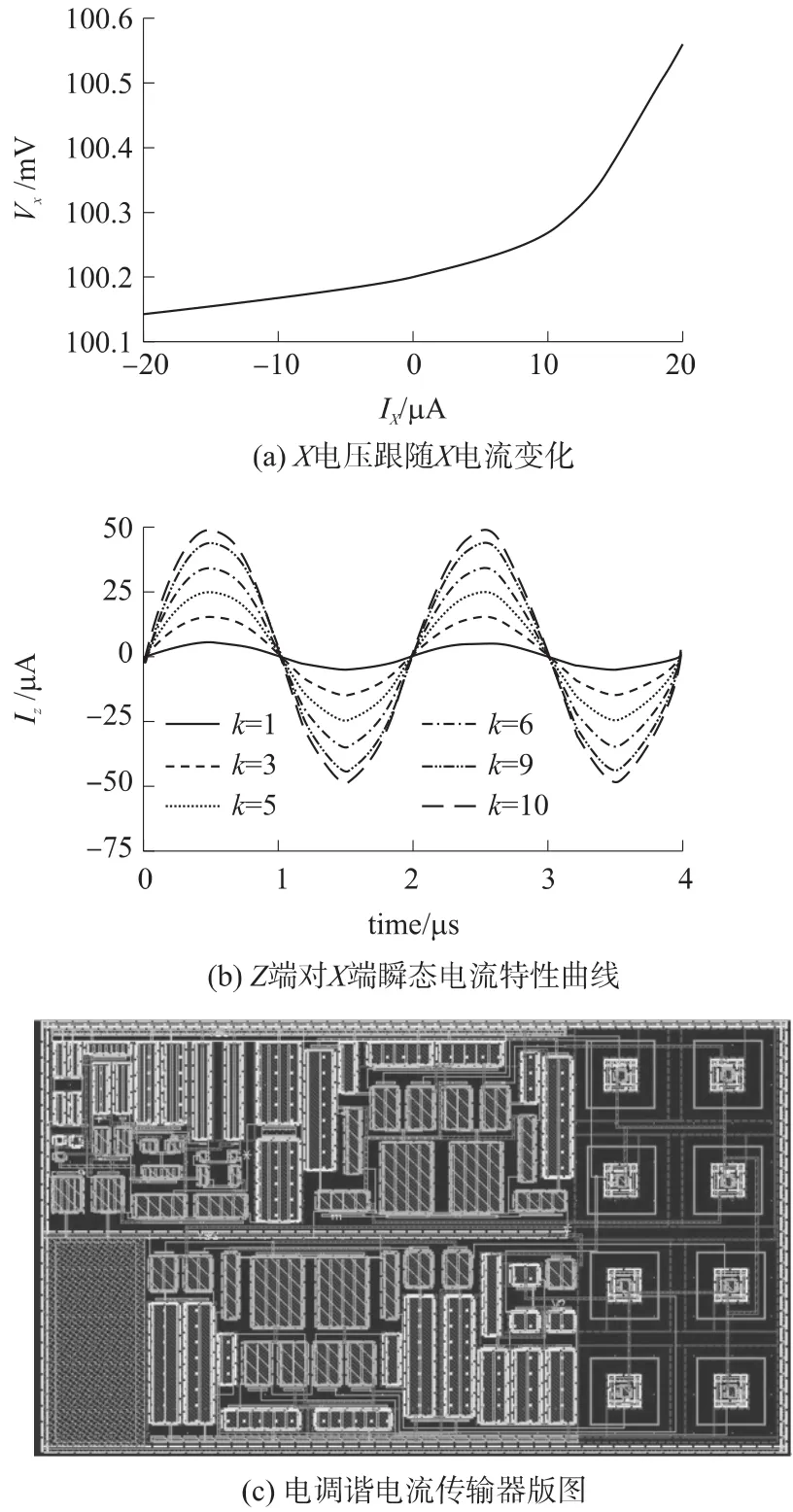

ECCII的前级采用轨对轨结构作为输入级,因此具有很大的共模电压输入范围,NMOS差分对管M4、M5和PMOS差分对管M6、M7作为轨对轨输入端。M11~M13形成自偏置结构,不需要加额外的偏置电压,即可将电流分别镜像到M1和M10,为差分对管提供偏置电流,M2、M3和M8、M9构成差分输入电路的有源负载。M22、M23、M24、M25构成共源共栅电流镜,M20、Mf分别连接到M22、M23的漏极,这样可以减小M2、M3之间的电流误差,同理,M18、M19连接到M14、M15、M16、M17组成的共源共栅电流镜,减小了M8、M9之间的电流误差,因此提高了电压跟随精度,通过小信号模型分析:

1.2.2基于正负极性差分差动电流传输器(DDCC±)的电流放大器

电路中采用了两个极性相反的电流放大器,起初通过偏置电路给他们提供相同的直流偏置,保证二极管工作在导通状态,最后在输出端偏置电流相互抵消,只保留信号电流。这样当X端输入交流小信号时,信号可以在Z端精确跟随,不会出现失真,因为在信号的整个周期内,二极管都工作在导通状态。正负极性的电流放大器分别由DDCC+、DDCC-和二极管构成。二极管采用图2中的连接方式与DDCC连接。DDCC+中所有晶体管均工作在饱和区,除差分对管M3A、M4A、M5A、M6A外,其余管子的源极均与衬底连接,因此可以忽略体效应对阈值电压的影响。体效应对于差分对管M3A、M4A、M5A、M6A的阈值电压具有相同的变化量影响,因此也可以忽略,所以整个这部分电路中晶体管的阈值电压不受体效应影响。晶体管M38~M41用来减小M1A与M2A之间的电流误差,提高电路的跟随精度。M40、M42提供负反馈,确保X端的电压尽量独立于流过X端的电流。同理,DDCC-只是将输出的电流极性取反,其余部分工作原理和DDCC+相同。

1.2.3偏置电路

考虑二级管的单向导通性,确保输出电流不失真,需要一个偏置电路给电流放大器的输入端提供偏置,晶体管M30~M37构成偏置电路,M36、M37是分压电阻,M30~M34构成低压共源共栅电流镜[6],M32、M35将电流同比例镜像出来。采用低压共源共栅电流镜是考虑既可以提高电流传输的精度,又可以降低电压余度的消耗。

2 电路仿真结果与分析

为了验证电路的实际性能,对图4中的电调谐电流传输器电路用Spectre进行模拟仿真。仿真参数采用SMIC 0.18 μm CMOS工艺参数,电源电压VDD = -VSS=1 V,V1=-500 mV,V2=-100 mV,V3=-750 mV,Ib=10 μA,M30~M35构成的低压共源共栅电流提供的偏置电流为20 μA,电路的静态功耗为1.642 4 mW。

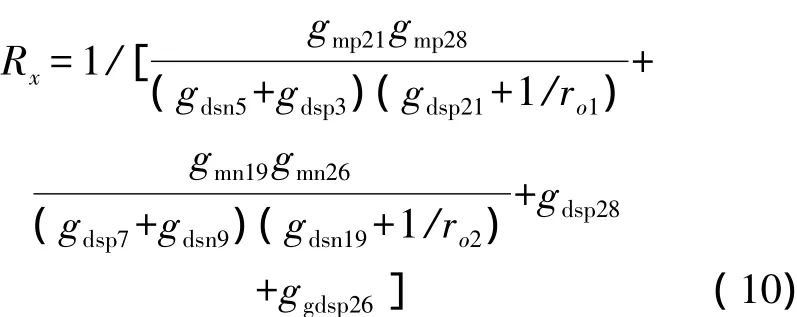

首先分析静态特性,X端接阻抗为10 kΩ的电阻,扫描Y端-1 V~1 V之间的直流电压,得到图5(a)所示的X端跟随Y端的电压静态特性曲线。从图5(a)可以看出,在-1 V~1 V的范围内,X端电压精确跟随Y端电压。当Z端接10 kΩ负载,在Ia=Ia1分别取10 μA、30 μA、50 μA、70 μA、90 μA、100 μA时,扫描Z端电流跟随X端电流的特性曲线,扫描范围为-20 μA~20 μA,Z端电流跟随X端电流特性曲线如图5(b)所示,由图可知,在给定的偏置电流范围内,调节系数k最大可达到10。

图5 静态特性

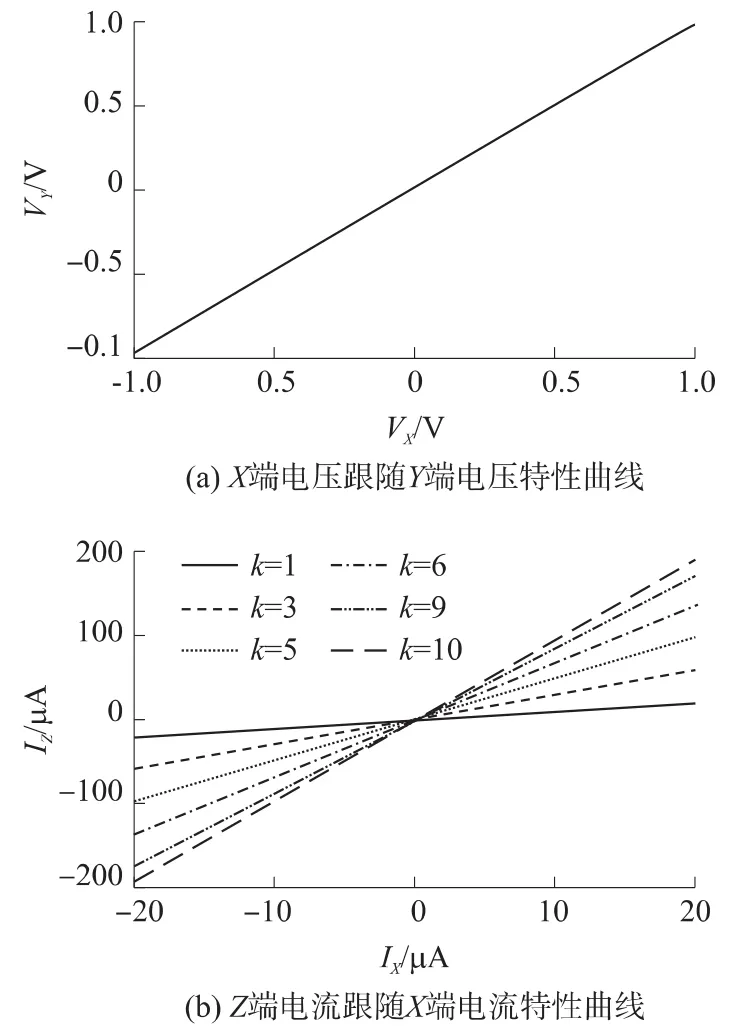

再分析电路中X端电压跟随Y端电压的交流特性,X端接10 kΩ电阻,Y端加幅度为100 mV,频率为1 MHz的正弦交流信号,在曲线平坦范围内vx/vy=0.997,-3 dB带宽为300 MHz,传输特性曲线如图6(a)所示。当Z端接10 kΩ负载,在Ia=Ia1分别取10 μA、30 μA、50 μA、70 μA、90 μA、100 μA时,测试Z端电流对X端电流的交流传输特性,测试结果如图6 (b)所示,当Ia= Ia1= 10 μA,即k=1时,在曲线较平坦的范围内满足iz/ix= 1.004,-3 dB带宽155 MHz。

图6 传输特性曲线

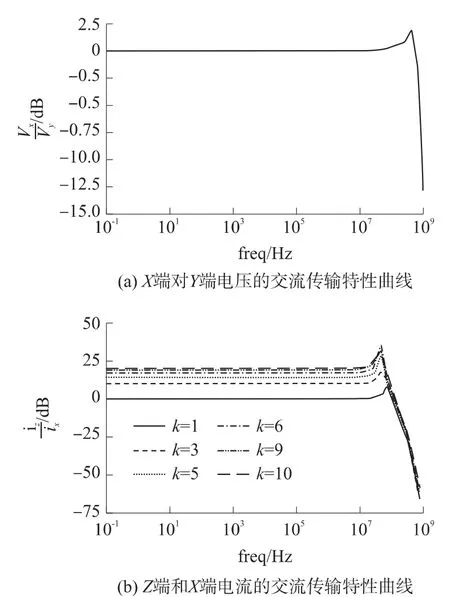

最后测试了X端口寄生电阻及Z端对X端瞬态电流特性曲线。图7(a)即为X电压跟随X电流变化关系,由图可得X端寄生电阻小于36 Ω。当X端输入幅度为5 μA,频率为500 kHz的正弦信号,Z端接10 kΩ负载,在Ia=Ia1分别取10 μA、30 μA、50 μA、70 μA、90 μA、100 μA时,分析了Z端对X端瞬态电流特性关系,如图7(b)所示。电流传输器版图设计使用SMIC 0.18 μm CMOS工艺来实现,版图面积约为95 μm×55 μm,如图7(c)所示。

图7 传输电流特性曲线及传输器版图

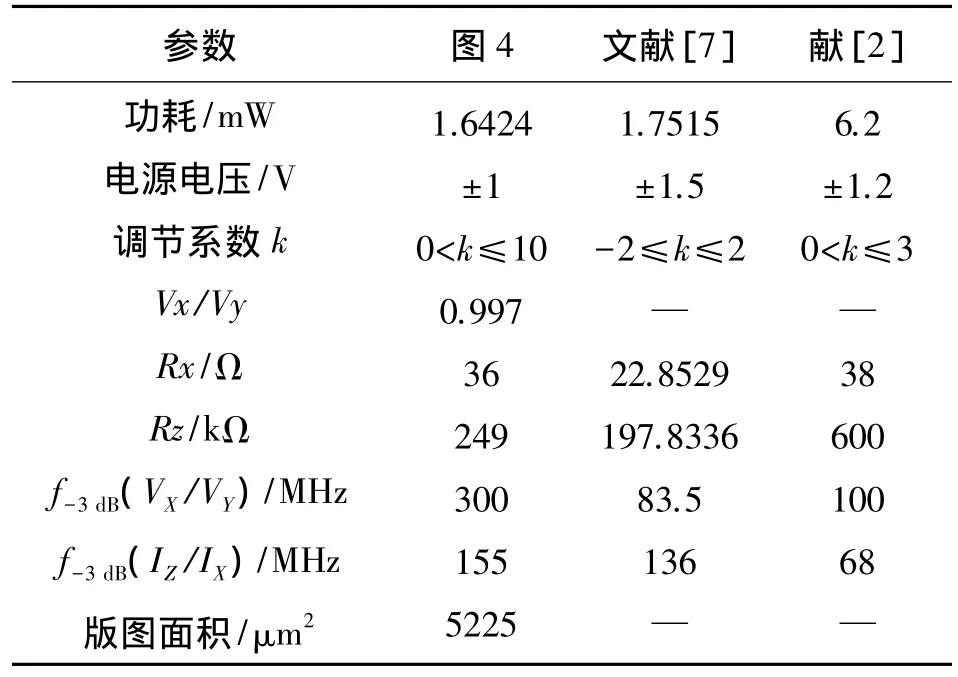

表1列出了图4电路性能参数与文献[2,7]对比结果,从表中可以看出,相比于参考文献[2,7],电路具有更大的调节系数k,更宽的带宽以及较低的功耗。

表1 提出电路与参考文献电路性能参数比较

3 提出电路应用于滤波器的设计

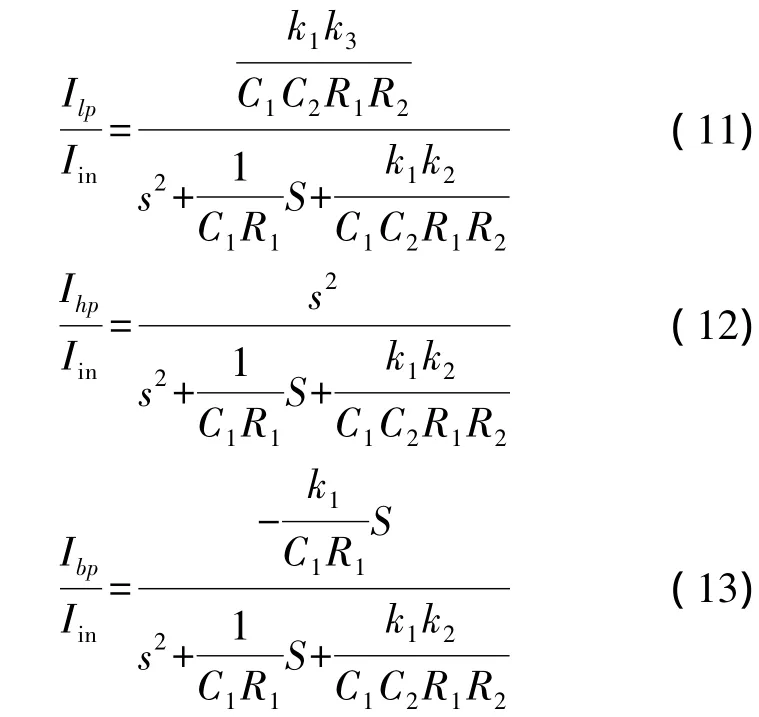

为了验证提出电调谐电流传输器的性能,参考文献[8]中的结构,如图8所示,将其应用于滤波器的设计[8-12],由图8可知:

图8 利用ECCII构成的滤波器电路

式中:ki是ECCII+的电流增益,低通和高通滤波器的增益分别为k3/k2,1和-k1,特征频率ω0和品质因子Q的表达式如下所示:

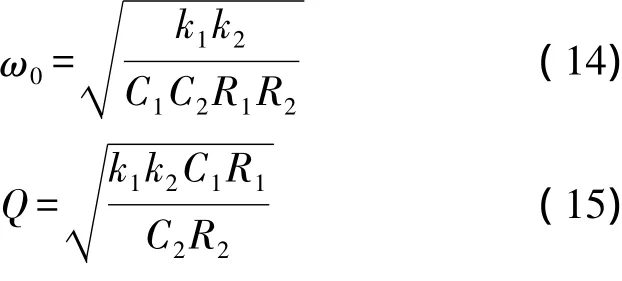

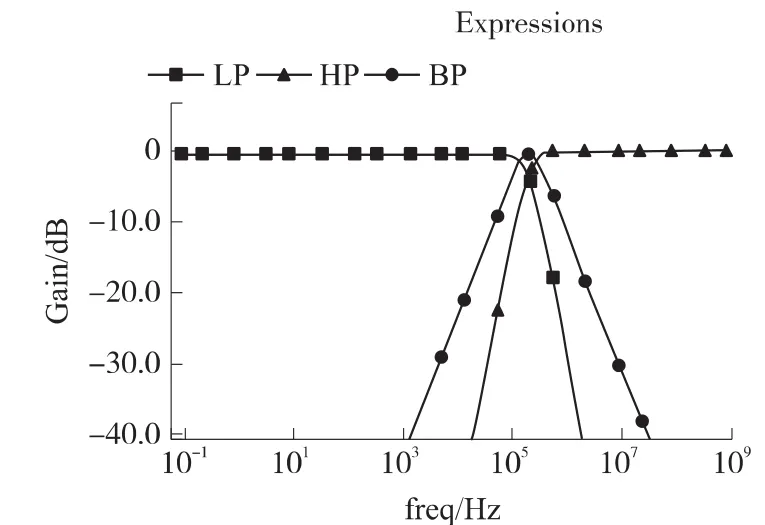

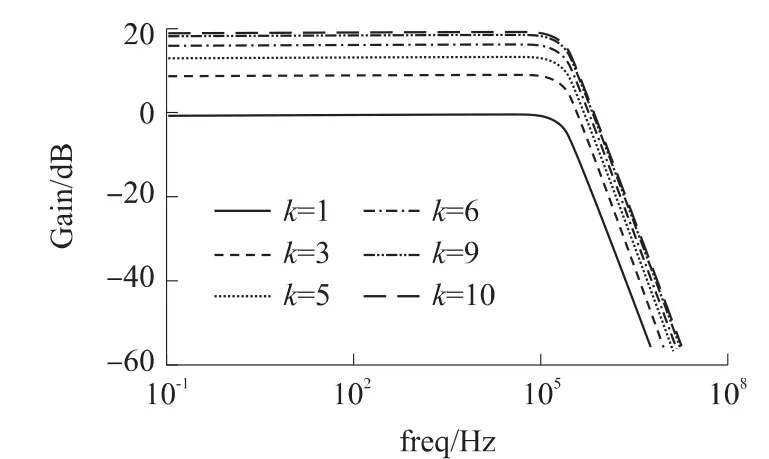

通过以上分析,令C1= C2= 100 pF,R1= 5 kΩ,R2=10 kΩ,k1=k2=1,则Q=0.707,特征频率f0=225 kHz,当k3=1,如图9可得滤波器的低通、高通、带通曲线,测得实际的特征频率为223 kHz,与理论值f0= 225 kHz十分接近。在不改变其他参数的情况下,可以通过调节k3改变低通滤波器的增益,本文测试了k3从1调节到10时的低通曲线,如图10所示,当k3=10时,最大增益达到20 dB,与理论值相符。

图9 所构成滤波器的低通、高通、带通曲线

图10 低通滤波器的增益可调特性曲线

4 结束语

本文提出了基于对数反对数电流放大器宽可调范围的新型CMOS电调谐第二代电流传输器(ECCII),该电流传输器具有输入电压动态范围大,跟随精度高、电流传输增益可调范围大的特点,增益调节因子0<k≤10。采用SMIC 0.18 μm CMOS工艺参数,在±1 V的供电电源条件下,用Spectre对电路进行仿真,vx/vy、iz/ix的-3 dB带宽分别为300 MHz和155 MHz,电压跟随精度为0.997,功耗仅为1.642 4 mW。经验证,提出的电调谐第二代电流传输器可用于设计可调谐连续时间电流模式滤波器。

参考文献:

[1]宋树详,严国萍.一种新型CMOS电谐调第二代电流传输器(ECCII)[J].半导体技术,2007,32(12) :1077-1080.

[2]Song Shuxiang,Xie Hongguo,Huang Shoulin.A New CMOS Electronically Tunable Current Conveyor Based on Programmable Current Amplifier[C]/ /Proc ICEICE,2011:1043-1046.

[3]Hu Jianping,Xia Yinshui,Xu Tiefeng.A New CMOS Differential Difference Current Conveyor and Its Applications[C]/ /Proc ICCCAS,2004,2(6) :1156-1160.

[4]Kumngern M.A New CMOS Second Generation Current Conveyor with Variable Current[C]/ /Proc ICCAS,2012(10) :272-275.

[5]Tare M H,Soliman A M.New CMOS DVCC Realization and Application to Instrumentation Amplifier and Active RC Filters[J].International Journal of Electronics and Communications,2010,64(1) :47-45.

[6]毕查德·拉扎维.模拟CMOS集成电路设计[M].陈贵灿,程军,张瑞智,等译.西安:西安交通大学出版社,2003:116-121.

[7]李沁莲,陈向东,王丽娜,等.一种电压控制CMOS电调谐第二代电流传输器(ECCⅡ)[J].微电子学与计算机,2011,28(6) :62-66.

[8]Shahra Minaei,Onur Korhan Sayin,Hakan Kuntman.A New CMOS Electronically Tunable Current Conveyor and Its Application to Current-Mode Filters[J].IEEE Transactions on Circuits and Systems,2006,53(7) :1448-1457.

[9]王卫东.现代模拟集成电路原理及应用[M].北京:电子工业出版社,2008:222-225.

[10]Abolila A H M,Hamed H F A,Hasaneen E S A M.High Performance Wideband CMOS Current Conveyorfor Low Voltage Low Power Applications[J].Proc ISSPIT,2010:433-438.

[11]Abdalla K,Bhaskar D,Senani R.Configuration for Realising a Current-Mode Universal Filter and Dual-Mode Quadrature Single Resistor Controlled Oscillator[J].Circuits,Devices and Systems,IET,2012,6(3) :159-167.

[12]Alzaher H,Tasadduq N,Al-Ammari S.Optimal Low Power Complex Filters[J].IEEE Transactions on Circuits and Systems,2013,60(4) :885-895.

胡许光(1989-),男,汉族,安徽安庆人,桂林电子科技大学信息与通信学院硕士研究生,研究方向为专用集成电路设计,1059479910@ qq.com;

王卫东(1956-),男,汉族,桂林电子科技大学硕士生导师,教授,主要研究方向为模拟集成电路及电流模技术方面的研究。

Design of a Logic Circuit to Improve LED Driver Visual Refresh Rate

LI Guanhua,WANG Weidong*

(School of Information and Communication Engineering,Guilin University of Electronic Technology,Guilin Guangxi 541004,China)

Abstract:In order to improve the quality of image of LED display,a logic circuit which can improve the LED display visual refresh rate was designed.A display cycle can be divided into 32 segments in the circuit,each segment consists of 128 gray clocks cycle,and duty cycle is controlled by 12 bit gray-scale data.Compared with traditional PWM and S-PWM,the logic circuit of PWM can improve visual refresh rate,the maximum visual refresh rate can be increased 32 times; and it can also make up shortcoming of the S-PWM(Scrambled-PWM) when at low gray-scale data.Simulation in Cadence software and verified the feasibility of the design on the development board.

Key words:LED display; logic circuit; pulse width modulation; refresh rate

中图分类号:TN432

文献标识码:A

文章编号:1005-9490(2015) 03-0521-05

收稿日期:2014-06-28修改日期:2014-07-22

doi:EEACC:4260D; 1250B10.3969/j.issn.1005-9490.2015.03.011