双非门结构皮秒级窄脉冲设计*

2015-02-25赵红梅王园璞崔光照

赵红梅,王园璞,崔光照

(郑州轻工业学院电气信息工程学院,郑州450000)

双非门结构皮秒级窄脉冲设计*

赵红梅*,王园璞,崔光照

(郑州轻工业学院电气信息工程学院,郑州450000)

摘要:窄脉冲的产生是超宽带通信系统中的一项关键技术,不同的应用对脉冲的产生方法有不同的要求。文中分析了超宽带室内定位系统中几种常规的超宽带窄脉冲产生方法,比较了它们的优缺点,对存在的问题进行了研究。在此基础上首先设计了一种基于数字方法的脉冲发生器,通过对该脉冲发生器的仿真分析提出了一种基于双非门结构的超宽带窄脉冲的产生方法,仿真结果表明,利用该方法得到的脉冲重复频率为10 MHz,宽度为150 ps。实验电路测试结果与理论分析和仿真结果基本一致。相电路比常规的数字电路窄脉冲产生方法,该设计方法不仅电路简单,对器件的要求不高,成本低,而且脉冲宽度变窄了十几倍,定位精度更高。

关键词:超宽带;皮秒级窄脉冲;数字电路;竞争冒险现象;双非门

超宽带UWB(Ultra-Wideband)是近年来一种全新的无线通信技术,其通常利用宽度在纳秒甚至亚纳秒级的脉冲信号来实现高速率的数据传输。与其他无线通信技术相比,超宽带无线电系统不仅具有隐蔽性好、抗多径和窄带干扰能力强、数据传输速率高、空间容量大、穿透能力强、低功耗、低成本等一系列优点,而且可以达到频谱资源共享的目的,很好地解决了频谱资源日趋紧张的问题。当采用较高的发射功率时,超宽带脉冲信号可以穿透墙壁,探测到隐藏在墙壁或者其他障碍物后面的人员等目标,成为当下室内探测定位的首选技术[1-2]。

UWB室内定位技术要求发送的脉冲具有较高的功率利用率、合适的波形、良好的上升和下降沿、高的重复频率,同时要求脉冲产生电路具有体积小、结构简单、功耗低、重量轻等特点。因此,高速窄脉冲的产生是UWB室内定位技术中的一项关键技术。

1 现有的超宽带窄脉冲的产生方法

目前产生UWB窄脉冲的方法有很多,大体上可以分为3类:

第1类是将各种高速器件等效成开关,从而利用储能元件的充放电得到短持续时间的信号,再经过脉冲成形网络整形成满足要求的脉冲波形。采这类方法的核心是各种高速器件的选取,高速器件包括光电器件和各种高速的电子器件,例如隧道二极管、阶跃恢复二极管、雪崩晶体管等。这些器件产生的脉冲发生器原理各异,产生脉冲的特性也是各有特点[3-6]。

第2类是利用几种简单易控制的波形来合成窄脉冲的波形合成技术,比如傅里叶系数合成方式、小波合成技术等。利用此种方法是为了克服基于电器件特性产生的窄脉冲形状不易控制,能量效率低,难以保持精确的脉冲重复频率等缺点[7]。其间考虑更多的是数学方面的问题,这种电路较为复杂,实现较难。

第3类是采用数字电路中的竞争冒险现象产生窄脉冲,这种方法主要是从时域出发预选某种时间域函数,然后根据参数来调节波形使得该波形满足FCC的频谱规范。脉冲产生器最易产生的脉冲其实是一个钟形波形,类似高斯函数波形。文献[8-10]分别采用了晶体管—晶体管逻辑(TTL)电路、发射极耦合逻辑(ECL)电路来实现UWB脉冲的产生。此种方法的电路结构相对简单而且成本低廉,易于集成。

采用隧道二极管、阶跃恢复二极管、雪崩晶体管等模拟器件产生UWB脉冲信号的方法是利用了器件的开关特性,产生的均为模拟信号。UWB脉冲的各种调制方式如DS-BPSK(直接序列扩频—二进制异相键控)、TH-PPM(跳时—脉冲位置调制)等是将数字信息加载到脉冲上来实现数据的传输。如果脉冲的产生是利用模拟电路,产生的模拟信号与脉冲调制部分的数字信号将会产生很大的干扰,必须将模拟与数字信号进行隔离,或者将脉冲产生与调制分别设计于不同的电路板,否则会产生严重的信号失真[11-12]。这就增加了发射系统设计的复杂度,不利于UWB信号发射电路的小型化设计。同时,出于对电路集成成本的考虑,需要有更简单、更适合于数字电路系统兼容的超宽带信号产生方法。基于此本文主要研究分析了利用数字电路产生窄脉冲的实现方法,通过选择合适的逻辑芯片设计了一种基于数字逻辑器件的脉冲发生器。在对所设计的脉冲发生器进行仿真分析之后提出了一种基于双非门结构的ps级UWB窄脉冲的产生方法。

2 基于数字逻辑门电路的UWB脉冲发生器设计

采用数字电路产生窄脉冲只要是利用数字组合逻辑门电路的竞争冒险现象来产生的。这样的器件包括晶体管-晶体管逻辑(TTL)电路、金属氧化物半导体场效应管(MOS)电路、发射极耦合逻辑(ECL)电路以及集成注入逻辑(I2L)电路等。利用这类器件组成的脉冲产生电路结构简单、成本低且便于集成,利用上述不同器件产生的窄脉冲信号各有特点,可以满足不同的需要,在无线通信等领域都得到了广泛的应用。

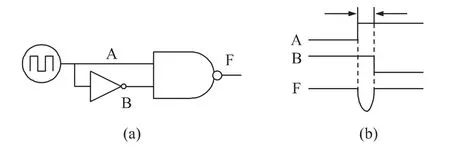

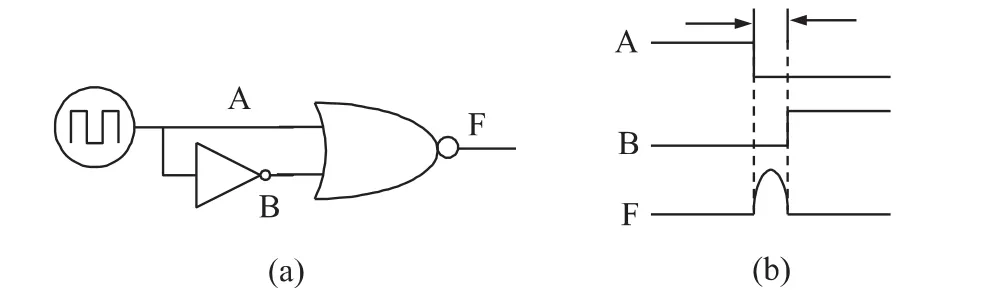

其实现方法主要有两种:一种是采用两输入端与非门(NAND)产生窄脉冲,如图1(a)、1(b)所示,其逻辑表达式为:另一种是采用两输入端或非门(NOR)产生窄脉冲,如图2(a)、2(b)所示,其逻辑表达式为:。

图1 采用两输入端与非门产生窄脉冲

图2 采用两输入端或非门产生窄脉冲

这两种方式产生窄脉冲的上升、下降沿由选用器件的开关特性来决定,它们产生的窄脉冲近似钟形,类似于高斯函数波形,可以用下列表达式描述:

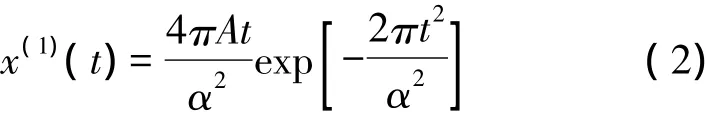

式中:A为脉冲峰值幅度,α为高斯脉冲的形成因子。高斯脉冲具有很大的直流分量,工程应用价值不大,一般仅用于学术研究。为了有效辐射,工程上常用的超宽带脉冲应该没有直流分量,一般通过对高斯脉冲求导获得[13],例如,对高斯脉冲求一阶导数可以获得高斯单周期脉冲,表达式如下:

根据以上原理可以看出,采用数字方法产生窄脉冲难度最大的地方在于高速逻辑的实现和精确的相位延迟的控制。目前在市场上可以方便地买到这些高速逻辑芯片,在实际设计过程中,应该注意选择上升沿时间尽量短的时钟信号作为激励源,以确保相位延迟的精确控制,并且还要考虑芯片之间的阻抗匹配等问题。

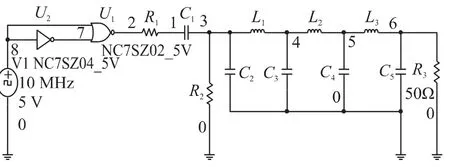

本文在数字电路产生窄脉冲方法的基础上设计了一种脉冲发生器,其电路图如图3所示。该电路采用的是两输入端或非门产生窄脉冲,所选用的高速逻辑器件NC7SZ02或非门和NC7SZ04非门是飞兆仙童半导体公司(Fairchild Semiconductor)的低ICCT逻辑门TinyLogic器件。TinyLogic低ICCT逻辑门相比标准CMOS产品,静态功耗减少多达99%,所选器件的超高速体现于在5V电源电压的驱动下典型延迟时间为2.4ns[14],比TTL逻辑门的74F系列的延迟时间还要小。

图3 采用数字组合逻辑电路产生窄脉冲电路图

本文所设计的数字电路脉冲发生器其输入信号采用的是10 MHz的晶振提供的基带方波信号。虽然理论上激励时钟信号的上升时间对脉冲的宽度没有影响,但是考虑到器件的非理想性,应选择上升时间尽量短的时钟信号作为激励源,所以在实现实际电路的制作时,时钟信号应先经过两个非门,以使输入的激励信号具有足够陡峭的上升沿和幅度,之后再分为两路分别输入到非门NC7SZ04和或非门NC7SZ02的一个输入端。时钟信号经过非门NC7SZ04后会产生一个极性相反、有足够陡峭的上升沿和幅度的信号,该信号和时钟信号经过或非门NC7SZ02后产生一个窄脉冲。此窄脉冲的宽度是由非门的延迟时间来决定的。电路后端的微分滤波电路主要用来完成脉冲的成形,通过调整RLC的参数,就可以得到适合UWB传输的高斯单周期脉冲。另外,在实际电路的制作中,由于传输的是高速的脉冲信号,所以电路的布线也会对脉冲的延迟时间造成影响。

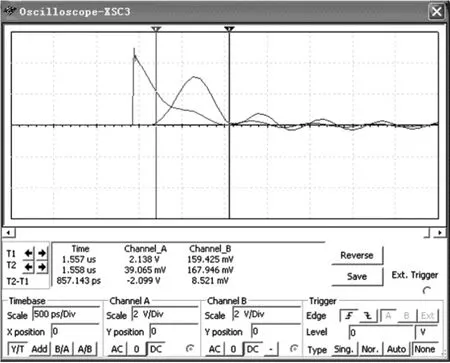

利用Electronic Workbench Multisim 10.0软件对电路进行了仿真。仿真波形如图4所示。其结果可得到重复频率为10 MHz,脉冲幅度为3.1 V,脉冲宽度为857 ps的窄脉冲。

由以上设计的数字电路脉冲发生器可知利用数字组合逻辑电路中的竞争冒险现象来产生UWB窄脉冲结构简单,成本低廉,易于集成。但是,此种电路脉冲宽度完全由非门的延迟量来决定,脉冲宽度不可控,如果要得到极窄的脉冲必须选择延时量极小的逻辑器件。若采用可编程延时芯片来替代电路中的非门,将能够实现产生的窄脉冲宽度可控,可以采用FPGA或者DSP来控制电路中的脉冲延时[15]。

图4 脉冲信号的仿真波形

3 基于双非门结构的窄脉冲产生方法

利用数字逻辑器件的竞争冒险现象产生窄脉冲,脉冲的持续时间完全由非门的延时决定,选择合适的非门延迟芯片就能得到不同宽度的窄脉冲,脉冲的宽度受非门的延迟的控制,目前使用的高速逻辑器件的非门大部分的延迟都在纳秒级,如在5 V电源电压驱动下74S04的典型延时为3 ns,74F04的典型延时为3.7 ns,NC7SZ04的典型延时为2.4 ns,74HC04的典型延迟时间为7 ns,这大大限制了极窄脉冲的产生,而利用几个延时相近的高速逻辑器件的延时差却远远的小于单个器件的延迟,因此本文在已经设计的脉冲发生器的基础上提出了一种利用两个延迟差极小的逻辑非门产生皮秒级脉冲的方法,该方法由于利用两个逻辑非门的延迟差,对器件的要求不高。图5为所提出的电路设计方案。

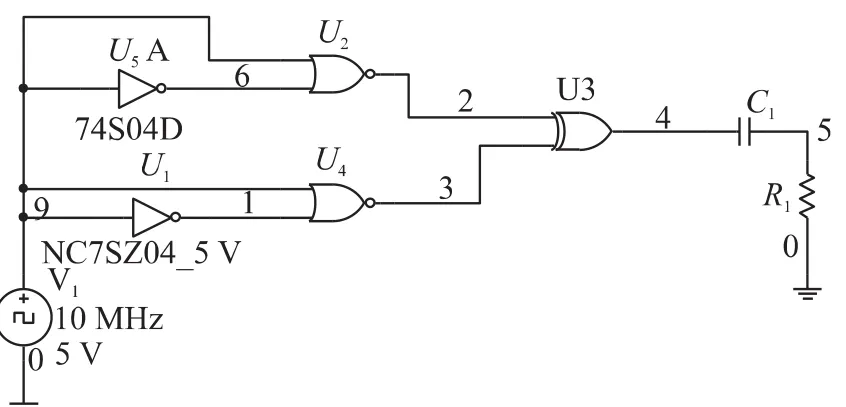

图5 双非门结构脉冲发生器电路图

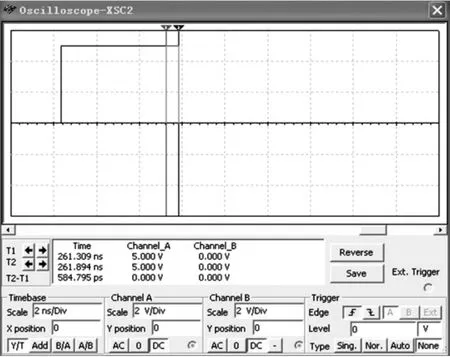

电路首先由74S04和NC7SZ04分别和时钟信号经过或非门之后得到两个不同宽度的窄脉冲,如图6仿真结果1所示。得到的两个脉冲宽度之差587 ps,就是所选择的两个非门的延时量之差。然后将这两路脉冲分别输入异或门得到最后的窄脉冲。由于得到的脉冲含有丰富的低频和直流分量,不适宜天线辐射,为了有效传输,UWB信号应含有尽可能多的高频分量,所以在经过逻辑电路之后,又通过微分电路对脉冲进行整形以获得适合UWB传输的高斯单周期脉冲。经过微分电路之后得到的脉冲波形如图7仿真结果2所示。

图6 脉冲发生器仿真结果1

图7 脉冲发生器仿真结果2

从图7中可以看到,经过微分整形电路之后得到的脉冲宽度为150 ps。将该结果与图4中的仿真结果比较分析,发现脉冲的宽度明显变窄。时域脉冲的宽度越窄,频域的频谱宽度也随之增加,而且频带的中心频率也随着脉冲的变窄而升高。同时由于采用了两级电路的缘故,严格的抑制了之前脉冲的拖尾和抖动现象。

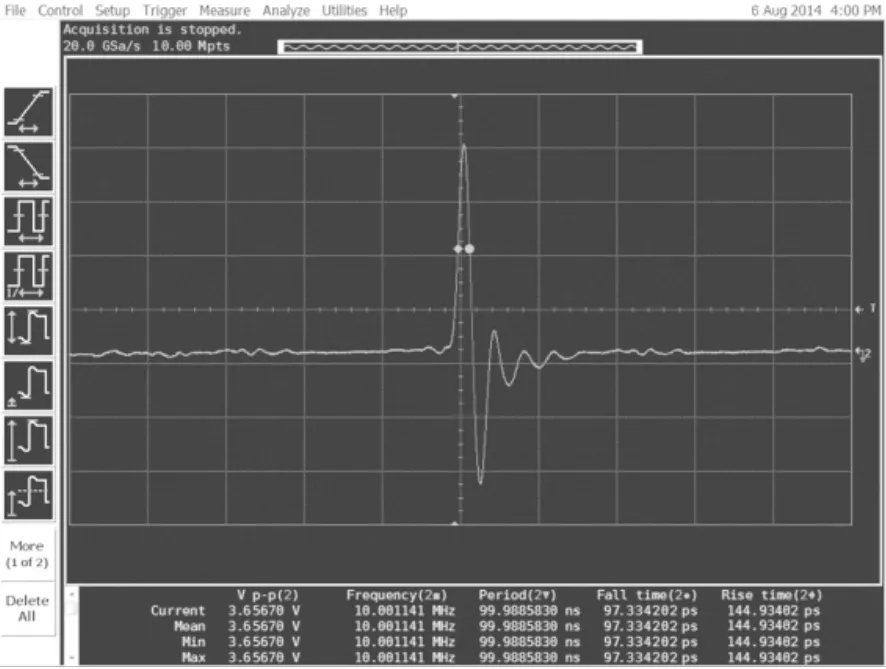

根据仿真结果的元件值和电路结构,本文对双非门结构的脉冲发生器进行了实物的制作和测试,测试采用的是Agilent MSO9404A高宽带数字滤波器(带宽为4 GHz,最高采样速率达25 GHz),测试结果如图8所示。从测试结果来看,与仿真结果基本一致,得到了重复频率为10 MHz,上升时间为145 ps,脉冲宽度约为290 ps的高斯单周期脉冲。测试时输入的触发信号是由10 MHz的晶振电路提供的方波信号,由于器件的非理想性,激励时钟信号的上升沿时间会对脉冲的宽度产生影响,同时考虑到芯片之间的阻抗匹配以及电路布线等因素都会使实测结果与仿真结果产生一定的偏差,不过这都在可接受的误差范围之内。

图8 脉冲发生器实测结果

4 总结

针对超宽带室内定位系统的应用,文中对几种常用的窄脉冲的产生方法进行了比较分析,着重分析了利用数字电路产生窄脉冲的方法。在此基础首先设计了一种简单的UWB脉冲发生器,通过对该脉冲发生器仿真结果的分析,本文又提出了一种双非门结构的超宽带窄脉冲的产生方法,仿真结果表明,采用该方法可以得到重复频率为10 MHz,持续时间为150 ps的窄脉冲,实物测试结果与仿真结果基本一致。采用这种方法与常规的数字电路的设计方法相比较,不仅对数字逻辑器件的要求不高,而且脉冲宽度变窄的十几倍,极大的提高了室内定位精度。

参考文献:

[1]赵光旭.监狱服刑人员三维精确定位系统研究与设计[D].辽宁工业大学,2014.

[2]李慧.超宽带脉冲通信技术研究[J].信息通信,2013(2) :16-17.

[3]Han J,Nguyen C.A New Ultra-Wideband,Ultra-Short Monocycle Pulse Generator with Reduced Ringing[J].IEEE Microwave and Wireless Components Letters,2002,12(6) :206-208.

[4]刘博.微小型超宽带收发技术研究[D].南京:南京理工大学,2014.

[5]姜苹.基于光导开关的纳秒脉冲功率源技术研究[D].中国工程物理研究院,2012.

[6]赵陈亮.典型超宽带信号的发射与接收技术[D].南京:南京理工大学,2013.

[7]赵延明,陈长兴,牛徳智,等.基于小波的优化组合认知超宽带波形设计方法[J].空军工程大学学报,2014,15(1) :77-81.

[8]关炜,陈锡华,余芬.一种基于数字方式的超宽带纳秒级窄脉冲设计[J].桂林航天工业高等专科学校学报,2007,45:7-9.

[9]黄堂森,梁小芝.基于ECL门电路的UWB信号发生器的设计[J].现代电子技术,2009,306:35-37.

[10]赵红梅,马琳琳,崔光照.一种简易的超宽带纳秒级脉冲发生器设计[J].现代电子技术,2012,35(19) :12-14.

[11]张海平.超宽带(UWB)窄脉冲发生的研究[D].西南交通大学,2007.

[12]贾占彪,朱爱民,李正华,等.超宽带抗干扰性能分析[J].云南大学学报,2014,36(1) :40-44.

[13]关炜,林基明.基于高速数字逻辑器件的超宽带脉冲设计和应用[J].火力与指挥控制,2009,34(5) :138-141.

[14]www.cecb2b.com.NC7SZ04 TinyLogicTMUHS Invert[OL/EB].http:/ /wenku.baidu.com/link.2014:4.

[15]李晓欢,陈倩,李全,等.基于FPGA的TH-UWB窄脉冲信号发生器设计与实现[J].半导体技术,2011,33(4) :336-338.

[16]张继红,方毅,黄鲁.一种低功耗OOK调制超宽带发射机的实现[J].微电子学,2014,44(2) :174-177.

[17]高睿劼,黄鲁,朱警怡.UWB室内定位系统的射频收发机设计[J].微型机与应用,2013,32(13) :87-89.

赵红梅(1976-),女,汉族,河南辉县人,郑州轻工业学院,副教授,博士,硕士生导师。研究方向为微波射频技术、超宽带无线通信,微带天线设计,zhhm@ zzuli.edu.cn;

王园璞(1988-),女,汉族,河南登封市人,郑州轻工业学院,硕士生,研究方向为超宽带无线通信技术,wang1012670157 @163.com;

崔光照(1957-),男,汉族,郑州轻工业学院,教授,博士,硕士生导师。研究方向为控制算法、智能计算等。

Design of Chua’s Circuit Based on Piecewise-Linear Positive Resistance*

LÜEnsheng*,BAI Jinke

(Department of Mechanical and Electrical Engineering,Henan Vocational College of Chemical Technology,Zhengzhou 450042,China)

Abstract:To simplify design of the Chua’s diode,a design method based on piecewise-linear positive resistance is proposed.The design of piecewise-linear positive resistance into piecewise-linear negative resistance,design of new Chua’s circuit based on the piecewise-linear negative resistance,EWB simulation and hardware circuit testing show that Chua’s circuit can effectively generate chaotic behavior.Both the chaotic behaviors or structure of circuit occupy the advantages which are not existing in the Chua’s circuits,the results show the design of this circuit is effective.Key words:Chua’s circuit; piecewise-linear positive resistance; chaotic circuit; circuit simulation

中图分类号:TN722.3

文献标识码:A

文章编号:1005-9490(2015) 03-0548-05

收稿日期:2014-07-05修改日期:2014-09-20

doi:EEACC:120010.3969/j.issn.1005-9490.2015.03.016