高速数据采集系统中USB3.0数据传输接口设计

2015-02-23杨少博裴东兴岳孝忠

杨少博,裴东兴*,岳孝忠

(1.中北大学电子测试技术国家重点实验室,太原030051; 2.中北大学仪器科学与动态测试教育部重点实验室,太原030051)

高速数据采集系统中USB3.0数据传输接口设计

杨少博1,2,裴东兴1,2*,岳孝忠1,2

(1.中北大学电子测试技术国家重点实验室,太原030051; 2.中北大学仪器科学与动态测试教育部重点实验室,太原030051)

摘要:高速稳定可靠的数据传输在高速数据采集系统中扮演着重要的角色。针对弹载电子测试仪对高速数据传输的要求,设计了一个基于USB3.0的高速数据采集传输系统。该系统数据传输部分采用Cypress公司CYUSB3014芯片作为接口芯片,详细介绍了接口连接及硬件工作过程;介绍了USB3.0接口的软件设计主要模块,如DMA通道、GPIFⅡ可编程接口等固件编程。实际测试表明:该系统实现了数据高速可靠传输,固件程序能够正常稳定的运行。

关键词:存储测试;高速数据采集;高速数据传输; USB3.0接口

高速数据采集系统中,为了保证处理器能够正确的处理A/D输出的数据,数据的正确传输和存储显得非常重要。实验室一直致力于高速数据传输接口的研究,近年来随着大容量存储器的发展,存储容量已经提升到GB级别,基于USB2.0的数据传输接口已逐渐不能满足测试需要,USB3.0的出现为这一难题的解决提供了新的方向。在这种背景下,利用存储测试方法[1-2]研究设计了适合在恶劣环境下实现动态测试的小型高速数据采集传输系统,该系统能够放在高速炮中随炮弹一起发射,高速采集、存储编码信号;随后用超速传输设备USB3.0将信号传输显示,并将静态和动态的脉冲信号进行对比,更好地了解导弹、弹丸飞行过程的姿态参数的数据。本设计选用USB3.0芯片CYUSB3014作为接口芯片,不仅提高了数据传输的速率,还能保证数据传输的准确性与稳定性。

1 系统总体方案设计

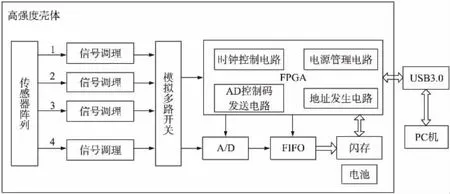

图1为实验室为准确测量引信在膛内及飞行过程的动态参数研制的可置于引信内部的弹载电子测试仪数据采集系统。该系统把弹上动态参数测试必不可少的功能部分放置到弹载电子测试仪上,而把尽可能多的功能部分,如接口、数据处理、显示等功能部件放置在地面。经过特殊系统校准及专门的恶劣环境可靠性考核系统考核,该系统可以适应弹载测试的恶劣环境。

图1 弹载电子测试仪数据采集系统

弹载电子测试仪完成被测参量的获取和存储记录,高强度壳体的有效防护可以提高仪器的存活性[3]。通过USB3.0传输接口,地面计算机完成对弹载电子测试仪的参数设置及实验数据的读取处理。图中传感器1为轴向安装的加速度传感器,传感器2和3为径向安装的加速度传感器,传感器4为实验室自制的地磁传感器[4]。

2 USB3.0接口硬件设计

2.1USB3.0硬件工作过程

EZ-USB FX3芯片CYUSB3014由Cypress公司研发,拥有一个高性能的32 bit ARM926EJ-S微处理器[5],该内核的工作频率可达200 MHz,使得FX3能够用在对数据处理要求较高的地方。芯片内部还集成了一个512 kbyte嵌入式SRAM,用来存储代码、配置参数,同时作为芯片内部DMA通道的缓冲区。它具备一个并行通用可编程接口GPIFⅡ(GPIFⅡ是Cypress公司USB2.0旗舰产品FX2[6]中GPIF的增强版本),它可与任何处理器、FPGA或ASIC等进行连接。CYUSB3014有两种配置方式:Slave FIFO模式和GPIF主控模式。本设计选用GPIFⅡ接口的Slave FIFO工作模式,与一片FPGA相连,实现高速数据传输系统的整个过程。USB3.0接口硬件框图如图2所示。

高速数据传输系统的硬件工作过程如下:首先,将系统与计算机相连,然后,系统上电,FX3芯片通过固化在EEPROM中固件程序加载系统,加载固件程序,调用子函数,初始化芯片内部寄存器和外围电路状态,USB设备被计算机正确识别后,上位机软件通过调用DLL使USB设备进入工作状态,执行固件中的读数子程序并开始读数,二者相互独立。本系统与USB3.0通信的FPGA芯片选用EP3C40F484,它具有体积小,处理速度快和散热性好等特点,借助FPGA强大的并行处理能力,协助FX3芯片完成高速数据传输。USB3.0接口为系统提供5 V电压,900 mA电流,电源管理芯片选用TPS650243,通过转换可以为CYUSB3014提供3.3 V电压,为EP3C40F484提供1.2 V工作电压。

图2 USB3.0接口硬件框图

图3 CYUSB3014与FPGA、PC机接口连接

2.2CYUSB3014与FPGA、PC机接口连接

CYUSB3014与FPGA、PC机接口连接如图3所示。USB3.0拥有8条线路:一对电源、地线和三对差分信号线。三对差分信号线分别为:D+和D-,SSTX+和SSTX-,SSRX+和SSRX-。相对与USB2.0,USB3.0新增的两对差分信号线SSTX+和SSTX-,SSRX+和SSRX-可保证数据进行并行的收发,专用的数据发送线路和独立的数据接收线路,支持全双工通信[7]。同时,USB3.0还兼容了USB2.0的D+/-信号接口,从而可以与USB2.0无缝连接。相比USB2.0,USB3.0数据传输速率更高,理论最高传输速率可达5.0 Gbit/s。另外,USB3.0采用的是更加人性化的中断驱动协议,在发出中断请求之前,USB3.0设备处于待机状态,不消耗电源电能[8]。

3 软件设计

3.1USB3.0固件设计

固件是在加电后,由EEPROM加载到CYUSB3014中并在其中运行,完成接口数据传送功能的一段程序,其作用是控制硬件来完成预期的设备功能。固件的主要功能包括:初始化设备;辅助硬件完成设备的重新枚举(Re-Numeration)过程;对主机请求做出响应;数据的接收与发送;对中断的处理;对外围电路的控制等。固件框架流程图如图4所示。

图4 固件框架流程图

USB3.0与USB2.0不同之处之一就是USB3.0涉及到不同固件数据流,这大大提高了数据传输速度。固件设计一个很重要的工作就是建立DMA数据通道,DMA通道用来连接两个套接字[9]。FX3提供了两种DMA通道模式,一种是自动DMA通道,另一种是手动DMA通道。GPIFⅡ接口和USB接口只能通过DMA通道进行数据传输。DMA系统引擎会向微处理器发送DMA事件中断信号,该信号用来通知微处理器有特定的DMA事件发生,当微处理器接收到特定的DMA事件时,就会调用相应的回调函数来处理这些DMA事件。手动创建DMA通道程序如下:

/*创建一个手动DMA通道* /

dmaBulkLpConfig.size = CY_FX_BULKLP_DMA_BUF_ SIZE;

dmaBulkLpConfig.count= CY_FX_BULKLP_DMA_BUF_ COUNT;

dmaBulkLpConfig.prodSckId = (CyU3PDmaSocketId_ t)(CY_U3P_UIB_SOCKET_PROD_0|

CY_FX_EP_PRODUCER_SOCKET);

dmaBulkLpConfig.consSckId = (CyU3PDmaSocketId_ t)(CY_U3P_UIB_SOCKET_CONS_0|

CY_FX_EP_CONSUMER_SOCKET);

dmaBulkLpConfig.dmaMode = CY_ U3P_ DMA_ MODE_ BYTE;

dmaBulkLpConfig.notification=CY_U3P_DMA_CB_PROD_ EVENT;

dmaBulkLpConfig.cb=CyFxBulkLpDmaCallback;

dmaBulkLpConfig.prodHeader=0;

dmaBulkLpConfig.prodFooter=0;

dmaBulkLpConfig.consHeader=0;

dmaBulkLpConfig.prodAvailCount=0;

apiRetStatus=CyU3PDmaChannelCreate

(&glChHandleBulkLp,CY_ U3P_ DMA_ TYPE_ MANUAL,&dmaBulkLpConfig);

3.2下位机程序设计

GPIFⅡ接口工作在Slave FIFO模式下,FPGA作为逻辑控制器,外部数字信号通过FPGA写入FX3,再通过USB3.0接口传输到计算机上。GPIFⅡ一侧的套接字(Socket)相当于端点。FX3可提供多达4个物理线程用于GPIFⅡ数据传输,将要使用的套接字映射至某个线程上,这种映射由固件完成。GPIFⅡ接口上的信号A1:A0表示要访问的线程,数据传输时,DMA结构将数据映射到该线程上的套接字[10]。GPIFⅡ是一种可编程状态机,使用GPIFⅡDesigner软件生成GPIFⅡ波形描述符加入到固件程序中,完成相关配置。使用QuartusⅡ9.1软件采用VHDL实现FPGA对USB3.0的逻辑时序控制,仿真结果如图5所示。

图5 FPGA对FX3逻辑控制仿真

DCLK为由FPGA控制GPIFⅡ的接口时钟; SLCS为片选,低电平有效,即选中FX3芯片; SLWR为写使能控制,低电平有效。FLAGA和FLAGB是FX3固件配置的标志位,它们可以配置为空、满、局部空或局部满状态信号,由FX3内部的DMA硬件引擎控制。数据传输接口系统中应用FLAGA作为当前线程套接字的满/不满状态标志。FIFO地址由A1:A0= 0确定线程0,FLAGA信号为高电平,表示套接字缓冲区不满,SLCS一直处于低电平使能状态,当应用程序通过GPIFⅡ的INT接口向FPGA发送一个高电平脉冲时,SLWR下拉至低电平,数据开始从时钟上升沿向套接字缓冲区写入数据,紧接着FX3会启动DMA通道;当缓冲区被装满数据,FLAGA信号下拉至低电平,相应的DMA回调函数被调用。PKTEND是数据包结束信号,低电平有效; SLOE是输出使能控制信号。

3.3驱动程序设计

Cypress公司为EZ-USB FX3系列提供的SDK开发包中含有通用cyusb3.sys驱动程序和与之相匹配的cyusb3.inf文件[11]。对于通用驱动程序而言,用户需要做的是根据固件程序中的PID和VID来修改INF文件。固件程序中定义了VID = 04B4与PID = 00F1,修改INF文件后保存,系统就能根据INF文件识别USB3.0设备加载驱动程序,USB设备启动后用户就可以对它进行一些正常的操作。

4 测试结果分析

利用第3方工具软件Eclipse IDE建立工程,调试FX3固件,自动生成ELF二进制文件,这些二进制文件在Eclipse工程中利用elf2img工具可被转换成二进制img格式文件。硬件连接好后,利用Cypress公司提供的USB control center软件可以下载img文件到FX3芯片中,完成固件下载。

弹载电子测试仪已在靶场进行了20余次实弹测试,成功获取了某引信在膛内和飞行过程的加速度参数,数据捕获率为高达96%。图6为某次实弹测试轴向加速度测试结果部分截图,图7为利用Cypress公司Streamer软件测试的该USB3.0系统的数据传输速率,在win7 64位操作系统下传输速率测试结果为191 300 kbyte/s,实现了高速数据传输的要求,比以往使用的USB2.0接口传输速率更快,并且无点的丢失。在发射的同时使用天幕靶对弹丸的初速进行测试,通过对引信轴向加速度信号的积分可得出弹丸在膛内的速度曲线,计算出引信在出炮口的最大速度和所测的初速相差6 m/s,验证了测试数据的正确性[12]。测试结果表明本高速数据传输系统在测试中的可靠性和实用性,也表明本数据采集系统可控性强,传输速率快,数据完整,是一套成功、实用的采集系统。

图6 加速度测试结果分析

图7 数据传输速率测试

5 结论

FPGA技术与USB3.0的结合有极大的灵活性和可扩展性,基于FPGA和USB3.0的突出优点,该设计方案必将应用在更广阔的领域。虽然已经设计出了一个高速数据采集系统,但本系统还处在研发阶段,在PCB布局布线及信号和电源完整性方面仍待提高。

参考文献:

[1]张文栋.存储测试系统的设计理论及其应用[M].北京:高等教育出版社,2002:34-40.

[2]祖静,张志杰,裴东兴,等.新概念动态测试[J].测试技术学报,2004,18(z6):1-4.

[3]靳书云,靳鸿,张艳兵.弹载加速度数据记录仪抗高冲击设计[J].传感技术学报,2014,27(4):463-466.

[4]裴东兴,王文武,崔春生.利用转速测试弹丸炮口速度的方法研究[J].兵工学报,2013,34(1):125-128.

[5]Cypress Semiconductor Corporation,EZ-USB FX3 Super Speed USB Controller[EB/OL].www.cypress.com,2011,1-35.

[6]钱峰.EZ-USB FX2单片机原理、编程及应用[M].北京:北京航空航天大学出版社,2006:171-176.

[7]Cypress Semiconductor.Cypress CyAPI Programmer’s Reference [EB].2011:12-61.

[8]刘妍秀.USB3.0体系结构及发展前景[J].长春大学学报,2010,20(10):23-26.

[9]张聪,张涛.基于USB3.0设备控制器的固件设计[J].电子器件,2013,36(3):384-388.

[10]USB 3.0 Promoter Group,Universal Serial Bus 3.0 Specification [S].www.usb.org,2008.

[11]段仲麟,何其胃.基于USB的DSP与PC的通信接口设计[J].信息与电脑,2010,30(11):49-51.

[12]费业泰.误差理论与数据处理[M].5版.北京:机械工业出版社,2006:24-34.

The Design of Multi-Interface CAN Bus Detecting System*

LI Ping*,WEI Changbao

(School of Information Engineering,Huanghuai University,Zhumadian He’nan 463000,China)

Abstract:In order to make the data communication between the computer and 1553B bus much easier and faster,and improve the detection efficiency of 1553B bus equipment,a CAN bus detecting system was designed based on ARM and FPGA.With modular method for the hardware circuit,the ARM module,the FPGA module and the bus interface connecting were designed independently.The Top-Down method was used in the logic design based on FPGA.USB and Ethernet interfaces were designed based on ARM microcontroller for resolving the interface integration.Two interfaces could work independently.The results of software stimulation and hardware testing indicated that the detecting system could achieve data transmitting and detecting for CAN bus.

Key words:CAN bus; detecting system; multi-interface; modular method

doi:EEACC:720010.3969/j.issn.1005-9490.2015.04.040

收稿日期:2014-10-16修改日期:2014-11-08

中图分类号:TP334.7

文献标识码:A

文章编号:1005-9490(2015)04-0912-05