基于FPGA的Serial RapidIO协议 的设计与实现

2015-02-22许树军牛戴楠

许树军,黄 镠,牛戴楠,王 锐

(中国船舶重工集团公司第七二四研究所,南京 211153)

基于FPGA的Serial RapidIO协议 的设计与实现

许树军,黄镠,牛戴楠,王锐

(中国船舶重工集团公司第七二四研究所,南京 211153)

摘要:在对RapidIO协议和Serial RapidIO(SRIO,下同) IPcore用户接口介绍的基础上,详细描述了Serial RapidIO交换架构在FPGA上的编程方法,并采用双缓存机制实现了位宽、数据流速的转换,完成了多SRIO节点间的高速数据通信,具有较强的通用性和可移植性。

关键词:FPGA;SRIO IPcore;RapidIO;高速通信;串行接口

0引言

RapidIO高速总线技术主要为了实现系统内部设备互连,总线支持芯片到芯片和板到板通信。其规范采用三层分级体系结构:逻辑层、传输层和物理层。在物理连接上,它支持两种方式:并行模式和串行模式。与并行模式相比,串行模式具有更少的连接管脚、更大的带宽、更高的扩展性能、更低的成本等优点。

本文采用Xilinx公司Virtex6系列的FPGA实现高速串行RapidIO(SRIO)接口,即利用FPGA内RocketIO模块实现3.125Gbps ×4的SRIO高速接口。

1用户接口介绍

1.1 RapidIO协议概述

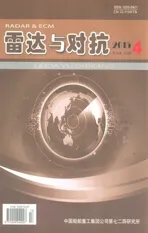

RapidIO数据交换流程是基于请求和响应事务的。包是系统中各设备端点间的基本通信单元,发起端点产生一个请求事务,该事务被发送至目标端点。目标端点产生一个响应事务直至发起端点来完成该次操作。图1显示了FPGA中SRIO端点支持的几种典型包格式。

图1中,ackID为物理层的包号;crf为扩展优先级位;prio为包的优先级;tt为器件寻址模式,=00为8位地址模式,=01为16位地址模式;Ftype为包格式类型字段;Ttype为事务类型字段;srcTID为源事务ID号;目的地址和源地址的长度由tt字段决定。所有包以16位循环冗余校验码(CRC)结束。

图1 FPGA中SRIO支持的典型包格式

1.2 SRIO IPcore的用户接口

SRIO IPcore已经实现了SRIO协议中的物理层、传输层和逻辑层的功能,用户只需对用户接口部分进行编程就可以实现FPGA与外部其他设备端点(以下以CPU处理器为例介绍,其他端点类似)的高速数据交换。

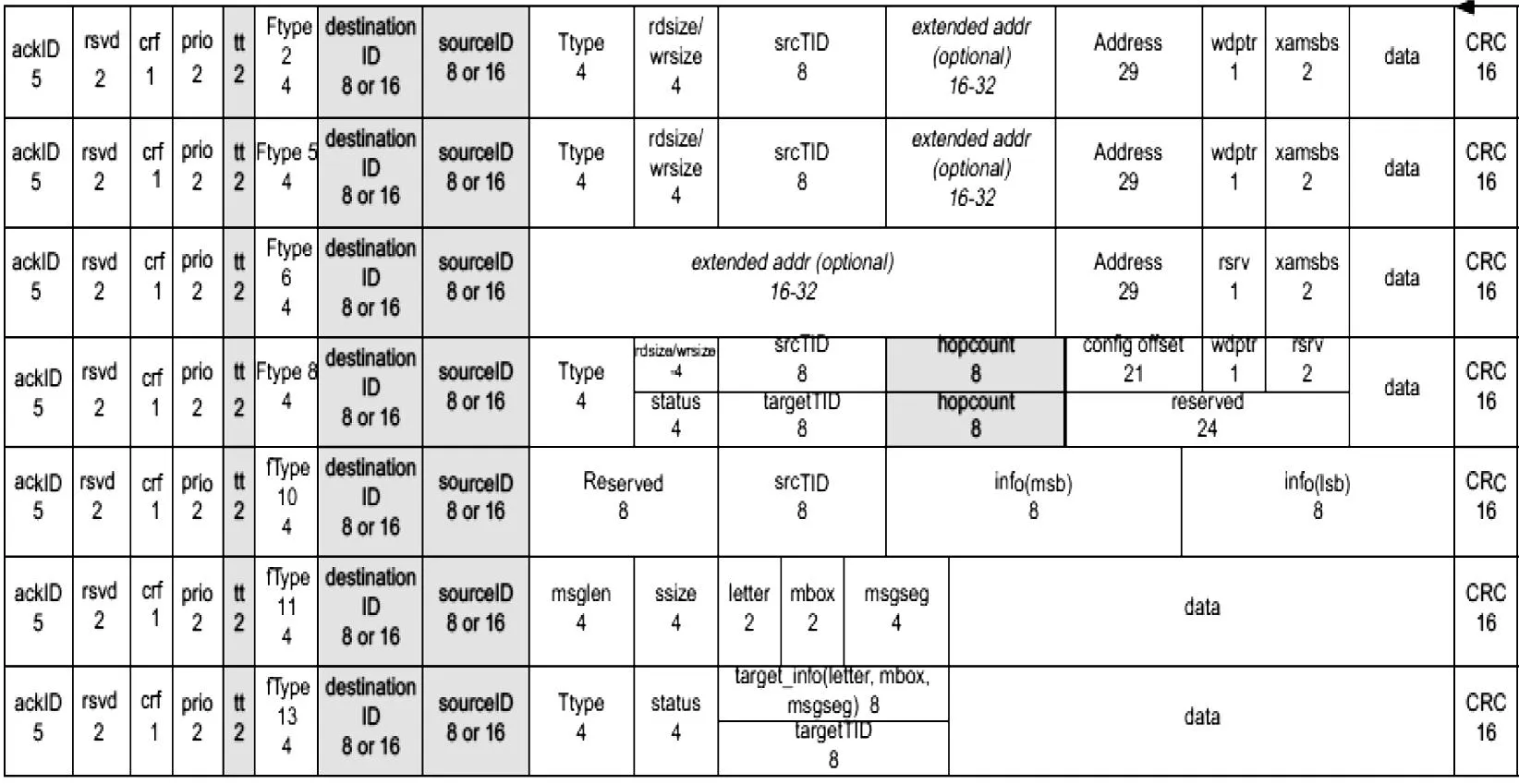

用户接口分为源端事务接口和目的端事务接口。源端事务包括源端点发起的请求事务和目的端对该请求事务应答回来的响应事务,目的端事务是目的端点发过来的请求事务及源端点对该请求事务进行应答的响应事务。图2显示了典型的有响应事务操作过程。无响应事务只有请求事务,没有响应事务。

图2 典型的有响应事务操作过程

SRIO IPcore的用户接口如图3所示,包括源端事务请求用户接口、源端事务响应用户接口、目的端事务请求用户接口和目的端事务响应用户接口。

图3 逻辑层用户接口框图

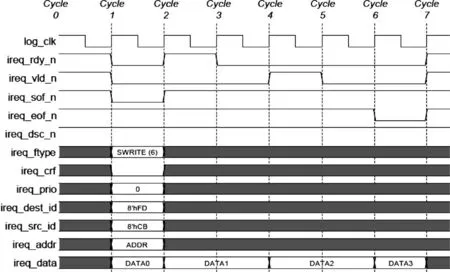

考虑在FPGA中实现SRIO协议的主要目的是为了高速的数据交换,即FPGA发送或接收高速数据流。为了编程逻辑实现的简单可靠,本文在设计中主要实现了两类事务接口:流写(Ftype=6)和门铃(Ftype=10),均采用8位器件地址和34位寻址模式。下面对源端事务请求接口的信号作简要说明,其他接口信号与此类似。

ireq_sof_n表示一包的开始,低电平有效;ireq_eof_n表示一包的结束,低电平有效;ireq_vld_n数据有效标志,只有在ireq_vld_n为低电平时其他接口信号才有效;ireq_rdy_n为逻辑层准备就绪信号指示,其他信号必须在ireq_rdy_n有效的情况下才被逻辑层接受;ireq_prio[0:1]包的优先级,取值范围0~3,在数据包中一般取值0~2,最低优先级为0,最高优先级为3;ireq_ftype[0:3]表示包格式类型,ireq_ttype[0:3]表示事务类型,如表示流写(SWRITE)的Ftype=6,流写只有一种事务类型,所以Ttype的值可以忽略,表示写(WRITE)的Ftype=5,Ttype有如下几种情况(Ttype=4 NWRITE,Ttype=5 NWRITE_R等);ireq_dest_id[0:7]表示目的端的端点号,采用8位器件地址模式(tt=0),所以最多可以寻址256个端点(0xFF端点号一般不采用);ireq_tid[0:7]表示事务ID,在端点之间交换数据包时指示这是第几个事务,一般采用自动累加计数器,每传输一包使该字段加一;ireq_data[0:63] 8字节的传输数据;ireq_addr[0:33] 34位字节寻址的地址偏移量。

一次流写请求事务的时序图如图4所示:在ireq_rdy_n和ireq_vld_n有效的情况下, ireq_sof_n为低电平指示一包数据的开始,在ireq_sof_n有效时钟周期内采集其他接口信号的值;包开始后,在每个有效时钟周期(ireq_rdy_n和ireq_vld_n都有效)采集ireq_data上的数据,直到ireq_eof_n有效,采集最后一个数据值,从而一包完整的数据即可传送到逻辑层内部。

微小钙化是超声诊断甲状腺癌的重要指标之一,其特异性较强,尤其是对乳头状癌的特异性较高。因当微小钙化这一指征出现时,考虑甲状腺癌的几率较高。

图4 SWRITE 源端请求时序图

2设计实现

接口逻辑主要完成FPGA内部逻辑与SRIO IPcore之间正确的数据交换,包括两个方面的功能:把FPGA内部数据流按照SRIO核的接口时序要求形成发送数据包;正确解析SRIO核接收到的其他端点发送来的数据包,并形成相应的响应事务包。

2.1 设计思路

设计中采用源端事务和目的端事务分离的模式。为了在FPGA中的逻辑实现方便,所有的数据传输都是采用8字节对齐的方式(每次传输的数据字节数为8的整数倍)。

在数据接收过程中,如果收到的是写事务,则根据接收到的偏移地址值把接收到的有效数据写入相应地址的RAM;如果收到的是门铃,则判断门铃号。

数据发送的过程是先传输数据,在一次数据传输完毕后发送门铃信号通知目的端点读取数据,这样就完成了一次数据的传输,接着启动下一次的数据传输。在RapidIO协议中规定,每个事务包的有效数据载荷在1~256字节之间(无有效数据载荷的包除外)。为了最大化传输效率,在设计中采用除最后一个数据包外其他包的有效数据载荷都为256个字节。

2.2 具体实现

数据接收的实现过程相对简单,只要根据接收到的地址把数据正确写入接收数据的双口RAM中,接收完毕给出标志信号即可完成一包数据的正确接收。

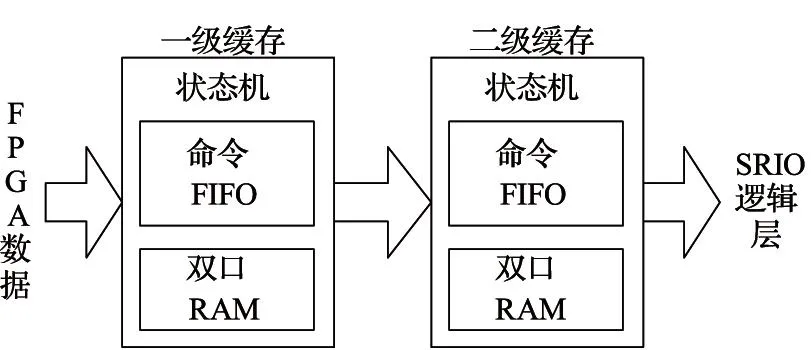

数据发送过程相对复杂一些,需要把传输的数据分成不大于256字节的包,并根据每包传输的字节数控制每包的偏移地址量,保证数据传输正确。由于RapidIO核每接收一个完整的包都要进行包数据的重组,且RapidIO核的缓存区大小也有限制,所以传输过程中需要握手信号控制双方的通信时序。如图5所示,设计中采用两级缓存结构。SRIO核的逻辑层时钟是156.25MHz、数据位宽是64bit,FPGA的数据位宽和时钟频率很可能和SRIO核不匹配。为了解决时钟域、数据位宽变换等问题,设计中加入了第一级缓存。由于每个RapidIO事务包的有效数据载荷不大于256个字节,加入第二级缓存完成数据分包功能,把FPGA的输入数据分成不大于256个字节的RapidIO流事务包。

图5 具体实现框图

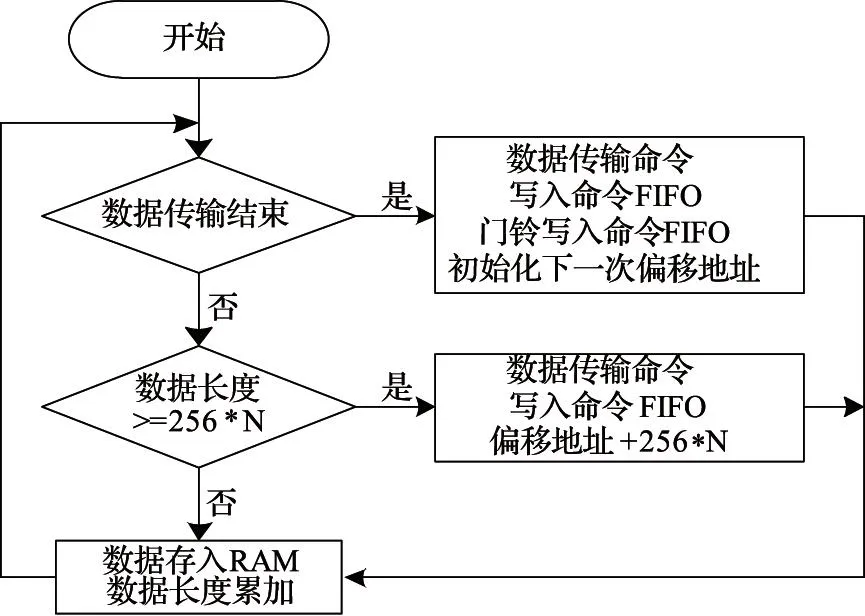

第一级缓存主要实现与FPGA传输数据的接口。为了防止数据丢失,第一级双口RAM的容量根据实际需要可以设置足够大的空间。命令FIFO每传输256*N个字节数据或数据传输结束写一次。命令FIFO存储的内容包括目的端点号、包格式类型、事务类型、偏移地址量、双口RAM中数据的起始地址和数据长度。在每次数据传输结尾,要把这次传输的字节总长度和一些附加信息传输出去,最后传输门铃给对方,通知对方接收数据。流程如图6所示。

图6 第一级缓存写状态机

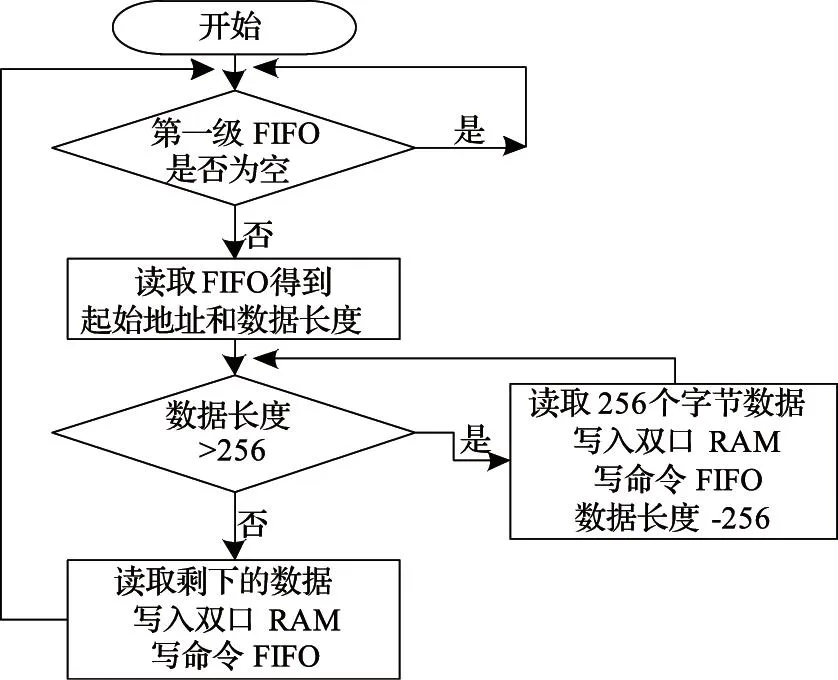

第二级缓存是把第一级缓存的数据包按照RapidIO协议分包,并最终实现与RapidIO逻辑层的接口时序。流程如图7所示。首先判断第一级FIFO是否为空,如果不为空,读取FIFO中的信息,根据读出的包格式类型、数据在第一级RAM中的起始地址和数据长度,产生RapidIO传输包。如果数据长度大于256个字节,则读取256个字节,产生数据长度为256个字节的SWRITE事务包,直到数据长度不大于256个字节产生最后一个写事务包。

图7 第二级缓存写状态机

由于RapidIO协议是基于交换结构的,在数据正常通信前必须要配置整个系统的交换路由关系,在系

统配置期间是不能正常通信的,所以在最终的设计中用户接口要加入通信使能开关,在系统配置完毕之前不能开始数据传输。

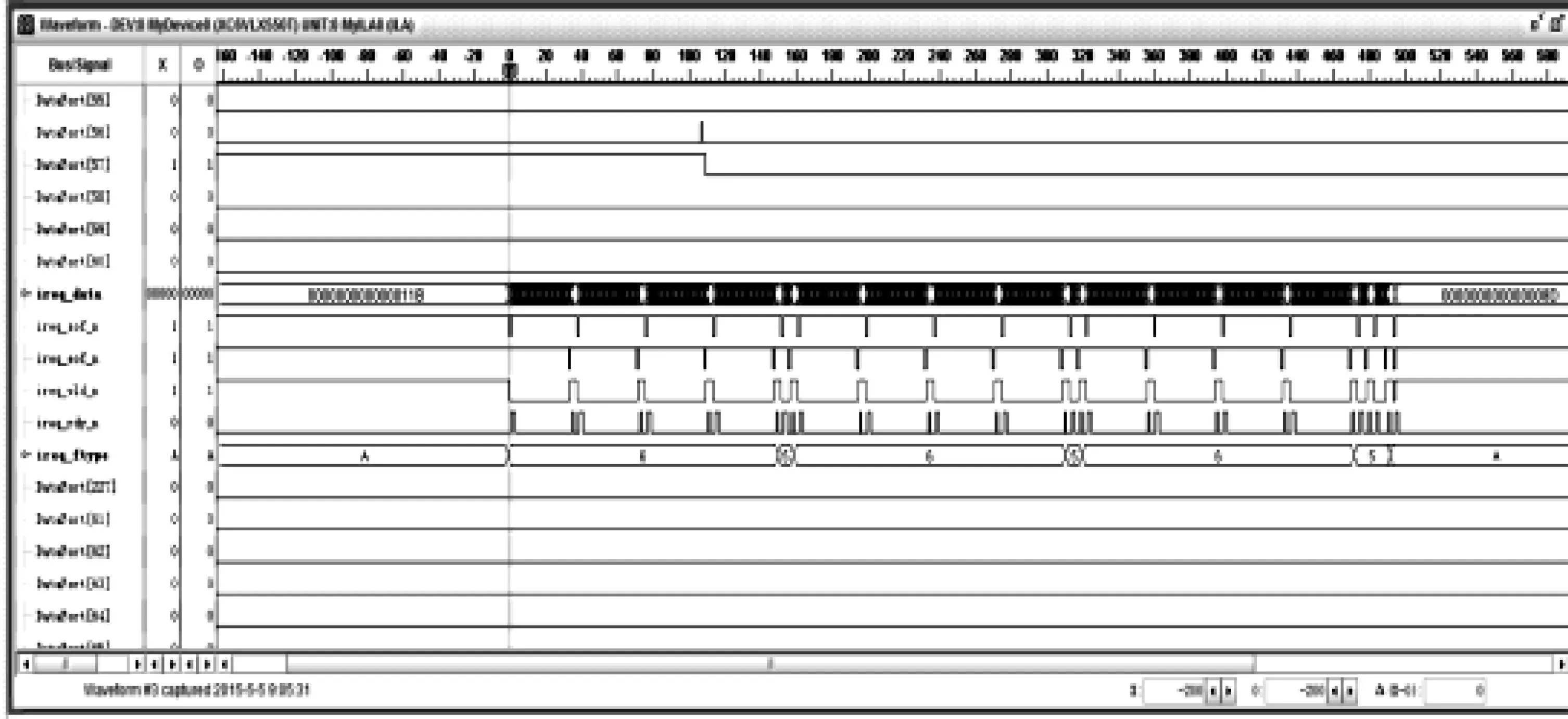

最终的设计采用VHDL语言在Xilinx公司的XC6VLX550T上实现。为了实现一对多的数据交换功能,设计实现中增加了第一级缓存双口RAM容量,同时加入更多的命令FIFO深度来实现多点通信能力。按照RapidIO协议成功发送数据如图8所示,在ireq_rdy_n和ireq_vld_n都为低电平的情况下 ireq_sof_n为低电平指示一包数据的开始,在ireq_sof_n有效时钟周期内采集其他接口信号的值,包括优先级、数据长度、事务类型、节点号、起始地址等;包开始后,在每个有效时钟周期(ireq_rdy_n和ireq_vld_n都为低电平)采集ireq_data上的数据,直到ireq_eof_n有效,采集最后一个数据值,从而一包完整的数据即可传送到逻辑层内部。

图8 发送数据成功时序图

3结束语

RapidIO是面向系统互连和交换结构的标准,具有握手协议简单、低缓冲开销等特点。FPGA的高速逻辑阵列、高级I/O能力和可重编程性,应用FPGA来实现RapidIO协议变得简便可行。RapidIO技术使FPGA的接口适应能力大大提高,使交换结构的使用设备设计和升级更加灵活。

RapidIO用户接口实现中,由于需要适应不同接口位宽和不同传输速率的数据流,并且RapidIO的逻辑层接口也有严格的时序要求,为了接口逻辑的适用性更强,设计中采用了两级缓冲机制,第一级缓冲实现FPGA数据流的存储和位宽变化,第二级缓冲用来实现与RapidIO逻辑层的接口时序。在时序关系调整正确后,第二级缓冲的逻辑就可以固定下来,因此只需修改第一级缓冲的逻辑来适应不同速率和位宽的数据流传输。RapidIO程序具有较强的通用性和可移植性。

参考文献:

[1]Sam FullerRapidIO嵌入式系统互连[M].北京:电子工业出版社,2006.6.

[2]LogicCORE IP Serial RapidIO v5.5 user guide,Xilinx Inc,2010.4.

Design and implementation of FPGA-based Serial RapidIO protocol

XU Shu-jun, HUANG Liu, NIU Dai-nan, WANG Rui

(No.724 Research Institute of CSIC, Nanjing 211153)

Abstract:The RapidIO protocol and the Serial RapidIO (SRIO) IPcore user interface (UI) are introduced, on the basis of which the programming method of the SRIO IPcore exchange architecture on the FPGA is described in detail. The two-stage buffer mechanism is adopted to realize the conversion of the bit width and the data rate and complete the high-speed data communication between multiple SRIO nodes. The RapidIO program features strong generality and portability.

Keywords:FPGA; SRIO IPcore; RapidIO; high-speed communication; serial port

中图分类号:TN911.7

文献标志码:A

文章编号:1009-0401(2015)04-0036-04

作者简介:许树军(1985-),男,工程师,硕士,研究方向:雷达信号处理;黄镠(1986-),男,工程师,硕士,研究方向:雷达信号处理;牛戴楠(1982-),男,工程师,硕士,研究方向:高速电路板设计和数字信号处理;王锐(1982-),男,工程师,硕士,研究方向:雷达信号处理。

收稿日期:2015-04-04;修回日期:2015-05-09