用于环路校准的延迟锁相环设计

2015-02-05陈勖房丽娜肖本

陈勖,房丽娜,肖本

(1.深圳信息职业技术学院软件学院,广东 深圳 518172;2.广东机电职业技术学院电气学院,广东 广州 510051)

用于环路校准的延迟锁相环设计

陈勖1,房丽娜1,肖本2

(1.深圳信息职业技术学院软件学院,广东 深圳 518172;2.广东机电职业技术学院电气学院,广东 广州 510051)

延迟锁相环能够产生精确的延时而被广泛使用。本文介绍了一种适用于直接调制发射机锁相电路环路校准的延迟锁相环。电路采用TSMC 0.18μm CMOS工艺实现,参考频率为26 MHz。在3.3 V电源电压下的仿真结果显示:延迟锁相环锁定时间为520ns,锁定相位为2π,同时输出8路相位差为45o间隔的时钟。

锁相环,延迟锁相环,鉴相器,压控延迟线

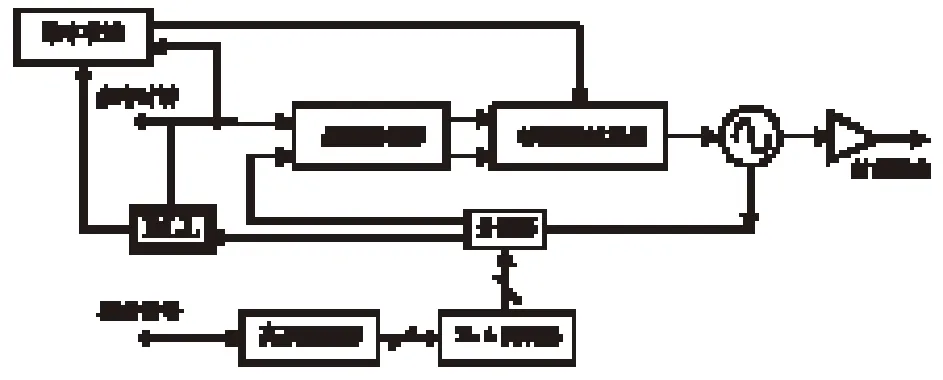

近些年移动通信产业迅猛发展,移动终端呈现爆炸式的增长。但是对于便携式移动设备而言,低噪声和低功耗仍然是移动产品射频前端最重要也是设计者最需要考虑的两个系统指标。传统的发射机结构不但功耗较大,而且体积较大,不利于集成;直接上变频结构以其低成本和高集成度性能大量使用在GSM等通讯制式中,仍然需要面临频率牵引、本振泄露、直流失调等诸多问题,随着集成电路的高速发展,新的发射机结构—直接调制锁相环发射机以较低的功耗和较低的噪声的性能得到人们的广泛使用。直接调制锁相环发射机的基本结构如图1所示[1]。这种结构去掉了传统发射机必须存在的上混频器,通过调整锁相环的分频比达到间接改变输出频率的目的。这种结构最大的特点是调制过程中不会出现频率漂移的问题,但也存在由于工艺的容差所导致的环路带宽波动或环路增益的不稳定等问题。

图1 直接调制发射机结构Fig.1 Direct modulation transmitter

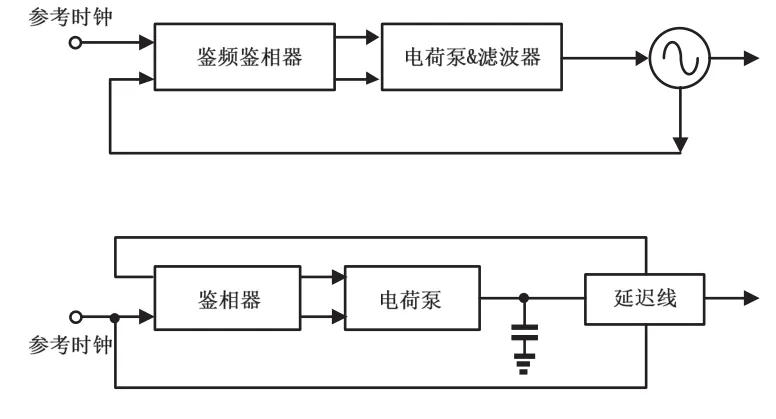

在无线通信系统中,当环路带宽较窄时,由于发射的频谱有效部分在某种程度上会被压缩,导致调制信号的相位误差进一步恶化,如果环路带宽较宽时,由于相位噪声和量化噪声的增加会使得噪声性能变差[2]。另外,在GSM通信系统中,环路带宽限定为200kHz,为了克服窄的环路带路影响,常用的做法是让基带的调制信息通过一个预失真滤波器进行滤波[3],预失真滤波器的设计必须和环路传递函数形成互补关系,否则任何的波动或差异都会造成发射信号质量的下降。因此对环路带宽的校准就变得非常重要。整个校准框图如图2所示[4]。

图2 校准框图Fig.2 Calibration structure

1 工作原理

延迟锁相环DLL是在锁相环PLL的基础之上发展起来,继承了锁相环PLL的功能特点,两者在结构上非常相似,只是将环路中的压控振荡器去掉,取而代之的是一段能够改变延迟时间的压控延迟线(VCDL),其结构框图如图3所示,它是一个相位负反馈系统。压控延迟线的核心结构是由一组由电压控制的反相器链,与锁相环的压控振荡器相比,不但结构简单,功耗也大幅度降低。

延迟锁相环工作时,参考时钟驱动压控延迟线,压控延迟线的输出时钟反馈到鉴相器和参考时钟进行比较,通过锁相环路使两者之相位差锁定在一个参考周期(同相比较)或者半个周期(反相比较),则每个延迟单元的延迟时间就为Tref/n或者Tref/2n,其中Tref是参考信号周期,n为延迟的级数[5]。

另外,对于VCDL而言,输出相位和控制电压成正比,传输函数是一个常数Kvcdl。对于一阶环路滤波器,DLL系统传输函数为一阶方程,相对于PLL二阶系统来说,增益、带宽、稳定性及相位噪声方面的考虑将更加容易。另外,延迟锁相环的输入噪声会通过延迟线消失,从而相位抖动得到很大的改善。因此DLL常用来生成稳定的延迟或者多相位的时钟信号。

图3 a)锁相环结构 b)延迟锁相环结构Fig.3 a)PLL structure b)DLL structure

2 电路设计

延迟锁相环的电路设计主要集中在鉴相器、电荷泵和延迟单元上。而延迟锁相环的环路滤波器仅需要一个电容即可。设计中需要考虑几个要点:1)要充分考虑工艺的影响,否则会因为VCDL的开环延迟时间变化而导致不能锁定;2)由于需要输出8路等相位间隔时钟,则延迟链路会较长,这样后级驱动能力不足也会导致不能锁定;3)需要考虑工艺的变化所带来的锁定频率范围过窄的问题。

2.1 鉴相器

鉴相器的作用主要是鉴别输入信号的相位误差来调节电荷泵的输出电流,从而控制压控延迟线的延迟时间达到锁定的目的。通常电荷泵型锁相环中所采用的鉴频鉴相器电路主要有三种:基于触发器的PFD、传统形式的PFD以及预充电PFD。本次设计采用基于触发器的结构进行设计。

图3是整个鉴相器的门级电路实现。其基本结构是由两个具有复位功能的、边沿触发的D触发器和一个与门共同组成,D触发器的D输入端口接高电平Vdd,这样在DN、UP都处于高电平时,与门的电平翻转输出会使得两个触发器复位[6]。与非门和反相器间可以添加缓冲单元以调节DN的脉冲宽度,用来消除电荷泵锁相环中的鉴相死区,并有足够的脉冲宽度打开后级电荷泵的开关管。

2.2 电荷泵

美国疾病预防控制中心CDC,曾经从美国城市亚特兰大的161个公共和私人游泳池做了调查,发现每个进泳池的人都附着至少0.14克大便物质。

电荷泵,顾名思义就是一个电荷开关。它的作用就是让超前或滞后的相位差转化为电流,然后通过一阶电容的积分作用再变成后级延迟单元的控制电压,从而达到锁定。

图4 鉴相器门级电路图Fig.4 The gate circuit diagram of PD

在进行电荷泵设计时,电流的不匹配是值得关注的,因为这样会导致控制电压的不稳定。本次设计的电荷泵电路如图5所示。

图5 电荷泵电路Fig.5 Charge pump circuit

由图可见,最左边的支路1构成了参考电流源,中间的支路2是电流源的输出支路,右边的支路3则构成了镜像电流源。由于所有支路都采用的是共源共栅结构,这就避免了输出阻抗不匹配导致的电流不匹配问题。同时在UP和DN输入端加入传输门来抑制偏移。

电荷泵的输出端CP需要接环路滤波器,由于整个延迟锁相环是一个一阶系统,因此,设计时无需考虑复杂的滤波器结构,只需要采用一个电容就可以了。电容的容值选取需要考虑环路带宽、速度因素的影响,这里给出经验公式进行计算:

这里ωn是环路带宽。最终通过计算优化选取合适的电容值为0.96pF。

电荷泵最右边的部分则将输出的控制电压转变为控制电流输出,可以达到比较高的控制精度。

2.3 压控延迟线

压控延迟线是由若干压控延迟单元串联而成,级数越多波形失真度越小。从设计角度考虑,延迟线的设计主要是对工艺的设计。因为制造工艺的影响会造成累积效应,造成输出信号的占空比不等,最后终会使得后级输出信号被完全拉平。本次设计需要输出8路等相位间隔时钟,考虑累积效应的影响,选择16级延迟单元,并且每个延迟单元前端串联一个反向器来消除累积效应,取偶数级延迟单元的输出为最终的时钟输出,相位间隔为45度。

在MOS工艺中,传统的压控延迟单元主要有两种结构[7]:1)电容性调节;2)电阻性调节。前者通过改变等效电容值来达到延迟,但线性度较差,调节范围小;而后者通过调节充放电电流来改变延迟,线性度好,调节范围也比较大。这里选用电阻性调节结构做延迟单元的基本结构,但控制方式变为电流控制方式[8]。

设计的延迟单元如图6所示。这样结合前置的电荷泵后级的电流源电路,对延迟控制更为准确。

图6 延迟单元Fig.6 Delay cell

3 仿真分析

整个延迟锁相环电路设计采用TSMC 0.18μm 1P5M的CMOS工艺实现。由于压控延迟线中延迟单元较多,而延迟线上的节点电容又是其延迟时间的影响因素,因此设计版图时需要特别考虑节点的寄生电容,尽量让各延迟线信号连线最短,同时考虑版图的对称性。整个版图约为130*60μm2,如图7所示:

图7 延迟锁相环版图Fig.7 The layout of delay locked loop

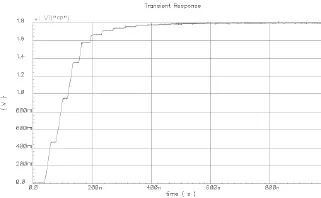

GSM系统的参考频率为26MHz,这也是延迟锁相电路的输入参考时钟频率。利用Cadence公司的SpectreRF仿真工具对整个延迟锁相环电路进行瞬态仿真。首先观察鉴相器的输出端口UP和DN输出情况,如图8所示。可以看到,对于电荷泵而言,刚开始是一个充电过程,当系统稳定后不再充电,UP和DN基本一致,在上升和下降沿瞬间临界状态,充放电保持相等。

图8 鉴相器的输出波形Fig.8 The output waveform of phase detector

图9 电荷泵的输出波形Fig.9 The output waveform of charge pump

接下来查看电荷泵的CP端口输出情况。由于仿真电路平台已经连接了对地电容,因此测量电容上的电压值VCP,如图9所示。从VCP的建立稳定可以判断DLL是否锁定以及具体的锁定时间。从波形图上来看,延迟锁相环的锁定时间在520ns左右,VCP稳定后的电源约在1.8伏。

图10给出了反馈时钟与参考时钟的对齐过程,可以看到,520ns以后两者上升沿对齐效果较好,最大间隔小于0.5个ns,开环延迟时间为1.5T,锁定相位在2π。

图11给出了8路等相位间隔的时钟,电路锁定后,8路时钟相位间隔基本相等,时间间隔约4.8ns。

4 结论

由于无线通信系统锁相环环路带宽的不稳定性,对环路校准非常重要。本文为GSM系统锁相环路校准设计了一款结构简单、能快速锁定的延迟锁相环电路。仿真结果表明,该延迟锁相电路锁定时间为520ns,锁定相位在2π,并且输出了8路等相位间隔的时钟供数模转换器使用。

图10 反馈时钟和参考时钟的对齐过程Fig.10 The alignment process of feedback and reference clock

图11 8路等相位间隔时钟Fig.11 Eight clocks with same phase interval

References)

[1]赵冯.应用于短距离无线通信的发射机研究与设计[D].上海:复旦大学,2009 ZHAO Feng.Research and design of transmitter applied to short distance wireless communication [D].Shanghai:Fudan University,2009 (in Chinese).

[2]Akamine Y.,Kawabe M.,Hori K.,and at el.A loopbandwidth calibration system for fractional-N synthesizer and ΔΣ-PLL transmitter[C].2005 Solid-State Circuits Conference,2005,1:314-315.

[3]Perrott M.H.Techniques for High Data Rate Modulation and Low Power Operation of Fractional-N Frequency Synthesizers [D].Massachusetts Institute of Technology,1997.

[4]Sappok S,Joeres S,Heinen S.Step response detection technique for self-calibrating predistortion GFSK ΣΔ modulation loops [C].2005 fifth international conference on information,communications and signal processing,2005,1:1388-1392.

[5]陆平,郑增钰,任俊彦.延迟锁定环(DLL)及其应用[J].固体电子学研究与进展,2005,25(1):81-88 LU Ping,ZHENG Zengyu,REN Junyan.Delay-locked loop and it's application [J].Research&Progress of SSE,2005,25(1):81-88(in Chinese).

[6]罗文.基于1.8V CMOS工艺的12bit 100MSPS ADC的时钟发生器设计[D].成都:电子科技大学,2009 LUO Wen.Design of clock generator of 12bit 100MSPS ADC based on 1.8V CMOS [D].Chengdu:University of Electronic Science and Technology,2009(in Chinese).

[7]李军.应用于手机DDR控制芯片的延迟锁相环设计[D].上海:上海交通大学,2010 LI Jun.An analog DLL for mobile DDR controller applications[D].Shanghai:Shanghai Jiao Tong University,2010(in Chinese).

[8]陈星.用于时钟产生电路的延迟锁相环的研究与设计[D].成都:西南交通大学,2012 CHEN Xing.Design and research of a delay locked loop for clock generator [D].Chengdu:Southwest Jiaotong University,2012(in Chinese).

Design of delay-locked loop for loop calibration

CHEN Xu1,FANG Lina1,XIAO Ben2

(1.Software Institute,Shenzhen Institute of Information Technology,Shenzhen 518172,P.R.China 2.School of Electrical Engineering,Guangdong Vocational and Technical College,Guangzhou 510051,P.R.China)

Delay locked loop is widely used because it may generate an accurate delay.This paper introduces a delay locked loop applied to loop calibration for PLL circuit of direct modulation transmitter.The whole circuit used TSMC 0.18 μm CMOS technology with a reference frequency of 26 MHz.The power supply is 3.3V.The simulation results show that the circuit has a locking time of about 520ns and a locking phase of 2π.It also can output eight clocks with the same phase interval of 45o.

phase locked loop;delay locked loop;phase detector;voltage-controlled delay line

TN911.8

A

1672-6332(2015)01-0074-05

【责任编辑:杨立衡】

2015-03-10

深圳市科技计划项目(JCYJ20140418100633642)

陈勖(1977-),男(汉),湖南邵阳人,工程师,博士,主要研究方向:射频集成电路设计。E-mail:chen_xu@sziit.com.cn