基于PC104+总线的24位AD数据采集卡设计

2015-02-05中国船舶重工集团公司第七一八研究所

中国船舶重工集团公司第七一八研究所 胡 备

基于PC104+总线的24位AD数据采集卡设计

中国船舶重工集团公司第七一八研究所 胡 备

本文设计了一种基于PC104+总线的24bit分辨率数据采集卡,该采集卡具有高精度、高速度的优点。采用PLX9054控制芯片控制PCI时序,给出了具体的逻辑设计,通过实际测试,验证了其实用性。

PC104+;PCI9054;24位AD

1 引言

随着数字信号处理技术的快速发展,AD数据采集过程中的采样和处理速度也越来越高。在某些数字信号处理场合,采样信号的频带要尽可能的宽,动态范围要尽可能大,以便获取更多的信号细节特性。因此,数字信号处理系统对前端的A/D采样电路要求更高,高精度、高分辨率,转换速度也尽可能的快,以满足整个系统实时性和精确度的要求。PCI总线作为一种高速同步总线,实现了设备间的快速访问,并且有高达132MB/S 的数据传输率,而PC104+更以其紧凑的结构和方便的扩展性更有广泛应用。本文采用了PC104+总线,结合PCI9054和FPGA作为控制中枢,设计了一种24位的AD数据采集卡。

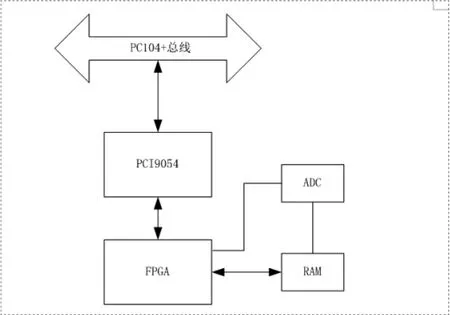

2 采集卡总体结构

本设计中,采用一片PCI9054作为PCI总线控制器,一片采集控制芯片(FPGA)作为采集控制及时序控制,以及PCM4220芯片为核心的AD转换模块。总体结构框图如图1所示。该数据采集卡性能可以达到400k的采样速率,分辨率在20左右,由于PCI总线不需CPU的介入便可进行数据传输,因此能在设备之间实现数据交换和快速访问。

图1 系统总体结构图

欲采集信号经隔离放大后进入A/D模块,在FPGA的控制下,由24bitADC芯片PCM4220将外部信号作模数转换后,存入RAM之中。每一组数据采集完成后,由FPGA通过PCI9054向主机申请中断,中断响应通过PCI9054直接读取RAM中的数据,再进行下一步的数据处理。

3 采集卡的设计方案

3.1 PCl总线控制器

PCI总线是一种高速同步总线,它可以实现突发传递、即插即用功能。由于PCI总线协议有一定的复杂性,其硬件电路实现起来较为困难,所以一般情况下通过两种途径实现:一种是选用专用协议处理接口芯片,或者是采用FPGA的IP核实现。两者各有优缺点:专用芯片由于内部集成了处理协议的大部分功能,所以开发过程中并不需要设计者参与太多PCI协议相关内容,所以开发周期短,但是降低了系统的集成性,增加了成本;IP核方式要求设计者对PCI协议有深入了解,然后自行设计协议接口的时序和逻辑,这种方式的设计难度相对较大,但是保证了系统的集成性。本设计中,我们采用第一种方式,采用PLX公司的PCI9054作为PCI总线控制器。

选用PCI9054的c模式工作方式。在C模式下, PCI9054将PCI接口的地址和数据总线区分开,是系统设计中的一种常见模式。C模式下,要求设计者对时序能严格把控,使本地和总线两部分的时序控制互不干扰,同时相辅相成,从而很好的应用9054芯片。在本设计中,将mode0和mode1引脚拉低,以确保mode[0:1]=00。

3.2 FPGA逻辑设计

本设计中采用的Altera公司的EP2C8Q208,其主要功能是负责PCI接口芯片的逻辑,在FPGA内部,集成了PCI局部总线、DMA控制器以及ADC芯片控制等功能,其内部逻辑结构框图如图2所示。其中,9054接口的主要任务是与PCI 总线完成握手过程,根据PCI9054芯片的时序要求产生时序对应的响应信号;当有数据写入完毕后,负责产生中断请求信号;时钟信号部分用来产生片内所需的时钟信号;控制部分根据总体时序逻辑来控制FPGA片内其它部分;DMA 控制器主要是地址控制器,按照相应的ADC频率产生一个递增的RAM地址,在写入RAM时发挥作用,另外可以作为片选信号等逻辑。

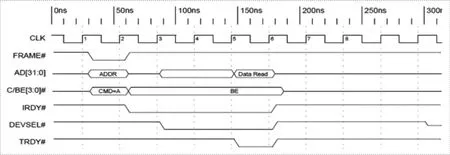

图3 PCl读时序

图4 PCl写时序

图2 FPGA内部逻辑框图

PC104+主板通过向I/O口的既定地址单元执行写入操作,从而触发AD开始采集命令,此时控制部分使ADC芯片PCM4220相应引脚有效来启动数据采集。当AD准备好数据并且数据有效时,由DMA控制器做出相应使得数据存入RAM。进而,PCI本地总线部分产生中断信号申请中断。与此同时,PCM4220仍继续按递增地址的方式将采集后的有效数据存入RAM。PC104+主板收到中断信号后,执行中断服务程序,读取数据采集卡上RAM中的数据。PCI9054的数据地址线分别与RAM的数据地址线直接相连,读写控制线与FPGA相连,中断有效后,PCI9054直接读RAM中的数据。

4 设计时序图

FPGA相关时序如图3、图4所示。

5 结论

经制板测试验证,本文设计的24bit分辨率数据采集卡,具有高精度、高速度的优点。采用PLX9054控制芯片控制PCI时序,给出了具体的逻辑设计,通过实际测试,验证了其实用性。采用了PC104+总线架构,实现了系统的易扩展性。

[1]PC/104 Embedded Consortium PC/104—Plus Specification Version 1.2,August 2001.

[2]贾英江,王维斌.ADC综述[J].电子测量技术,1999(4).

[3]邱兆坤,王伟,马云,等.一种新的高分辨率ADC有效位数测试方法[J].国防科技大学学报,2004,26(4).

[4]何正淼等.24位ADC在地震数据采集中的应用[J].数据采集与处理,2005,20(2).