基于PLD/FPGA的通用异步收发器设计

2015-01-22汪超宇

汪超宇

摘要:通用异步收发器是一种能同时支持短距离和长距离数据传输的串行通信接口,被广泛应用于微机和外设之间的数据交换,本文对FPGA的通用异步收发器设计进行分析。

关键词:通用异步收发器数据传输数据交换

串行通信方式传递数据所传输的距离比较远,所用的数据线也很少,并且其稳定性也高。因此在数据通信方面能够被广泛的使用。异步收发器(UART)是经常被使用来进行串口通信的设备。本文就是用VHDL语言编写的应用在FPGA上的一个UART。在传递数据时,我们仅仅需要使用UART的几个作用,所以如果专门购置专用的UART,则会造成资金和功能上的浪费。恰好VHDL可以用硬件语言搭建出UART的模型,可以根据所需要的功能来进行程序的编写,这样既省费用又省步骤。

1UART的工作原理

UART(UniversalAsynchronousReceiverTransmitter,通用异步收发器)是通常使用的异步串行传递数据的传输协议。在串行通信中,数据是一个字节帧一个字节帧来发送信息的。发送端和接收端在接收数据帧的时候必须有约定的格式和约定的波特率。一个数据帧由1位起始位(低电平)、5~8位数据位、1位校验位(可选可不选)和停止位来组成。一个数据帧的开始便是起始位,起始位处于逻辑0状态,处于逻辑0状态就表明发送端已经准备开始发送数据了。一个数据帧的结束是停止位,停止位处于逻辑1状态,处于逻辑1就表明接收端已经停止接收数据了。而波特率采用标准速率9600字节每秒。数据在传输时,低位在前,高位在后。接收端检测并确认起始位后,开始接收数据位。当接到停止位后,FPGA向CPU发出中断信号。发送数据时,CPU设置波特率为9600字节每秒,然后FPGA将数据一帧一帧的通过总线传递给CPU,当CPU接收到低电平时,表示此时数据传送结束。

2程序设计与仿真

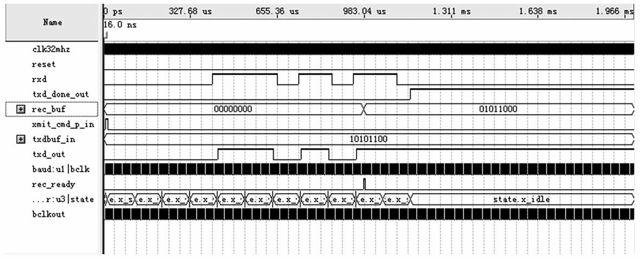

顶层程序与仿真:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_arith.all;

useieee.std_logic_unsigned.all;

entitytopis

port(clk32mhz,reset,rxd,xmit_cmd_p_in:instd_logic;

rec_ready,txd_out,txd_done_out:outstd_logic;

txdbuf_in:instd_logic_vector(7downto0);

rec_buf:outstd_logic_vector(7downto0);

bclkout:outstd_logic

);

endtop;

architectureBehavioraloftopis

componentreciever

port(bclkr,resetr,rxdr:instd_logic;

r_ready:outstd_logic;

rbuf:outstd_logic_vector(7downto0));

endcomponent;

componenttransfer

port(bclkt,resett,xmit_cmd_p:instd_logic;

txdbuf:instd_logic_vector(7downto0);

txd:outstd_logic;

txd_done:outstd_logic);

endcomponent;

componentbaud

port(clk,resetb:instd_logic;

bclk:outstd_logic);

endcomponent;

signalb:std_logic;

begin

u1:baudportmap(clk=>clk32mhz,resetb=>reset,bclk=>b);

u2:recieverportmap(bclkr=>b,resetr=>reset,rxdr=>rxd,r_ready=>rec_ready,rbuf=>rec_buf);

u3:transferportmap(bclkt=>b,resett=>reset,xmit_cmd_p=>xmit_cmd_p_in,txdbuf=>txdbuf_in,txd=>txd_out,txd_done=>txd_done_out);

bclkout<=b;

endBehavioral;

3总结

UlART经常用于数据之间的串行通信,它所需要使用的线路较少,并且稳定性高,数据可以传输很长的距离,因此芯片或计算机系统之间进行数据传送时经常用UART。使用VHDL语言,可以把UART有限状态机做的更加精密,更加适合于数据的通信,数据之间的传递的稳定性更高。

参考文献:

[1]朱勤.基于VHDL/FPGA的嵌入式UART的设计及FPGA验证[D].苏州大学,2011.

[2]刘李明.基于FPGA的通用实时信号处理系统的硬件设计与实现[D].北京工业大学,2009.

[3]刘志平.基于FPGA的高速数据采集存储系统设计[D].西安电子科技大学,2009.