低功耗小型化时频模块的设计

2015-01-21谢鹏

谢 鹏

(华中光电技术研究所 武汉光电国家实验室,湖北 武汉 430074)

0 引言

时间是当今测量精度最高的基本物理量。随着信息化时代的到来,高精度时间频率已经成为一个国家科技、经济、国防和社会生活中至关重要的参量,其应用范围涉及到国家诸多重要部门和各个领域,几乎无所不及。高精度时间是军事、电力、通信、交通等各行业系统运行的安全保障,时间频率的科学研究已成为国家信息化建设的重要科技支撑。

高精度时间基准是通信、导航、电力、工业、商务以及国防建设等领域重要的基础保障平台之一,精确的时间同步需求也越来越广泛,人们对时间和频率基准的精度提出了越来越高的要求。如何获得高精度时间同步是保障各系统正常可靠运行的关键。对于时间频率用户系统来说,在利用各种技术手段获得高精度、高可靠性时间频率的同时,时频用户终端的体积、功耗等也成为更加关注的目标。时频设备要想获得高可靠性,时间源的冗余备份是必要的手段之一,而时频设备高精度指标的实现又需要增大设备的体积和功耗。研制低功耗、小型化的时频模块,可以有效解决时间频率用户系统性能指标与体积、功耗之间的矛盾,便于实现时间源的冗余备份,更大程度提高时频设备的可靠性。

1 模块硬件设计

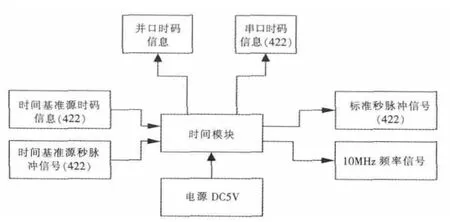

时频模块通过接收外部提供的供电电源及时间基准源,对内部时间进行校准后,以串口、并口等接口形式向外输出标准时间信息,同时输出高准确度的秒脉冲及频率信息。该模块在保持与我所现有时统设备相应级别的精度指标下,功耗与体积大大减小。

模块以ARM 系列的微处理器和物理层网络接口芯片等构建嵌入式硬件平台,在软件层面实现基于微处理器和基于FPGA 的分频控制程序设计,实现时间模块的对时、守时、串口通讯及并口显示功能。

低功耗小型化时频模块由频率源及外围电路、电平转换电路、隔离电路、FPGA 和ARM 微处理器构成的主控电路、电源电路等组成,如图1 所示。该模块将接收和解码的GPS 时码及秒信息译码为用户所需要的各类时间信号。

图1 模块组成

模块输入接口:①供电电源DC5V,1 路;②时间基准源时码信息 (422),1 路;③时间基准源秒脉冲信号(422),1 路。

模块输出接口: ①标准串口时码信息(422),1 路;信号内容:年、月、日、时、分、秒;数据更新率:4 次/秒;②标准秒脉冲信号(422),1 路;③并口时码信息,1 路;信号内容:年、月、日、时、分、秒;数据更新率:4 次/秒;④10MHz频率信号,1 路。

模块主要技术参数: ①同步精度: 优于200ns;②守时精度: 优于5ms/100day;③电源功耗: 不大于5W;④模块体积:不大于(100×150×20)mm。

模块频率源选型: 当前时频设备通用的频率源有温补晶振(TCXO)、恒温晶振(OCXO)、铷原子频标、铯原子钟等等。其中恒温晶振和原子频标频率准确度、老化率、温度特性等指标较好,但功耗较大;温补晶振功耗、体积都较小,但频率准确度不足。需要选择一种体积小、功耗低、性能指标高的频率基准作为时频模块的时间源。通过调研国内外多型晶振和原子频标,选定一种新型的芯片级原子钟CSAC (Chip Scale Atomic Clock)作为频率源。经调整后的频率输出准确度标称值可达±5×10-11,适合作为低功耗小型化时间模块的频率源。

CSAC 模块的选取参考了来自儒科电子对CSAC 相关性能测试报告。以下为截取的部分测试报告内容。测试采用了其公司自主研制的高性能GPS 同步时钟——TG100 系统作为测试参考源,分别对CSAC 的10MHz 输出和1PPS 相关指标进行了测试,并同其它铷钟进行了一个横向比较。测试内容包括CSAC 的10MHz 的频率准确度、短期稳定性、相位噪声,以及1PPS 信号的定时精度、锁定频率准确度、保持稳定性和24 小时保持等关键指标。此外,还对CSAC 的锁定时间和功耗进行了测试。这里截取了部分报告如下:①开机锁定时间见表1;②开机功耗见表2。测试的时候要求测试环境的温度在25℃左右;③外观及尺寸对比。如图2 所示为CSAC 原子钟外观图,图示中硬币为尺寸参考,CSAC 原子钟体积不足铷钟FE-5650A 的1/10,具体尺寸大小如表3 所示。

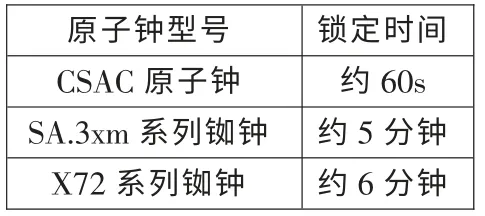

表1 开机锁定时间对比

表2 功耗对比

2 模块软件件设计

2.1 低功耗小型化时间模块工作原理

图2 CSAC 模块俯视图

时间模块采用FPGA(EP3C25E144C7) 和ARM(STM32F107) 微处理器构成主控电路。其中,FPGA主要用来完成时间的驯服、频率源的倍频、对基准频率源的误差计算、并口时码信号的输出、标准秒信号及标准频率信号的输出等功能,ARM 微处理器主要完成时间基准源时码的解算、串口时码信息的输出、CSAC 频率源的校准及附加功能的实现等。如图3 所示为时间模块的信号流程图。

表3 外形尺寸对比

图3 信号流程图

低功耗小型化时频模块利用FPGA 和ARM 微处理器构成的主控电路实现以下功能: ①监测频率源的工作状态。对频率源的锁定信号进行实时监测,确定其工作在正常状态;②根据外部输入的基准秒信号对频率源频率进行测频运。在进行频率源校准期间,每秒对输入秒信号和频率源分频出的同步输出秒信号之间的相位进行计算,并将计算所得差值实时发送给ARM 处理器;③根据测频运算处理的调频值完成对频率源的调频工作。ARM 对FPGA 输出的秒脉冲在10000 秒相位差进行计算,得出频率源的误差值(精度为10-15),将补偿值通过串口发送给CSAC 模块进行补偿;④测量本地秒与外部输入秒的相位差,对本地输出秒相位进行调整,使输出秒信号同步于外部输入秒信号;⑤接收外部GPS 时间报文,设置本地时间信号的运行时间,使本地输出时码信息同步于外部输入的时间报文。将同步后的时码报文通过串口及并口发送出去,串口通讯波特率为9600,并口与T6963C 液晶模块通讯,实现标准时间的显示;⑥预留手动配置时间数据、按键同步外部输入的时间报文等其它附加功能。

为确保时频模块的守时精度这一关键技术指标,需要对选定的频率源CSAC 做频率校准处理。用FPGA 作为直接的调频元件和主要的逻辑控制单元,结合ARM处理器的运算数据,实现频率调相处理,保证频率源的输出频率准确度处于最佳。采用的技术途径如下: ①将频率源输出的10MHz 频率信号,通过FPGA 内部的锁相环(PLL) 倍频至100MHz,作为频率校准的基准时钟使用;②外部输入参考秒脉冲和本地秒脉冲的频率源不同,存在着一定的频差,通过测量在一定时间t(10000S) 内两路秒信号相位差的变化,算出被测频率与标准参考频率的频差值;③ARM 处理器结合频率源的准确度曲线,对FPGA 计算得到的频差值数据进行滤波计算,舍去由于异常干扰而产生的大调频数据,防止由于异常情况而引起的频率大跳变。这里采样连续3 秒内输入输出秒脉冲相位的差值,比对3 差值的大小,取大小相同的2 次差值为10000S 后的相位差值。如三次差值均不相同则重新取值;④ARM 处理器通过串口发送调频命令,对频率源进行调频操作,实现输出满足指标要求的10MHz 频率信号。其中,通过测量相差来计算频差的过程如下: 测量相差的采样时钟用100MHz 系统时钟信号,以两路秒脉冲的上升沿 (这里记上升沿分别为h1、h2,h1为输入,h2为输出) 作为触发门限,测得一个频率计数值x,进行如下计算:

2.2 ARM 控制软件和FPGA 控制软件

ARM 控制软件采用C 语言编写,主要用于完成GPS 时间解码、串口时码通讯、T6963C 并口显示处理、频率校准计算及辅助控制等功能;FPGA 控制软件采用框图和Verilog 混合编写,主要用于完成分频处理、倍频处理、脉冲同步控制、相位差值采样等功能。图4 所示为ARM 软件控制流程图;图5 所示为FPGA 软件控制构架图。

图4 ARM 软件流程图

图5 FPGA 软件流程图

3 结论

低功耗小型化时频模块实现了频率源与时间电路的集成化设计,用一块单板实现时频设备核心功能;功耗降低为现役时频设备的1/5 以下 (实测单板工作功率小于2W),体积仅为现有铷钟体积的1/10,工作时发热量可忽略(铷钟工作时发热量较大);选用新型芯片原子钟作为频率源,通过测量秒脉冲相位差实现频率调整,达到优于5ms/100d 的守时精度。

[1] 曹远洪,何庆,杨林.芯片原子钟_CPT 钟研究进展[J].电讯技术,2010,1.

[2] 关晓旭,吴昊.新型船用时统可靠性设计[J].无线互联科技,2014.