一种基于Verilog的任意整数分频器实现方法*

2015-01-15谷涛,黄勇,卢晨

谷 涛,黄 勇,卢 晨

(广西民族大学 信息科学与工程学院,广西 南宁 530006)

0 引言

1 任意整数分频器的实现框架

Verilog HDL是电子设计的主流硬件描述语言之一(另一个是VHDL),采用硬件描述语言完成电路设计是当前数字电路设计的主流方法.Quartus II是Altera公司的综合性PLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL 以及 AHDL(Altera Hardware Description Language)等多种设计输入形式[1].Modelsim是MENTOR公司推出的业界最优秀的HDL语言仿真软件,Quartus II可以方便地调用Modelsim进行电路设计的RTL级和门级仿真.尽管在目前大部分设计中,可以使用芯片厂家集成的锁相环资源进行时钟的分频,但通过硬件描述语言设计的时钟分频电路可以节省芯片内部的锁相环资源,而且消耗不多的逻辑单元就可以达到对时钟操作的目的.所以在时钟要求不高的电路设计中,使用语言来说设计分频电路是必要的也是广泛应用的.笔者以Quartus II为设计平台,基于Verilog语言设计了一个任意整数分频器,并在Modelsim中完成仿真[2-3].

任意整数不是奇数就是偶数,所以笔者的设计思路分别对输入时钟源进行奇分频和偶分频,然后再判断分频比是奇数还是偶数.如果是奇数则选择奇分频器输出的信号为最终输出信号(此时偶分频器在执行分频,但分频比不符合要求),如果是偶数则选择偶分频器输出的信号为最终输出信号(此时奇分频器在执行分频,但分频比不符合要求).电路构造简单,在一定程度上缩短了输入到输出的时延.任意整数分频器的实现框架如图1所示.

如图1所示,输入信号clk分别经过奇数分频和偶数分频,然后根据分频比是奇数还是偶数,选择分频后的输出作为最终的输出信号clkk.分频比是奇数,选择奇数分频后的输出,是偶数则选择偶数分频后的输出.对于二进制形式的分频比k,只需要根据最后一位是1还是0即可判定它是奇数还是偶数.例如输入分频比是k[3∶0],可以根k[0]来判断分频比的奇偶性.

图1 任意整数分频器的实现原理框图Fig.1Implementation principle of arbitrary integer frequency divider

2 实现框架中各部分的原理

2.1 奇数分频的实现原理

k倍奇数分频有两种实现办法:

1)首先进行k/2分频(带小数,即等于(k-1)/2+0.5),然后再进行二分频得到[4].这种办法需要先实现小数分频,比较麻烦,所以笔者采用第二种奇分频方法.

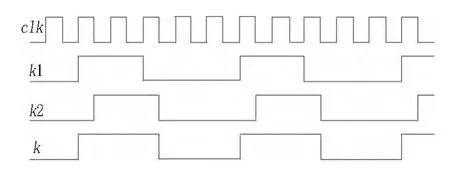

2)通过计数器来实现.一般的方法为:对于实现占空比为50%的k倍奇数分频,首先进行输入时钟上升沿触发模k计数(从0计到k-1),计数到1时输出时钟翻转,然后经过(k-1)/2个脉冲上升沿计数到(k+1)/2时输出时钟再次翻转.然后继续计数,计到k-1时计数器清零继续计数,再次计到1时输出时钟再翻转一次.这样可以得到一个占空比非50%的奇数k分频时钟.再者同时进行输入时钟下降沿触发模k计数(从0计到k-1),计数到1时输出时钟翻转,然后经过(k-1)/2个脉冲下降沿计数到(k+1)/2时输出时钟再次翻转.然后继续计数,计到k-1时清零并继续计数,再次计到1时输出时钟再翻转一次.这样得到另一个占空比非50%的奇数k分频时钟.两个模k计数依次这样循环下去,得到的输出时钟为两个占空比非50%的输入时钟k分频.把它们相或运算,得到占空比为50%的奇数k分频时钟.以5分频为例,奇数分频的实现原理如图2.

图2 5分频原理图Fig.2Schematic diagram of frequency divider(mode=5)

以5分频为例,在图2中可以看到,k1内部的计数器对clk的上升沿计数,k1的输出波形初始为低电平,遇到第1个上升沿计0,遇到第2个上升沿计1,此时k1的输出波形翻转为高电平.遇到第3个上升沿计2,遇到第4个上升沿计3,此时k1的输出波形翻转为低电平.遇到第5个上升沿计4,第6个上升沿计数器清零,第7个上升沿计1,此时k1的输出波形再次翻转,为高电平.然后依次类推……我们可以看到从第2个上升沿到第7个上升沿之间,k1的输出波形形成了一个完整的脉冲.随着第8个及后续上升沿的到来,k1的计数器计数和输出波形依次循环下去.k1的输出波形是对clk的5分频,但占空比不是50%.k2的内部计数器计数和输出波形翻转办法与k1类似,只不过k2是对clk的下降沿计数.从图2中还可以看到把k1和k2相或,可以得到占空比为50%的5分频信号k.

2.2 偶数分频的实现原理

偶数分频原理为:当进行占空比为50%的k倍偶数分频时,可以由待分频信号clk的上升沿去触发计数器计数.当计数器从0计数到(k/2)-1时,输出信号进行翻转,同时给计数器赋值为零.待分频信号clk的下一个上升沿到来时重新从0开始计数,计数到(k/2)-1时,输出信号再次进行翻转,计数器再次赋值为零,以此循环下去.采用这种方法可以实现占空比为50% 的任意偶数倍分频[5].这里不再做详细叙述.

2.3 输出信号选择原理

因为可以根据k[0]来判断分频比k[n∶0]的奇偶性,所以把k[0]作为选择输出信号的依据.k[0]=1选择奇数分频的输出作为最终输出信号,k[0]=0选择偶数分频的输出作为最终输出信号.这个在Verilog中可以用条件赋值语句实现,具体语句将在下面的程序中给出.

3 任意整数k分频器的完整Verilog设计程序及测试程序

3.1 任意整数k分频器的完整Verilog设计程序

module kfenpin(rst_n,clk,k,clkk);// 该 例 中任意整数k为输入值k

程序中rst_n是全局的复位信号;clk是输入的待分频时钟信号;k是输入的分频比,该例程序中是4位二进制输入信号,可以改变位宽来达到实现更大分频比的目的;clkk是分频后的输出信号.

3.2 任意整数k分频器的测试程序

任意整数k分频器的测试程序如下:

4 仿真结果

在上述设计程序和测试程序下,在Quartus II程序中调用Modelsim,可以看到仿真结果.

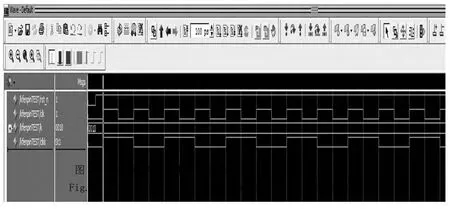

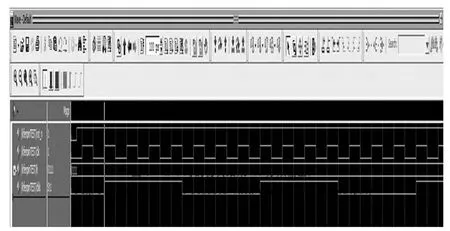

在测试程序中,k赋不同的值,就可以得到相应的分频输出.下面给出k=2,k=7,k=8的仿真结果:

可以看到除了最初的几个周期外(具体几个周期与分频比有关),输出信号是输入信号的k分频.该例程序的2分频的仿真测试也可以通过.

图3 k=2时的仿真结果(2分频输出)Fig.3The simulation results when k =2(2divider output)

图4 k=7时的仿真结果(7分频输出)Fig.4The simulation results when k =7(7divider output)

图5 k=8时的仿真结果(8分频输出)Fig.5The simulation results when k =8(8divider output)

[1]潘松,等.EDA技术实用教程-Verilog HDL版[M].北京:科学出版社,2013.

[2]帅旗.基于FPGA的全数字锁相环的设计与实现[D].大连理工大学工程硕士学位论文,2013.

[3]张成.基于FPGA的全数字锁相环的设计与应用[D].合肥工业大学硕士学位论文,2010.

[4]邓玉元,等.数字电路中等占空比分频器的实现[J].现代电子技术,2006(24).

[5]黄国达.基于FPGA的任意整数分频器的设计[J].福建电脑,2013(7).