基于FPGA的声发射检测仪的设计

2015-01-10王银玲李华聪

王银玲,李华聪

(西北工业大学 动力与能源学院,西安 710072)

飞机在服役过程中受外界环境(如气温、湿度、紫外线辐射、酸雨等)作用、表面处理和涂层缺陷、多余物堵塞排水孔等都可能引起局部腐蚀,腐蚀会影响材料的组织结构性能,并产生疲劳裂纹。机身铝蒙皮铆接以及进气道等部位常发生腐蚀,而裂纹通常由腐蚀造成,并在载荷作用下产生疲劳裂纹扩展,因此飞机的机翼大梁、发动机和起落架等部位常产生裂纹。在第一时间发现各类缺陷并对缺陷进行检测和危害程度评估,对于保障飞机的安全飞行具有十分重要的意义。声发射检测是一种重要的无损检测技术,它利用耦合在材料表面上的压电陶瓷探头,将材料内声发射源所产生的弹性波转变为电信号,然后对电信号进行放大和处理,使之特性化,并显示和记录,从而获得材料内声发射源的特性参数,通过分析即可获得材料内部的缺陷情况。

为了得到较高的采样精度及传输速率,声发射测试仪器通常采用有线的传输方式。而对于一些移动的物体,必须采用无线方式进行数据传输。然而无线传输数据量小,制约了声发射测试仪器的数据采集速率及仪器的采样精度,通常此类仪器只能采用简化的波形特征参数方式。

1 声发射遥测系统设计方案

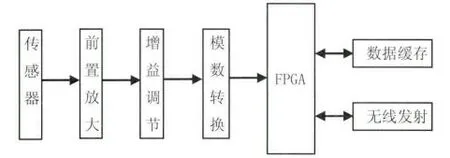

声发射检测系统由下位机和上位机两部分组成,基本体系结构如图1所示。下位机负责数据的采集、存储及发送任务;上位机对发送的数据进行存储、分析处理;下位机与上位机间的数据传输部分采用无线方式。通过图1可以看到,下位机的核心是数据采集及其硬件方面的设计,而上位机主要负责对采集的数据进行处理。

图1 声音检测系统基本体系结构

1.1 下位机硬件设计

下位机是基于FPGA 控制的现场主机,系统硬件包括传感器模块、增益调节放大电路、ADC 模数转换电路、FPGA 控制模块、数据存储模块、无线传输模块,硬件体系结构如图2所示。

图2 下位机硬件体系结构

声发射信号的频率分布与材料或构件的具体特性有关,其范围可从次声波到超声波,使用频率在20kHz~2 MHz之间。由于该设计针对金属构件,其裂纹的声发射信号检测使用频率的范围在100~300kHz之间,故检测系统选用频带在50~400kHz 的美国物理声学公司的声发射传感器R15。前置放大电路将传感器微弱的信号放大,设计选用美国物理声学公司1220系列中带通频率范围为100~300kHz的前置放大器。前置放大器的输入有单端和差动两种方式,分别配用不同的传感器。差动传感器和差动放大器具有较强共模电压干扰抑制能力,可以适应于较强的电磁干扰环境的声发射信号检测,但差动传感器的灵敏度较低。该设计所采用的传感器类型为单端谐振传感器,为了与传感器匹配且获得较高的灵敏度,选用单端输入的前置放大器。前置放大器有20、40、60dB三种信号放大率,对应的输出信号峰-峰值为20,20,6,现场可以通过信号的强弱选择合适的波特率,以达到最优的效果。前置放大器的信号与电源共用,供电要求为+28V。经过C1的信号VS2为交流信号,电容C1的作用是将直流分量滤除,剩下经前置放大器放大的交流信号。AD 转换要求输入电压最大不超过5V,所以在进行AD 转换前首先要对输入信号的幅度进行调制。

选择ADA4898 作为调制电路中的放大器。ADA4898是一款超低噪声和失真、单位增益稳定、电压反馈型运算放大器,工作电压范围为±5V 至±16V。它内置一个线性、低噪声输入级,并具有内部补偿功能,可实现高压摆率和低噪声。ADA4898的带宽为65 MHz,其内置的消除电路可降低输入偏置电流。

调制电路如图3所示,VREF 为+2.5V 的参考电压,先通过前一级运放AR2-A 构成增益为1的电压跟随,然后再通过后一级运放AR2-B 进行翻转,输出-2.5V 的参考电压,最后将前置放大信号与-2.5 V 的参考电压通过AR1 进行差分运算。在此电路中AR1的+IN 和-IN 间的压差可忽略不计,D1、D2两个稳压二极管起限压保护作用。由电路图可得,要将输出信号Vout的范围设置在0~5V,取R3、R4、R5为1K,R2为7K。

图3 增益调理电路

通过增益调理电路将信号转变为0~5V,接下来进行AD 转换。由于放大器的频率范围为100~300kHz,根据奈奎斯特采样定理和探头探测声发射信号的频率范围,则要求AD 的采样频率为600kHz或以上,为了使重构信号波形完美,AD 采样频率应该在最高频率的10倍以上。综合考虑系统的要求及后期的可扩展性,AD 转换选用单路模数转换芯片AD 9240,其采样精度为14bit,采样速率为2.5 MSps。

AD 转换电 路如图4所 示,AD 9240 的7 脚 为FPGA 发送时钟信号,VINA 和VINB 为模拟量输入端。在该设计中采用单端输入模式,增益调节后的信号ADCIN1接入AD9240的41脚作为输入信号。AD 9240 的SENSE 引脚接地,VREF 输出2.5V的标准电压;OTR 引脚为信号幅值检测端,当AD 9240输入信号幅值超出输入范围时将输出高电平1;BIT1~BIT13为模数转换后输出的二进制信号。

图4 AD 转换电路

因为4路AD 同时采集,且要求各通道采样间隔时间不大于1μs。而MCU 控制为顺序操作,要做到各路1μs内的延时很难办到,所以就要考虑并行处理的可编程逻辑器件,通过FPGA 实现数据的高速采样、读取、存储及处理等操作。可编程逻辑器件选用EP4CE6F17C8,EP4CE6F17C8芯片采用256 个引脚的FBGA 封装形式,外部时钟源为50 MHz,可以通过PLL 进行倍频。由于FPGA 内部没有程序存储单元,所以需要外部扩展,本设计采用M25P16(或EPCS16),其实质是一个容量为16 Mbit串行FLASH 芯片,这对于存储FPGA 中的程序绰绰有余,同时还可以存储软核NIOS II的应用程序。JTAG 程序下载电路如图5所示。

图5 JTAG 下载电路图

由于AD 转换芯片选择AD9240,其没有片选使能引脚,如果以总线方式相连,需要通过硬件进行扩展,而这将增加设计复杂度,再者时序也不好控制。由于每个AD 接口需要14路数据线、一路时钟信号一路OTR 溢出检测共计16根信号线,当4路AD 都与FBGA 相连需占用64个引脚。设计采用FPGA 引脚与AD 数据输出接口直连,这样利用FBGA 的并行处理可以实现真正意义上的4路信号同步采集,达到零延时。如果按2.5 MSps的采样速率计算(数据宽度为16 位),则每路数据量为40 MBit,4路总的数据量为160 MBit,如此大量的数据不可以实时无线传送出去,所以要加入一个暂时存储单元,等一次声发射事件结束后再将采集的数据全部传送。由于每次声发射时间不超过1s,所以可以将采集的4路数据首先存入SDRAM 中,等到一次声发射事件结束后再通过无线方式传到上位主机。

数据暂存单元选择SDRAM,其型号为HY57V2562GTR,容 量256 Mit(16M*16bit)、16bit总线,工作频率133 MHz。本设计给其时钟引脚频率选择2倍频,即100 MHz。SDRAM 是整个FPGA 的缓存区,可以暂存数据。另外,由于本设计需要占用大量资源的NIOS II软核,FPGA 内部的ONCHIP RAM 无法满足需求,而SDRAM 作为系统的“内存”,保证了整个系统的稳定运行,既存储FPGA 运行时的程序,也存储AD 转换后的数据。SDRAM 的连接方式如图6所示,S_A[0…12]为地址线接口,BA0和BA1为SDRAM 的bank存储选择位;S_DB[0…15]为16位数据线接口。

图6 SDRAM 接口

通常在数据吞吐量大的地方采用FIFO 以实现数据缓冲,这种结构又称为乒乓结构。乒乓结构是一种典型的用于数据流控制的处理技巧,它通过对输入输出地址线的操作分别对输入输出数据块进行切换,把经过缓冲结构的数据不停留的送到后续单元进行传输或运算等处理。整个乒乓结构作为一个整体,对于输入数据流和输出数据流都是连续不停顿的,符合流水线处理的思想,所以可以通过Quartus II软件通基于QSYS快速建立片内FIFO。

接下来设计无线通信部分,采集到的数据需要通过以太网实现无线发送,EP4CE6F17C8 可通过SOPC配置网络接口。通信芯片采用低成本10/100M 以太网接口芯片DM9000A,采用48引脚的LQFP封装,内置16KB SRAM。此芯片可以实现以太网媒体介质访问层(MAC)和物理层(PHY)的功能,包括MAC数据帧的组装拆分与收发、地址识别、CRC编码校验、MLT-3编码器、接收噪声抑制、输出脉冲成形、超时重传、链路完整性测试、信号极性检测与纠正等。DM9000A 的总线宽度分为8bit和16bit两种模式,每种定义时引脚有差异,本设计选择总线宽度16bit模式配置,电路原理如图7所示。

IOR#为处理器读命令,低电平有效;IOW#为处理器写命令,低电平有效;CS#为片选使能信号;CMD 为命令类型,当为高电平时访问数据端口,当为低电平时访问地址端口;INT 为中断请求信号,高电平有效;SD0~SD15 为处理器的16 位数据总线。为了提高开发速度以及无线传输的可靠性,无线收发模块采用成熟的技术方案。

图7 以太网接口电路图

1.2 下位机软件设计

在整个数据采集模块中,核心控制功能通过FPGA 完成,软件开发采用Altera公司的Quartus II 11.0 开发环境。在设计中所需的硬件主要为FPGA、SDRAM、AD 转换、网络接口这几部分,如何协调它们间的工作是设计中的重点,由于FPGA是并行操作,而顺序操作对其显得力不从心,一般常用的方案为FPGA+MCU 的控制模式。由于放大、滤波以及增益调节已通过硬件完成,所以软件设计只需要从模数转换开始。FPGA 采用的是一种模块化设计思想,各模块系统具有独立性及非时序性,使得完全意义的并行处理成为可能。

NIOS2是专为Altera公司开发的系列FPGA的软核处理器,可以在FPGA 内部建立一个软核,通过它来控制外部芯片,建立的内核如图8 所示,FPGA 内核主要由NIOS II核、SDRAM、JTAG_UART、PIO、FIFO、On Chip Memory、System ID、EPCS、DMA、PLL、Ethernet等构成。

当给AD9240一个外部时钟信号,则进行一次AD 转换。由于本设计采样最高频率为300kHz,所以根据采样定理及实际经验,最终采样频率取2.5 MHz比较合适,所以要对系统时钟进行20 倍分频,作为AD 转换时钟。为了实现4路AD 采样同步,需要一个PLL 锁相环。AD 转换数据输出格式如表1所示,数据宽度为14位。由于转换后的数据存入SDRAM,而SDRAM 的数据位宽度为16位存储,所以有2位数据宽度空闲。而AD 采样共4路,所以在数据存储到的时候将最高的2位作为路选位,即00~11分别代表AD0~AD3的路选信号,与数据共同存储。同时,将最高2位设置为通路标志,可以在最后数据处理中进行校验,防止跳变引起的数据通路不一致的错误。

图8 FPGA 内核

由于设计声发射系统的工作状况为检测瞬时单个事件,而不是检测物体的连续声发射事件,所以需要检测事件是否达到采集的条件,这就需要门限检测。为此系统工作时4路AD 实时将采集的数据与给定值比较,当达到触发条件时4路AD 将转换的数据依次存入SDRAM 中,直到单次事件结束,在这里强调的是受SDRAM 存储影响以及声发射事件特点,整个持续时间不超过1s。等一次声发射事件结束后,通过无线网络模块将数据传输至上位机进行分析处理。

2 试验数据及分析

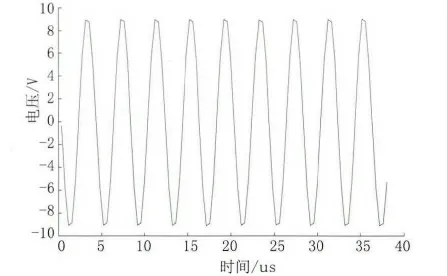

为了验证方案的有效性,需要对系统进行测试。通过信号发生器对4路AD端输入频率为300kHz、峰值电压为20V 的正弦信号,通过上位机得到4组数据,选择AD0路信号进行处理。由表1可知其最高计数值为16 384,而输入电压为20V,所以要将二进制数转换为幅度为±10V 之间,其采样间隔时间为0.4μs,任意选取95组数据,通过Matlab对数据拟合,结果如图9所示。由图可以看出,实际的波形幅值与给定有一个差值,一般不超过20%,而图中的幅值衰减大约10%,这与放大器的实际放大倍数及AD转换的量化误差有关,这些都可以通过后期的数字信号处理进行软件补偿,而输出的波形与输入波形与相吻合,证明了硬件设计的正确性。

3 结语

目前声发射检测无线检测相关研究工作正处于起步阶段,笔者设计的无线高精度全波声发射检测仪器,对航空航天设备进行在线检测,维护以及延长飞机的服役寿命具有一定的保障作用。

表1 AD9240输出数据格式

图9 采样输出波形图

[1]吴继华,蔡海宁,王诚.Altera FPGACPLD 设计(高级篇)[M].北京:人民邮电出版社,2011.

[2]徐洋,黄智宇,李彦,等.基于Verilog HDL 的FPGA设计与工程应用[M].北京:人民邮电出版社,2009.

[3]王银玲,孙涛,曾小进.基于单片机的以太网与RS485通信网关设计[J].工矿自动化,2008(4):92-94.