基于FPGA的LED屏控制器设计

2015-01-06夏建雄陈海燕

夏建雄∗,陈海燕

(国防科学技术大学计算机学院,湖南长沙410073)

基于FPGA的LED屏控制器设计

夏建雄∗,陈海燕

(国防科学技术大学计算机学院,湖南长沙410073)

通过对大型户外全彩LED显示屏的研究,基于FPGA设计了一种LED显示屏的控制系统。该系统主要工作基于Altera公司提供的DE1开发板上进行设计,在Quartus II的软件开发环境下,采用层次化设计,用Verilog HDL语言建立分频时钟模块、数据采集和重组模块、扫描驱动模块,最后连接成一个整体的系统模块,进行仿真和调试,完成FPGA控制系统的设计。通过SPI通信协议发送数据,完成了64×64的LED屏的图形显示,从而验证了LED大屏幕的设计方法。本方案实现的显示控制系统方法,满足目前LED大屏幕区域显示和高速处理图像数据的要求,具有稳定性高、设计灵活等特点。

现场可编程门阵列;发光二极管;Verilog硬件描述语言;扫描驱动

1 引 言

早期及目前市场上出现的一些规模较小的LED显示系统,一般都采用单片机作为主要的控制系统。一方面,单片机的驱动频率较低,不能驱动高分辨率的LED全彩显示屏。另一方面,对于LED全彩大屏幕来说,要求传输的数据量大、扫描速度快,对于传统的单片机而言,由于内部资源少、运行速度慢,不能满足系统要求。现在,一些大屏幕全彩显示系统主要采用32位微处理器作为LED系统的核心控制芯片,但设计系统不够灵活,在改变显示屏的尺寸大小时,需要较大幅度地修改控制系统的设计,不利于提高开发效率。如果以FPGA作为主要控制器,不仅能够用软件编程来实现硬件功能、有效地简化电路结构,速度很快;而且它的外接引脚资源丰富,扩展性较强[1-2]。因此,用一个FPGA和简单的外围电路就能控制LED大屏幕的显示。

随着微电子设计技术的不断发展和工艺技术的提高,现场可编程器件的性能不断提高,可靠性高、处理速度较快,集成度越来越高,使得FPGA能够满足高速视屏数据的处理能力,同时减小控制系统的体积。FPGA的设计灵活,根据项目的需要,采用Verilog HDL或VHDL语言来编程,灵活修改相应的应用程序即可满足要求。采用FPGA方式控制,能够实现在线升级,大大增加了设计的灵活性,同时也使得设计周期大大地缩短。

2 LED显示屏的扫描方式

实验所用的每块LED都是由红、绿、蓝三基色组成的P10户外全彩的单元板,单元板的模组分辨率是宽16点×高16点,每块LED单元板采用两个HUB75接口作为模组接口,12块相同的JXI5020芯片作为LED单元板的驱动芯片,采用1/4的扫描驱动方式,恒流驱动刷新频率大于300 Hz,可以保证摄像无抖动。因此该实验单元板可以考虑1/4扫描方式、直线行走,一路数据带4 行,共4路数据。

首先利用单片机进行数据输入,测出数据走线方式。用二进制ABC来表示行选择控制信号的输入端,先将A=0,B=0,C=0,从时钟信号CLK输入端给予一个时钟信号,使DR1=1,DR2=0,DG1=0,DG2=0,DB1=0,DB2=0,按照JXI5020芯片的功能和时序,给予一定的控制信号,发现LED灯闪一下就熄灭。通过分析可知,由于单元板内部的PR4538芯片能够实现和74HC123等效功能的单稳态电路,在行译码控制信号输入停止跳变130 ms时,单稳态保护电路将起作用,整个电路处于保护状态,关断行译码信号的输出。只有地址变化很快,才能让使能信号OE起作用,从而看到显示的信息。同理可对其他数据输入端口进行测试,最终发现R1、G1、B1控制上8行的数据显示、R2、G2、B2控制下8行的数据显示。

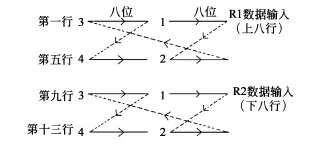

根据单片机控制的LED数据显示,可以知道数据走线方式如图1所示:先将数据从第一行的第九列开始送入,送完八位数据后若再有数据送入,先前数据继续从第五行的第九列开始送入。按如图所示方式送入数据,经过32个时钟周期后,数据最终送入如图所示的两行中。当32位数据完全输入时,可将LE置高电平将数据传入到32位的锁存器,等数据稳定后,将OE置低电平,此时32位的并行数据输出至驱动器进行控制显示,再进行行信号切换,可将整个显示屏数据进行显示。

图1 数据走线方式Fig.1 Arrangement method of the data

3 基于FPGA的控制设计

3.1 总体设计方案

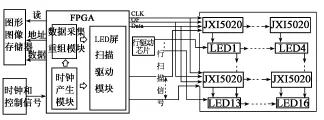

本设计方案采用现场可编程逻辑器件(FPGA)EP2C20F484作为核心板来实现对LED显示屏的控制,用16块相同的单元模板组合成64× 64的显示屏,设计好级联方式进行控制。在时钟和控制信号的作用下,按照地址从图形、图像存储器中依次读出数据,将读出的数据在FPGA的控制下送入到LED显示单元板,通过控制时钟信号、使能信号及行选择信号进行控制,最终在LED全彩显示屏中进行显示[3]。由于FPGA器件具有丰富的输入输出接口、内部逻辑及连线资源,可以采用Verilog HDL语言进行程序代码编写、仿真和调试过程。采用自顶向下的模块化设计来设计基于FPGA的LED全彩显示屏控制器。总体设计方案如下:

图2 显示屏设计方案Fig.2 Design scheme of the display screen

对大屏幕LED显示屏来说,每列显示的数据采用串行输入的方式进行输入,每行采用1/4的扫描方式进行扫描。每两块JXI5020芯片进行级联,能够实现32位的移位、锁存和并行输出的功能,所以列驱动器采用2个JXI5020进行显示和驱动。在时钟控制信号的作用下,数据从JXI5020的SDI端口一位一位地输入,当两行的所有16列数据传送完后,输出锁存信号LAT并选通控制行信号,则第1行和第5行的各列数据就会可按照数据的要求进行显示。当16行所有的数据扫描完一遍后,就完成了一个周期的信号扫描,随后可以接着从第1行和第5行进行下一个周期的扫描,从而可以完成图像数据的切换显示,只要满足扫描周期不超过10 ms,LED显示屏就不会出现闪烁的现象[4-5]。

此次设计的关键技术问题:就是要处理好FPGA内部逻辑中各个模块之间的问题,这将关系到LED显示屏控制系统功能的实现。(1)数据的采集和重组,由其他芯片解码出来的数据或由其他软件提取出来需要显示的数据,由于LED显示屏数据走线方式的特殊性,需要将提取出来的数据进行重组,再将重组好的数据按照相对应的地址依次存入到存储器中,便于后续数据的读取。(2)LED显示屏的扫描驱动模块,这是设计的核心单元模块。将存储器中的并行数据转化为串行数据、数据配合好时钟信号进行发送以及显示屏控制信号的产生,需要非常清楚LED显示屏各个功能模块的控制信号的功能和控制的时序。

费希尔上将和丘吉尔都不幸言中了石油之重。石油为这些机械和武器提供了动力资源。但是,石油对战争胜负的决定程度及战争对石油的依赖程度,却是任何领导人都始料不及的。汽油用来给战争武器供应能量,从而使石油成为具有高度战略意义的物资资源。以汽油发动机为核心的军事装备的使用,使石油在第一次世界大战的舞台上尽显风流。从此之后,世界各国对石油的争夺战更是前所未有。

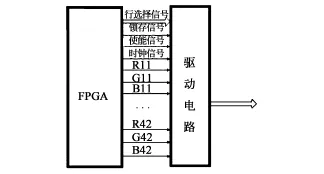

3.2 硬件部分设计

对于硬件模块部分,本次设计的顶层系统模块包括时钟分频模块、数据采集和重组模块和LED驱动显示模块。时钟分频模块就是把接收到的FPGA内部50 MHz的时钟输入信号转变为LED显示模块所需要时钟信号[6]。LED显示屏的显示控制模块,用来控制LED显示屏的显示控制。本次设计需要FPGA提供个输入输出接口32个引脚,如图3所示[7]。

(1)数据总线24根;

(2)控制总线5根,分别是使能控制信号1根、数据锁存信号1根、复位信号1根、时钟控制信号2根;

(3)行片选信号2根。

图3 FPGA的外围电路Fig.3 Peripheral circuit of the FPGA

3.3 模块部分设计

3.3.1 时钟产生模块

作为时序电路,大部分控制器都需要时钟信号来提供时序信号。FPGA内部含有晶体振荡器,通过自带的晶振电路,可以提供时钟信号。为了获得工作需要的时钟信号,往往要对内部提供的时钟信号进行分频或倍频。晶振电路提供的时钟信号,可以利用计数器或内部锁相环进行分频或倍频。分频器是时序电路中常用的一种电路,可以将系统提供的时钟信号根据具体的要求分频得到所需的时钟控制信号。刷新频率过低,就会感觉到闪烁现象,刷新频率过高,会使显示的数据不够稳定,使得传输数据出现错误。为了使人眼感觉不到闪烁的现象且传输数据稳定无误,显示屏的刷新频率至少要大于24 Hz,一般小于100 Hz。由于本次设计的显示屏移位数据可以看成是128位的数据,相当于对24组数据同时输入,进行1/4扫描,同时对4组显示屏进行扫描驱动显示,所以移位时钟频率的范围为0.123~0.512 MHz。对FPGA内部提供的50 MHz时钟信号进行300分频,得到0.167 MHz的时钟频率,能够满足要求。

3.3.2 数据采集和重组模块

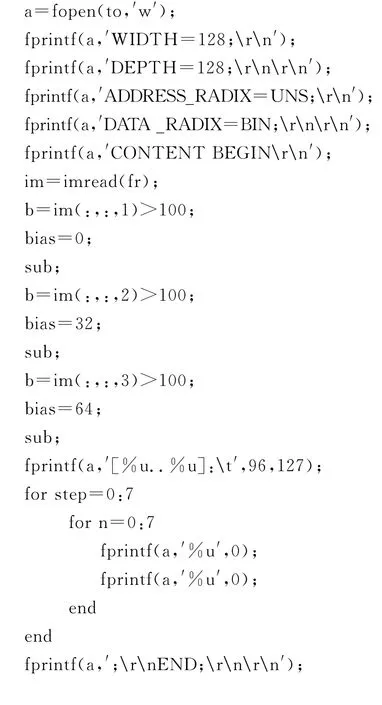

对于64×64的LED全彩显示屏,若要对一幅彩色图像进行显示,可以用Matlab编程按照一定的规律提取一幅图片的信息,先提取红、绿、蓝各种颜色分量,然后根据各分量显示数据的要求,将各分量的数据信号进行重组,组成128位的数据,将红、绿、蓝信号生成宽度为128位,深度为128位的mif文件。在Quartus II中添加工程文件,将mif文件导入到Quartus II中编译,存储到存储器中,编写Verilog HDL语言,再次采集和重组数据,通过扫描驱动控制将一幅全彩图像完全显示在LED大屏幕上。Matlab提取全彩图像的部分程序如下:

3.3.3 LED驱动显示模块

本设计采用的是LED全彩户外显示屏,用JXI5020作为驱动电路完成串行到并行的数据转换,APM4953为使LED灯电流信号放大功能的芯片,另外,由74HC138作为行选择器。显示屏的接口包括时钟信号、串行数据输入、行选择信号、使能信号和锁存信号。

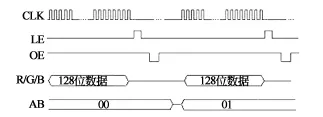

驱动时序分析:由于LED全彩显示屏扫描特性,输入的数据先通过移位寄存器输入到显示屏,再进行并行驱动显示。通过JXI5020驱动芯片将串行的数据转换成并行的数据,待两行整体数据发送完毕后,通过行选择信号选择该行导通,由74HC245芯片进行功率放大,由APM4953芯片进行驱动显示。LED全彩显示屏的模组中有时钟信号线CLK、数据锁存信号线LE、使能信号线OE、行选择信号线A、B和R、G、B三个数据线[8]。

图4 LED控制时序Fig.4 Control sequence of the LED

图4为LED控制时序,利用FPGA控制存储器每次读取128个像素点的一个分量值,经过128个时钟周期后将数据送入到显示屏,当两行的128位数据完全送完后,将LE置于高电平,就将数据输出锁存器,再将使能信号OE置低电平进行显示,同时将行选择信号加1,进行下两行数据的输入。当A、B加到4后进行清零,反复循环点亮显示屏,由于人眼的惰性,可以看到显示屏是持续亮着的,而不会出现闪烁现象。

显示控制模块对接收到的数据进行处理、重构,获得需要的数据格式。然后产生合适的地址和控制信号,将数据发送到LED显示屏进行驱动显示,这部分控制电路是控制系统的核心部分。本次试验用16块16×16的单元模板组成,可以考虑将这些模组分成4组,每一组由4块相同的单元板组成,对4组可以并行驱动显示,每一组都是由16行组成的,因此需要对各行进行扫描。因为4组进行并行驱动,可以克服由于逐行扫描导致显示时间不够长,LED显示亮度不够高,也可以避免闪烁现象的出现[9]。

4 硬件验证

4.1 LED单元板的JXI5020芯片功能仿真

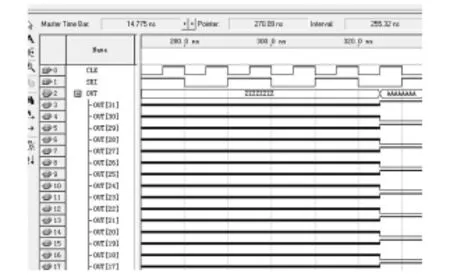

根据JXI5020脚位图、管脚说明及功能图,可以知道JXI5020具有16位串行输入并行输出的移位、并行锁存及三态输出等一些功能。对于移位缓存器及锁存器,都分别具有独立的时钟控制信号,在数据和时钟信号的上升沿,数据可以移入到移位寄存器,待输入完后,在LE锁存信号的上升沿将数据进行锁存,当OE为低电平时,数据将输出到LED显示屏中,因此在显示每一行数据时还可以进行下一行数据的输入准备,不会引起数据在传输过程中的冲突问题。将两片JXI5020芯片进行级联,可以使LE置低电平,OE置高电平,避免数据传入至锁存器,同时在时钟信号的上升沿,从SDI端将串行数据输入至32位的移位缓存器中,经过32个时钟周期后,32位的输入数据可以存入到移位缓存器中。此后将LE置高电平时,串行输入数据会被传入到32位的输出锁存器,等数据传入至锁存器中稳定后,可以将OE置低电平,此时32位的并行数据输出至驱动器进行控制,通过R-EXT外接电阻控制输出电流的大小。

首先要根据时钟信号,产生满足上述条件用来控制JXI5020芯片的使能信号OE和锁存信号LE,每经过32个时钟信号后,将LE从低电平切换到高电平,并且能够在LE置高电平一段时间待数据输入稳定后,再将OE置低电平。对32位移位寄存器进行时序仿真,结果如图5所示。

从单块LED显示屏时序仿真可以看出,从SDI端输入32位的数据,经过32个时钟周期后,将有32位的数据从OUT端口输出,从而验证了该移位寄存器功能的正确性。

4.2 LED显示屏整体功能验证

整屏彩图的显示:对于64×64的全彩显示屏,对一幅彩色图像进行显示,可以用Matlab编程按照一定的规律提取一幅图片的信息,先提取红、绿、蓝三种颜色分量,然后根据各分量显示数据的要求,将各分量的数据信号进行重组,组成128位的数据,将重组的数据存储到存储器中,在时钟和控制信号的作用下,读取存储器中的图像数据并对LED屏进行扫描驱动显示,结果如图6所示。

图5 LED单元板时序仿真Fig.5 Timing simulation for the LED unit board

图6 全彩图像对比显示结果(灰度图)Fig.6 Comparison results of full color images display(Gray scale image)

第一幅图为需要显示的全彩原图,第二幅图为通过FPGA控制的LED屏显示的全彩图。通过左右两图的对比分析可知,该显示屏基本上能够显示出原来图像。通过上述图像的显示,可以验证全彩LED显示屏控制系统设计的正确性。

5 结 论

本文在研究了LED全彩显示屏的原理和系统结构后,提出了以FPGA为核心的LED显示屏控制器的全套设计方案。采用FPGA实现对系统进行驱动控制,进而控制LED全彩大屏幕的图形、图像的显示。根据硬件的具体设计要求、功能,采用层次化设计多个独立的单元模块,利用Verilog HDL语言进行代码的编写、仿真及调试,最终实现了基于FPGA的LED屏控制器的设计。该控制方案的FPGA总功耗为129.04 m W,其中动态功耗58.24 m W,静态功耗47.46 mW,输入输出接口功耗23.34 mW,功耗较低。本次设计使用的时钟频率仅为0.167 MHz,若用FPGA作为主控芯片来控制LED大屏幕的显示,内部能够提供高达50 MHz的时钟控制信号,外部引脚资源丰富,不仅速度快,而且扩展性强,能够满足数据量大和高速处理大屏幕显示的要求。

[1] 赖义汉,张卫平,傅智河.基于FPGA的LED大屏幕控制系统设计[J].单片基于嵌入式系统应用,2011,(2): 66-69.Lai Y H,Zhang W P,Fu Z H.Control system of LED large display based on FPGA[J].Microcontrollers&Embedded Systems,2011,(2):66-69.(in Chinese)

[2] 张玉杰,马立云,张贺艳.基于ARM和FPGA的LED显示屏控制系统的设计[J].计算机测量与控制,2009,17 (12):2429-2431.Zhang Y J,Ma L Y,Zhang H Y.Design of LED screen display control system based on ARM and FPGA[J].Computer Measurement&Control,2009,17(12):2429-2431.(in Chinese)

[3] Zhou Y Y,Lv C Z,Gao T,et al.Design of LED display based on FPGA[J].Journal of Measurement Science and Instrumentating,2013,4(1):77-82.(in Chinese)

[4] 叶心明.基于FPGA的LED视频显示控制系统的设计[D].上海:上海交通大学,2009.Ye X M.Design of control system of LED video display based on FPGA[D].Shanghai:Shanghai Jiao Tong University,2009.(in Chinese)

[5] 李欢欢,秦实宏.基于FPGA的大屏幕扫描控制系统的设计[J].武汉工业学院学报,2010,29(3):83-85.Li H H,Qin S H.Design of FPGA-based large screen scan control system[J].Journal of Wuhan Polytechnic U-niversity,2010,29(3):83-85.(in Chinese)

[6] 徐绘峰.基于FPGA的LED视频显示控制系统的设计[D].武汉:武汉科技大学,2010.Xu H F.Design of LED video display control system based on FPGA[D].Wuhan:Wuhan University of Science and Technology,2010.(in Chinese)

[7] Qin S H,Li H H.The research of LED display screen based on embedded technology and FPGA technology[C].2010 International Conference on Electrical and Control Engineering,2010:2411-2413.

[8] 刘九维.基于FPGA的大型户外全彩色LED屏控制系统设计[D].重庆:重庆大学,2010.Liu J W.Design of full-color outdoor LED large screen control system based on FPGA[D].Chongqing:Chongqing University,2011.(in Chinese)

[9] 郭宝增,邓淳苗.基于FPGA的LED显示屏控制系统设计[J].液晶与显示,2010,25(3):424-428.Guo B Z,Deng C M.Design of LED display control system based on FPGA[J].Chinese Journal of Liquid Crystals and Display,2010,25(3):424—428.(in Chinese)

Design of LED screen controller based on FPGA

XIA Jian-xiong∗,CHEN Hai-yan

(School of Computer Science,National University of Defense Technology, Changsha 410073,China)

Through the study of the large outdoor full color LED display screen,a control system of LED display screen was designed based on FPGA.The system was designed on the platform of the Altera DE1 development board.In the software development environment of QuartusⅡ,a hierarchical design was applied.A complete system module consists of a frequency divided clock module,a module for data acquisition and reorganization,and a scan driver module with the use of the Verilog HDL language.Simulation and test were also conducted for the final FPGA control system.Moreover,the design of a LED large screen was also verified by using the SPI communication protocol to send data to realize the graphic display of a 64×64 LED screen.The display control system method of this scheme met the demand of current LED area of the large screen display and image data high-speed processing,having the characteristics of high stability,flexible design etc.

field programmable gate array;light emitting diode(LED);Verilog hardware description language;scan driver

TP873

:A

10.3788/YJYXS20153005.0838

1007-2780(2015)05-0838-06

夏建雄,男,(1989-),湖南邵阳人,硕士研究生,研究方向为微电子学与固体电子学,微处理器设计等。E-mail:jianxiongxiascu@163.com

2014-11-19;

:2015-01-13.

∗通信联系人,E-mail:jianxiongxiascu@163.com

陈海燕,女,(1967-),四川南充人,硕士,研究员,硕士生导师,主要从事微处理器设计,集成电路设计等方面的研究。