一种输入级模块复用的In-Zn-O薄膜晶体管行集成驱动电路

2015-01-06张立荣1李冠明2黄长煜3雷1罗东向2苗2吴为敬2彭俊彪2

张立荣1,李冠明2,黄长煜3,周 雷1,罗东向2,徐 苗2,吴为敬2∗,彭俊彪2

(1.广州新视界光电科技有限公司,广东广州510730; 2.华南理工大学发光材料与器件国家重点实验室,广东广州510640; 3.华南理工大学电子与信息学院,广东广州510640)

一种输入级模块复用的In-Zn-O薄膜晶体管行集成驱动电路

张立荣1,李冠明2,黄长煜3,周 雷1,罗东向2,徐 苗2,吴为敬2∗,彭俊彪2

(1.广州新视界光电科技有限公司,广东广州510730; 2.华南理工大学发光材料与器件国家重点实验室,广东广州510640; 3.华南理工大学电子与信息学院,广东广州510640)

提出了一种新型的基于In-Zn-O薄膜晶体管(IZO TFT)的行集成驱动电路。该电路采用了输入级模块复用的驱动方法,即一级输入级驱动多级输出级,因此可以显著地减少输入级模块TFT的数量,缩减电路的面积,满足高分辨率显示屏设计,同时也可以迎合显示屏窄边框的审美需求。电路的输入级模块工作时间是输出级模块的n倍(n是一级输入级模块驱动输出级模块的级数),因此输入级尺寸可以做得更小。另外,该电路的驱动时钟频率是传统结构中一级输入级模块驱动一级输出级模块时钟频率的1/n,有效地降低了电路的动态耦合功耗。我们制作了20级的行集成驱动电路,一级输入级模块驱动两级输出级模块,该电路的尺寸为宽730μm,高为164μm,满足窄边框的要求。从实验测结果表明,该电路很好地满足300 PPI的AMLCD或AMOLED显示屏的需求。

In-Zn-O薄膜晶体管;行集成驱动电路;输入级模块复用;输出级模块

1 引 言

薄膜晶体管制作的行集成驱动电路代替专门的行驱动芯片,其优点在于:首先,行集成驱动电路能够与像素电路制作在同一阵列上,合理的布局可以避免走线长度不一而导致不同的延时,在大尺寸面板影响尤为严重;其次,可以节约基板面积,减少工艺步骤,降低成本,应用在小尺寸显示屏,可以实现窄边框,符合人们审美需求。由于TFT构成的行集成驱动电路具有相对明显的优势,近年来成为背板TFT技术研究热点[1-4]。

目前,在平板显示领域中,应用于有源显示驱动的TFT主要有非晶硅TFT(a-Si TFT)和多晶硅TFT(Poly-Si TFT)[5-7],a-Si TFT具有工艺简单、价格低、制备成品率高、关态漏电流小等优点。但a-Si TFT载流子迁移率低,器件尺寸制作的比较大,而且需要的驱动电压和信号电压较高,从而行集成驱动电路占用的面积较大,功耗较大,无法实现窄边框和低功耗。多晶硅TFT具有较高的载流子迁移率,节省驱动电路面积。另外,对于多晶硅,可制作n型和p型的薄膜晶体管,这为使用多晶硅TFT实现了在同一衬底上集成制作OLED像素驱动电路及外围驱动电路提供了很大的灵活性。但多晶硅晶化设备相当昂贵,工艺复杂,工艺均匀性不好控制。金属氧化物TFT具有制备温度低、工艺相对简单,迁移率较高等优点,也具备应用于有源OLED平板显示中的潜力。我们制作的掺Ln元素的IZO-TFT具有相对更高的迁移率,更稳定的器件性能,具有应用显示产业的前景[8]。

传统的行集成驱动电路结构一般是一级输入级模块驱动一级输出级模块[9-11]。输入级的工作频率与输出级的工作频率相同。当工作频率增大时,每一级电路的工作时间变短,高电平保持时间减少,每一级电路的充放电时间减少;当频率增加到一定程度时,需要增加电路的尺寸,提高充放电速度,使得电路可以正常工作。通过牺牲面积,提高了电路工作速度,但是随着显示屏的分辨率不断增加,像素面积不断减少,有限的电路面积,难以满足高速电路的工作需求。

Binn Kim[12]等人首先提出了一种新型的IGZO-TFT的移位寄存器,该电路采用了输入级模块复用的结构,针对IGZO-TFT器件,设计了专门结构,抑制器件的泄漏电流,但是过多的驱动时序很容易造成信号竞争冒险的现象,复杂的驱动时序对电路的稳定也提出了挑战,电路信号跨级连接,导致电路最后五级电路无法工作。该电路仅仅基于仿真,没有实验支撑,无法验证其性能。

本文提出一种新型的行集成驱动电路结构,一级输入模块驱动多级输出模块的输入级模块复用驱动方法。该电路一级输入级模块通过电路的共同节点控制多级输出级模块,同时电路不需要跨级连接,也不用牺牲电路后五级电路。输入级模块的工作时间/输出级模块的工作时间=n(n为复用的级数)。输入级模块工作时的充放电时间是输出级的n倍,因此,输入级尺寸较小也可以满足输出级的驱动需求。与传统结构的行集成电路对比,该电路的时钟信号频率更低,可以节省更多的动态功耗。

2 电路设计及工作原理

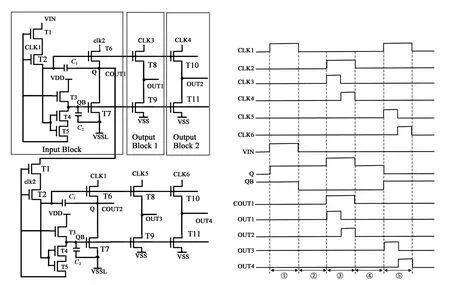

如图1所示,该行集成驱动电路采用每一级输入级模块驱动两级输出级模块的结构,输入级模块由7个薄膜晶体管和2个电容组成,输出级模块由2个TFT组成。电路中,节点Q和节点QB是输入级模块和输出级模块的公共节点,输入级模块通过控制节点Q和QB电平控制两级输出级模块的开关状态。因此,与传统结构相比,该电路结构可以节省一个输入级模块,即7个TFT和2个电容,节省电路面积。

图1 行集成驱动电路原理图和驱动时序图Fig.1 Proposed gate driver circuit and timing scheme of signal lines

该行集成驱动电路采用了6根时钟信号线(CLK1~CLK6),一根正电源线(VDD),两根负电源线(VSS,VSSL),电路工作原理如下:①当CLK1变高电平时,T1和T2被打开,Q点被输入信号VIN充电至高电平,与此同时,T3,T4,T5 被CLK1打开,QB点也被充电至高电平,由于CLK1的高电平与VDD相同,因此T3,T4和T5之间没有直流通路。T6,T8和T10被Q点打开,T7,T9和T11被QB点打开,COUT1输出VSSL低电平,OUT1和OUT2输出VSS低电平,由于CLK1,CLK2的低电平为VSSL,CLK3, CLK4,CLK5和CLK6的低电平为VSS,因此T6 和T7,T8和T9,T10和T11有没有直流回路。②当CLK1变为低电平时,CLK2继续维持低电平,T3被关断,T4,T5维持打开状态,因此QB点被拉低至VSSL低电平,关断T7,T9和T11。③当CLK2变高电平时,CLK1为低电平,T6的漏极连接CLK2,电容C1连接着T6管的栅极和源极,根据电容耦合原理,Q点会跳变到比之前更高的电平,使得T6,T8,T10完全打开。COUT1输出高电平,CLK3,CLK4高电平的占空比为CLK2的一半,如图1,因此OUT1输出与CLK3高电平时间一样的波形,OUT2输出与CLK4高电平一样的波形。④当CLK2,CLK3,CLK4变低电平,CLK1维持低电平,电路COUT,OUT1, OUT2均为低电平。⑤当CLK1再次变高, CLK2为低,此时VIN信号为低电平,因此Q点被拉低到VSSL电平,关闭T4、T5、T6、T8和T10;T3打开,QB点被充电至VDD,将T7、T9 和T11打开,COUT1、OUT1和OUT2拉低,电路COUT,OUT1,OUT2继续维持低电平。

从电路原理图可以看出,COUT1,COUT2是每一级输入级模块的级联信号,OUT1, OUT2,OUT3,OUT4都是输出到显示屏阵列的栅极驱动信号。从电路的驱动时序图看出,输入级模块级联信号的高电平保持时间是输出级模块栅极驱动信号的两倍,因此在同一工作频率下,输入级模块的尺寸可以做的更小。

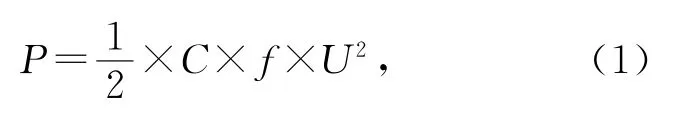

在电路中,两负电源需要满足|VSSL|>|VSS|,可以使得T9,T10在OUT1,OUT2输出高电平时完全关闭,输出信号达到全摆幅输出,减少功耗损失。由于CLK1,CLK2的低电平和高电平分别与VSSL和VDD相当,CLK3,CLK4, CLK5,CLK6的低电平和高电平分别与VSS和VDD相当,因此电路不存在直流回路,电路没有直流功耗,只有时钟的动态功耗。传统结构行集成驱动电路的动态功耗计算公式为:

其中:C为电容,f为时钟频率,U为电压变化。

采用输入级模块复用结构的行集成电路,输入级模块驱动n级输出级模块,其时钟频率为传统结构的1/n,动态功耗为:

其中:f/n为时钟频率。与传统结构的行集成驱动电路对比,输入级模块复用结构的电路可大大减低电路的动态功耗。

3 实验结果与分析

本文采用的器件为我们开发的掺Ln的IZOTFT器件,器件特性分别为:阈值电压为1.28 V,开启电压为-0.95 V,迁移率为15 cm2/V·s,开关比为2.96×109。

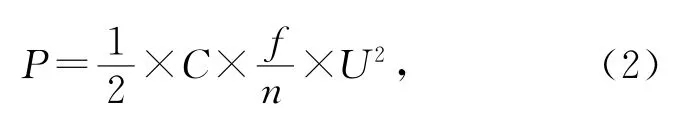

我们成功制作了20级该行集成驱动电路,图2为该电路的电子显微图,每级电路的尺寸大小为730μm×164μm,制作在显示屏的两边很容易实现窄边框显示,164μm的高度适用于300 PPI 的AMLCD或者AMOLED显示屏双边行集成电路驱动。表格1记录着电路的设计参数,其中输入级包括T1,T2,T3,T4,T5,T6和T7尺寸制作相对较小。输出级T8和T9,T10和T11需要满足驱动阵列的需求,因此制作尺寸较大。电容C1在充电阶段,存储电荷不被泄漏,维持高电平;在信号输出时,起到电容耦合效应,Q点电压跳变的更高,使得输出级晶体管完全打开,实现全摆幅输出。电容C2作用是维持QB点在Q点电压跳变时,不受到耦合作用的影响。

图2 行集成驱动电路的光学显微图Fig.2 Micrograph of the proposed gate driver circuit

我们采用安捷伦的B1500半导体测试仪的SPGU模块进行对电路性能的测试,测试中, CLK1和CLK2的低电平和VSSL相等,CLK3, CLK4,CLK5和CLK6的低电平和VSS相等,实验测试的RC负载分别为10 kΩ和14 p F。

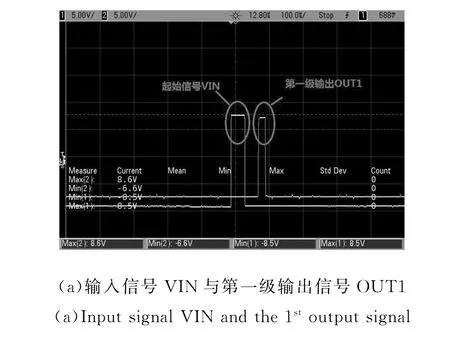

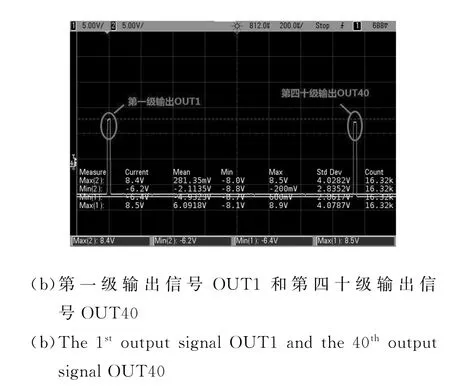

图3为该行集成驱动电路的测试结果,图3 (a)所示的行集成电路的起始信号VIN和第一级输出波形OUT1。从波形的峰峰值可以观察到,起始信号VIN峰峰值与CLK1和CLK2一样,输出波形OUT1的峰峰值与CLK3,CLK4,CLK5, CLK6一样。起始信号VIN的脉冲宽度为第一级输出信号OUT1的两倍宽,从前面分析结论可得,该电路的动态功耗是传统结构电路的1/2。图3(b)显示了输出级的输出信号,第1级输出信号OUT1和第40级输出信号OUT40,OUT1和OUT40的峰峰值相等,脉冲宽度一样,从实验验证了该电路可以正常工作。

图3 行集成驱动电路测试结果Fig.3 Experiment result of the proposed gate driver circuit

表1 行集成驱动电路的设计参数Tab.1 Design parameters of gate driver circuit

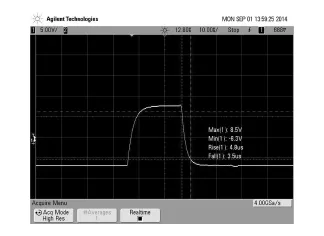

行集成驱动电路的输出能力关系到显示屏显示效果的好坏,我们对该行集成驱动电路做了负载测试,在工作频率50 k Hz,负载10 kΩ和140 p F的条件下,测试出来的输出级的波形,如图4所示,波形上升延迟时间4.8μs,下降时间为3.5μs,总的脉宽时间为20μs,所以在该负载条件下测试,验证了该电路有足够的输出能力,可以集成于显示屏两端,驱动阵列,不会产生串扰现象。

图4 行集成驱动电路输出级负载测试Fig.4 Load test of the proposed gate driver circuit

5 结 论

设计了一种输入级模块复用的行集成驱动电路,采用了一级输入级模块驱动多级输出级模块的结构,可以显著地减少输入级模块TFT的数量,缩减电路面积。该电路的驱动时钟频率是传统结构中一级输入级模块驱动一级输出级模块时钟频率的1/n,有效地降低了电路的动态功耗。我们成功地制作20级的级联行集成电路,20级输入级模块驱动40级输出级模块,该每级的行集成电路尺寸为730μm(宽)×164μm(高)。通过实验表明,电路可以正常工作。在工作频率50 k Hz,负载为10 kΩ和140 p F的条件下,电路的驱动能力满足驱动显示屏的需求。

[1] Choi J W,Kim J I,Kim S H,et al.Highly reliable amorphous silicon gate driver using stable center-offset thinfilm transistors[J].IEEE Trans.Electron Devices,2010,57(9):2330-2334.

[2] Kim B,Ryoo C I,Kim S J,et al.New depletion-mode IGZO TFT shift register[J].IEEE Electron Device Lett.,2011,32(2):158-160.

[3] 严利民,龙云腾,郭丽媛.一种新型的OLED像素补偿驱动电路[J].液晶与显示,2014,29(5):728-732.Yan L M,Long Y T,Guo L Y,A novel OLED pixel compensation driving circuit[J].Chinese Journal of Liquid Crystals and Displays,2014,29(5):728-732.(in Chinese)

[4] ZhengG T,Liu P T,Wu M C,et al.Design of bidirectional and low power consumption gate driver in amorphous silicon technology for TFT-LCD application[J].j.Display Technol.,2013,9(2):91-99.

[5] Lin C L,Tu C D,Wu C E,et al.Low-power gate driver circuit for TFT-LCD application[J].IEEE Trans.Electron Devices,2012,59(5):1410-1415.

[6] Ding Y Y,Si Y J,Lang L Q,An Integrated driving circuitry by employing P-type poly-Si TFTs for AMOLED[J].Chinese Journal of Electron Devices,2008,31(1):77-81.

[7] 徐小丽,刘如,郭小军,等.基于不同TFT技术的AMOLED像素电路仿真分析[J].电子器件,2010,25(4): 565-568.Xu X L,Liu R,Guo X J,et al.Simulation and analysis of AMOLED pixel circuit with different TFT technologies [J].Chinese Journal of Electron Devices,2010,25(4):565-568.(in Chinese)

[8] 曹镛,陶洪,邹建华,等.金属氧化物薄膜晶体管及其在新型显示中的应用[J].华南理工大学学报,2012,40(10): 1-11.Cao Y,Tao H,Zou J H,et al.Metal oxide thin film transistors and their application to novel display technology [J].Journal of South China University of Technology,2012,40(10):1-11.(in Chinese)

[9] Wu W J,Li G M,Xia X H,et al.Low-power bi-side scan driver integrated by IZO TFTs including a clock-controlled inverter[J].IEEE J.Display Technol.,2014,10(7):523-525.

[10] Wu W J,Song X F,Zhang L R,et al.A highly stable biside gate driver integrated by IZO TFTs[J].IEEE Trans.Electronic Devices,2014,61(9):3335-3338.

[11] Hong S J,Kang J S,Lee C H,et al.Low-power and small-sized scan driver using amorphous oxide TFTs[C].SID′2012 Digest,2012:1108-1111.

[12] Kim B,Lee Y U,Han M K,et al.A novel IGZO TFT shift register with node-shared structure[C].SID′2011 Digest,2011:1191-1194.

Nnew In-Zn-O thin film transistors gate driver circuit employing input block multiplex structure

ZHANG LI-rong1,LI Guan-ming2,HUANG Chang-yu3,ZHOU Lei1, LUO Dong-xiang2,XU-Miao2,WU Wei-jing2∗,PENG Jun-biao2

(1.Guangzhou New Vision Opto-Electronic Technology Company,Ltd., Guangzhou 510730,China; 2.State Key Laboratory of Luminescent Materials and Devices, South China University of Technology,Guangzhou 510640,China; 3.School of Electronic and Information Engineering,South China University of Technology, Guangzhou 510640,China)

This paper proposes a new gate driver circuit integrated by IZO-thin film transistors (TFTs),which employs a new driving method called input block multiplex structure.One input blockdriving several output blocks is used in this method,which can reduce the number of TFTs and save the area of the circuit dramatically,satisfying the design of the high resolution and narrow bezel displays.The working time of the input block is n times as the output block,where the parameter‘n’is the quantity of output blocks driven by one input block.Therefore the frequency of the driving clock of the proposed circuit is 1/n of the traditional circuits,in which one input block is used to drive one output block.We have successfully fabricated 20 stages of the circuit.The structure is one input block driving two output blocks and the dimension is 730μm width and 164μm height,which can realize the narrow bezel easily.The experimental results show the circuit can work well and be suitable for 300 PPI displays of AMLCD or AMOLEDs.

In-Zn-O thin-film transistor;integrated gate driver circuit;input block multiplex;output block

TN27

:A

10.3788/YJYXS20153005.0832

1007-2780(2015)05-0832-06

张立荣(1988-),男,广东阳江人,硕士,主要从事TFT集成电路,AMOLED面板设计研究。E-mail:zhanglirong@newvision-cn.com

2015-04-21;

:2015-06-19.

国家自然科学基金(No.61204089);广东省自然科学基金(No.S2012010008648);广东省自然科学基金(No.2014A030310253)

∗通信联系人,E-mail:wuwj@scut.edu.cn