SiC/SiO2复合材料的制备及介电性能研究

2014-12-31刘海涛郑治祥王苏敏祖立成徐光青

刘海涛, 郑治祥, 王苏敏, 祖立成, 吕 珺, 徐光青

(合肥工业大学 材料科学与工程学院,安徽 合肥 230009)

SiC是目前已投入使用的陶瓷基电子封装材料之一,作为封装材料的一部分,基片材料应满足以下性能要求[1-2]:① 高的热导率,保证电子元件不受热破坏;②与芯片(主要与Si和GaAs)相匹配的线膨胀系数,确保芯片不因热应力而失效;③ 良好的高频特性,即低的介电常数和低的介质损耗才能满足高速传输要求。另外,电子封装基片还应具有机械性能高、电绝缘性能好、化学性质稳定及易于加工等特点。当然,在实际应用和大规模工业生产中,价格因素也是不可忽视的一个方面。SiC因其具有低密度、高强度、耐腐蚀、热传导率大及热稳定性好等优点而备受关注。但在高速传输信号的布线电路上,信号延迟时间与基片材料介电常数平方根成正比[2],而SiC因其介电常数高(1MHz下,介电常数为9.7)、绝缘程度低、介电损耗大等原因限制了其中封装基片材料的应用范围,近年来作为基片材料研究的较少。在将SiC用于其他领域的研究中,人们发现,在以SiC为基的材质中加入一定量的BeO,可以较大程度地改善其绝缘性能和介电性能[3]。可见引入第2组元可有效改观SiC使用性能,但BeO是有毒物质,故不宜普及使用[1]。相对于单晶Si材料的芯片来说,SiO2具有较低的热膨胀系数,很低的介电常数(1MHz下,介电常数为3.9)以及良好的电绝缘性能。其中纳米SiO2是极其重要的高科技超微细无机新材料之一,因其粒径很小、比表面积大、表面吸附力强、表面能大、化学纯度高、分散性能好及在热阻、电阻等方面具有特异的性能,在陶瓷、涂料、电子封装、黏结剂等领域有着广泛的应用[4-6]。

本文根据SiC与SiO2的性能比较,选择以SiC微粉和非晶态纳米SiO2作为2种组元,用传统固相法烧结制备了SiC/SiO2复合材料,以期改善其介电性能。目前关于SiC/SiO2复合材料的性能研究多集中在吸波性能、高温抗减摩性能、力学性能及热震性能等[7-9],而关于该复合材料介电性能的报道很少。本研究考察了不同配比下SiC/SiO2复合材料随着温度升高,其烧结密度、显微结构变化等对介电性能的影响,为改善SiC/SiO2复合材料的介电性能提供参考。

1 实 验

1.1 SiC/SiO2 复合材料的制备

试验材料选用工业生产用的α-SiC粉体(平均粒径为1.5μm)、100%非晶态SiO2(50nm)粉体,分别称取原料配成不同质量比的混合粉料,采用无水乙醇作为分散剂,放入氧化铝球磨罐中球磨10h,混料后蒸发多余的酒精,并于100℃下烘干2h,随即制得不同质量比的SiC/SiO2前驱复合粉体,然后直接干压成型,压力为100MPa,压制成φ10mm×2mm的圆片。分别在900、1 000、1 100、1 200℃进行常压烧结,均保温3h。为防止SiC在空气中氧化成SiO2,控制组分配比,烧结在氩气保护下进行。

1.2 性能表征

将所有经不同温度烧结后的圆片用阿基米德法测出其密度,烘干后对其进行表面精磨,用多功能X射线衍射仪分析材料的物相组成,经喷金导电处理后在JSM-6490LV型扫描电镜下观察其表面形貌,并对部分样品进行EDS分析。然后将试样烧渗银浆制得电极,用介电常数测试仪测量室温l MHz下试样的电容量和介质损耗,根据电容量计算出介电常数。

2 结果与讨论

2.1 复合粉体及烧结试样的EDS表征

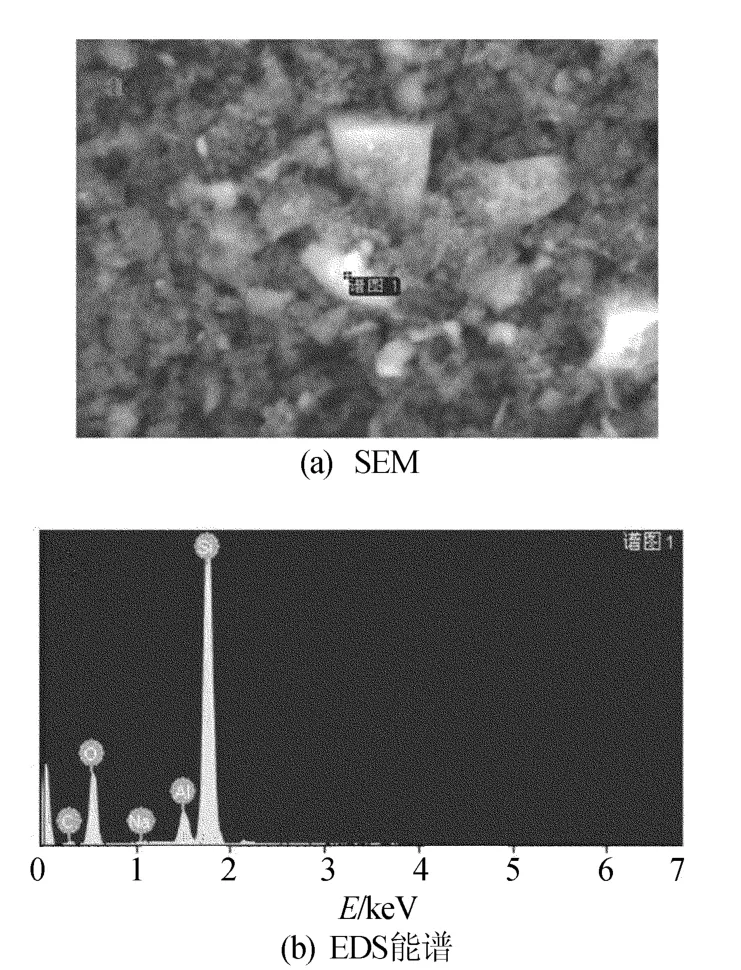

SiC与SiO2质量比为1∶1试样前驱粉的SEM图及能谱分析如图1所示。

图1 质量比为1∶1的前驱粉SEM和EDS能谱图

由图1b可以看出,球磨的复合粉体表面主要成分为SiO2,SiC的质量比很低,而少量Al的存在是因为使用氧化铝球磨罐在球磨过程中引入的;Na可能是SiC原料中含有的少量杂质,因为目前工业制备SiC常见的方法是将石英与焦炭混合,并加入食盐和木屑,置入电炉中,加热到2 000℃左右高温制得的。SiO2占主要成分说明采用球磨方式进行混料时,纳米SiO2吸附在SiC粉体的表面将其包裹住,进而形成了包覆型的SiC/SiO2复合粉体。这种包覆型结构的复合粉体形成的原因应是纳米SiO2比表面积大、表面能大、表面吸附性强的特点所致。

SiC与SiO2质量比为2∶1复合粉体在1 100℃下保温3h后试样的SEM和能谱分析如图2所示。从图2可以看出,除了少量的Al和Na杂质外,烧结试样表面的主要成分依然是SiO2,SiC的含量极低,可见在高温下,这种球磨形成的包覆结构得到了很好的保存。

图2 质量比为2∶1复合粉体SEM和EDS能谱图

2.2 烧结特性

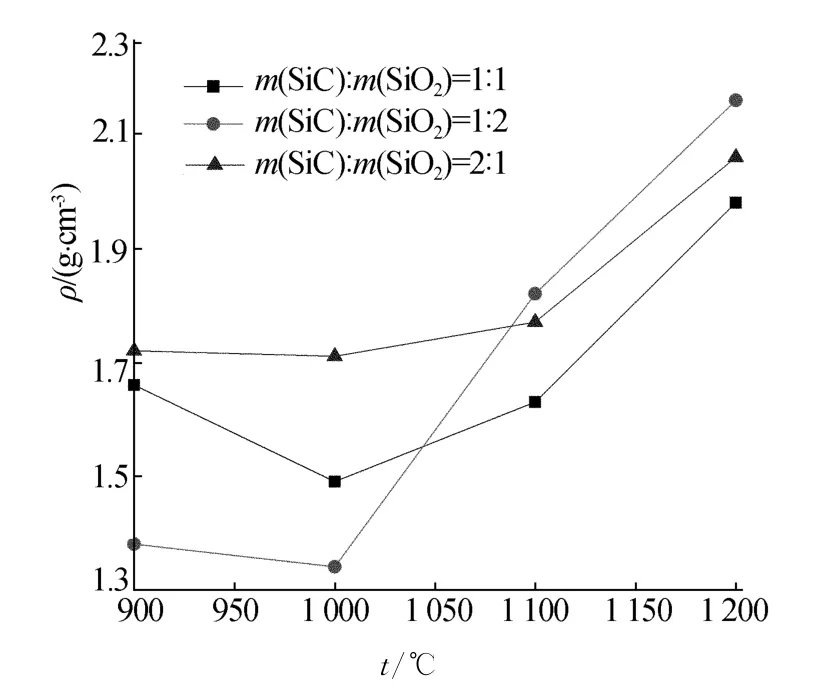

不同质量比的SiC/SiO2复合材料随烧结温度升高,其密度的变化情况如图3所示。

图3 不同质量比复合材料烧结密度随温度的变化

从图3可以看出,3种不同配比的复合材料从900℃升至1 000℃时,烧结密度均有一定程度的下降,在1 000℃后开始逐渐升高。这可能是由于试样在1 000℃以下烧结时,内部的孔隙结构随着温度的升高而膨胀扩大,且此时SiO2玻璃相液化程度较低,流动性差,致使在冷却时样品相对收缩较少,体积总体上增大导致其密度降低。随着温度进一步升高至1 100℃或1 200℃时,试样内的非晶态SiO2玻璃相液化增多,流动性增强,流动的玻璃相填补了孔隙扩张留下的空间,从而使得试样烧结变得越来越致密,密度也逐渐升高。由图3还可以看出,当SiO2的量最多时随着温度升高,其烧结密度也提高得最明显。此外,在温度上升足够高时,非晶态SiO2会开始析晶转化,密度也会随之增加。

2.3 XRD分析

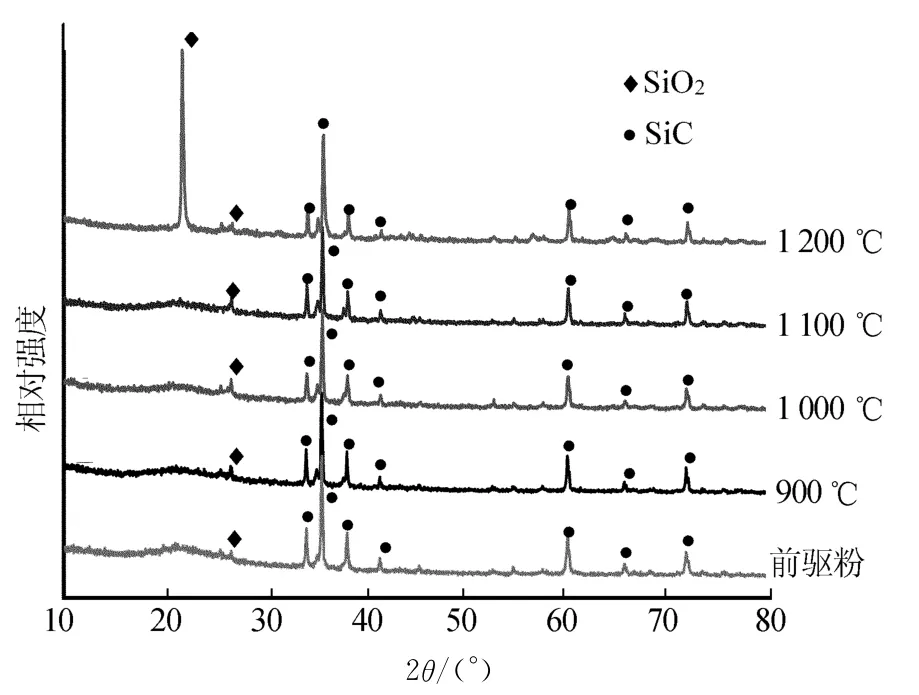

SiC与SiO2质量比为1∶2的前驱粉及不同温度烧结后的复合材料XRD图谱如图4所示。前驱粉XRD图谱上主要衍射峰为SiC峰和SiO2的馒头形状的非晶态峰,但在馒头峰附近2θ=26.639°位置有1个强度很低的衍射峰,且随着烧结温度升高变得尖锐,经分析可知为石英的衍射峰,说明球磨混料的过程中样品有少量的SiO2发生了晶化。这可能是因为纳米SiO2比表面积大,表面活性高,成核势垒低,球磨过程中部分机械能转化为内能而促进了形核。图4中,温度低于1 000℃时,复合材料的主要物相依然由SiO2的非晶相及SiC相所构成,在此温度之下,SiO2没有很明显的析晶转化。当温度上升至1 200℃时,非晶态峰基本消失,表明SiO2在此温度下发生了晶化。

图4 前驱粉及不同温度烧结后的复合材料XRD图谱

2.4 SEM 表征

SiC与SiO2质量比为1∶2试样在不同烧结温度下的SEM如图5所示。由图5可以看出,900℃和1 000℃下试样并无明显的玻璃相液化痕迹,形貌比较松散。而当温度为1 100℃时,可以看出,复合材料内部已有液化冷却后留下的形貌,且整体较为致密。温度至1 200℃时,该现象更为明显,液化的玻璃相流动范围增大,复合材料变得更加致密。

图5 不同烧结温度下质量比为1∶2试样的SEM图

2.5 介电性能分析

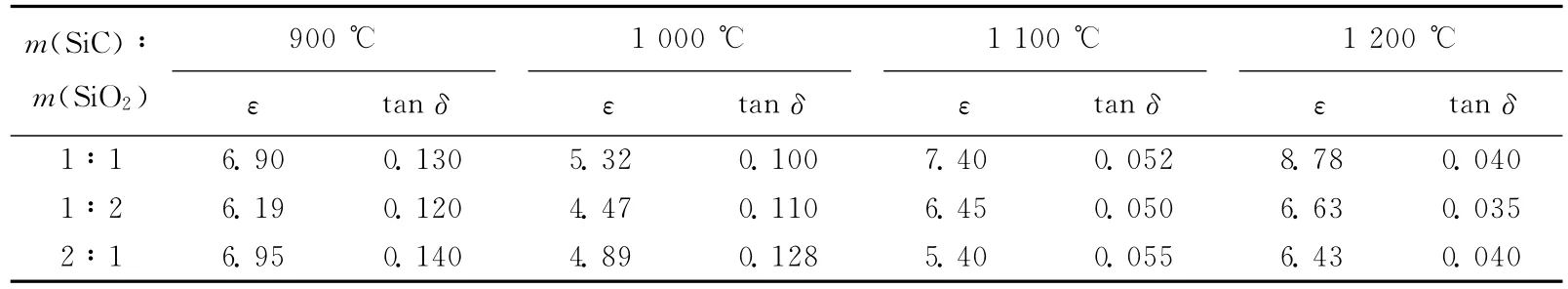

不同质量比的SiC/SiO2复合材料的介电常数ε(1MHz下)和介电损耗tanδ见表1所列,由表1可以看出,所有组分的介电损耗均随着温度的升高而呈现递减趋势,尤其在从1 000℃升至1 100℃时,介电损耗降低了1/2左右,而随后的降低过程趋于缓慢。不同配比复合材料的介电常数与SiC的介电常数(9.7)相比,均有不同程度的下降,且介于SiO2和SiC之间。在900~1 000℃时介电常数下降,1 000℃以上时开始增大,表现出与烧结密度相一致的趋势。SiC与SiO2质量比为1∶2试样在1 000℃下烧结后,介电常数达到了最低,为4.47,此时的密度也降到最低,为1.34g/cm3。这说明试样的烧结密度是影响介电常数的重要因素。当密度较低时,试样中气孔的存在相对较多,而空气的相对介电常数为1,这势必会降低材料的整体介电常数。随着温度的继续升高,样品中玻璃相的液化会越来越多,流动性也会逐渐增强,由XRD图谱可以看出,1 200℃时已有相当部分的SiO2发生析晶转化,这些都会促进样品的致密化。当样品密度较高时,气孔相对减少,介电常数也相应增大。

从理论上来说,随着SiO2质量的增加,由于其优良的介电性能和较低的密度,介电常数应随之减小[10],但由本文结果发现,SiO2质量的增加并没有对材料介电常数的降低起到明显的作用,反而在1 100℃以上烧结时,含SiO2最少的介电常数最低。这可能是因为孔隙对介电常数的影响依然占主要因素。当试样中SiO2质量增多时,在相同的高温下,其玻璃相液化的量比含SiO2量较少的试样要多,进而填补的孔隙也越多,使得烧结越致密,介电常数随之升高。

对于SiC与SiO2质量比为1∶2的试样,在1 000℃时虽获得了最低介电常数4.47,但此时的介电损耗达0.110,SiO2的含量也最大,其较低的烧结密度和相对较少的SiC含量势必会影响其机械强度。而对于SiC与SiO2质量比为2∶1的试样在1 100℃烧结时介电常数为5.40,且介电损耗只有0.055,烧结密度也比1 000℃烧结的质量比为1∶2试样有明显提高,其较高的SiC含量对材料的机械性能也会有明显改善,加之纳米SiO2的生产成本比SiC粉末高出许多,故综合考虑下,当SiC与SiO2质量比为2∶1时用来做封装材料相对较好。

表1 复合材料的介电常数和介电损耗

3 结 论

本文采用简单的机械球磨工艺可以实现将纳米的SiO2包覆在SiC粉体表面,制得包覆型SiC/SiO2复合粉体。采用常压烧结工艺,在氩气的保护下,可制备出介电性能良好的SiC/SiO2复合材料,介电常数均得到明显降低。且当SiC与SiO2质量比为2∶1,烧结温度为1 100℃时,可获得介电常数为5.40,介电损耗为0.055和烧结密度为1.77g/cm3的综合性能较好的复合材料。试样的介电性能与其本身的成分组成、烧结温度、烧结密度以及显微结构等都有着密切的关系。当化学成分配比在一定范围时,孔隙度对材料介电性能的影响起关键作用。孔隙结构越多,材料密度降低,介电常数也降低。

[1] 郝洪顺,付 鹏,巩 丽,等.电子封装陶瓷基片材料研究现状[J].陶瓷,2007(5):24-27.

[2] 张 强,孙东立,武高辉.电子封装基片材料研究进展[J].材料科学与工艺,2000,8(4):66-72.

[3] 李婷婷,彭超群,王日初,等.电子封装陶瓷基片材料的研究进展[J].中国有色金属学报,2010,20(7):1365-1374.

[4] 徐国财,张立德.纳米复合材料[M].北京:化学工业出版社,2002:5-20.

[5] Rao A V,Psjonk G M,Harnath D.Synthesis of hydrophobic aerogels for transparent window insulation applications[J].Materials Science and Technology,2001,17(3):343-348.

[6] 柯 博,黄志杰,左美群,等.纳米SiO2在涂料中的应用[J].涂料工业,1998(12):29-30.

[7] 辛 玲.SiCp/SiO2复合材料制备及吸波性能的研究[D].郑州:郑州大学,1999.

[8] 乔玉林,孟令东,孙晓峰,等.纳米SiC/SiO2复合体系的高温减摩抗磨性能研究[J].稀有金属材料与工程,2009,38(Z2):1018-1020.

[9] 刘 岩,贾德昌,孟庆昌.纳米SiCp/SiO2陶瓷基复合材料的制备和性能研究 [J].宇航材料工艺,2002,32(5):34-37.

[10] 王 涛,张立德.纳米非晶氮化硅的界面极化行为及其机制[J].科学通报,1994,39(11):983-985.