基于AD9911频率源的设计与实现

2014-12-18张震

张 震

(电子科技大学电子工程学院,四川成都 611731)

频率源是通信、雷达、仪器、空间电子设备和电视等电子系统的核心,其性能直接影响电子系统的性能指标[1]。捷变频、低相位噪声、宽频带以及高频率分辨率是频率合成器的研究热点,直接数字频率合成(DDS)正是在这种背景下发展起来的。DDS具有以下优势[2]:在完全数字控制下,DDS可以实现输出信号极小的频率分辨率和相位分辨率,并且具有快捷的切换速度;DDS的数字架构消除了以往模拟频率合成器方案中的手动调整以及与其相关的元件老化和温度漂移;DDS的数字控制接口使得系统可以在处理器的控制下方便地进行远程控制和微小优化;用作正交合成器时,DDS能对I/Q合成输出提供极好的匹配和控制。目前,DDS芯片集成了多种功能,无论用于通信,抑或测试设备和雷达系统,都是理想而灵活的频率合成器解决方案。

文中基于ADI公司的AD9911芯片提出了一种单片机+DDS的频率合成方案,输出频率范围25~75 MHz,频率步进10 kHz,相位噪声优于100 dBc/Hz@10 kHz。

1 AD9911简介

AD9911是ADI公司推出的一款单片DDS芯片,系统时钟频率500 MHz,采用0.35μm CMOS工艺,仅需1.8 V的供电即可输出高达250 MHz的同步正交信号[3]。AD9911内部集成一个DDS主通道和3个副通道、一个10位电流型DAC、一个4~20倍可编程参考时钟倍乘器(PLL)以及多种控制寄存器。AD9911具有单音、多音、Test-tone和多器件同步等工作模式,可完成最高16级的Shift Keying调制,支持频率、相位和幅度线性扫描。AD9911是 ADI公司第一款应用SpurKiller专利技术[4]的 DDS芯片。AD9911的 I/O端口具有4种工作模式且SPI兼容。

2 单片机控制AD9911的具体实现

采用Microchip公司的PIC18LF4520单片机控制AD9911,封装选择适合射频电路使用且节省空间的TQFP-44。PIC18LF4520具有以下优点:宽工作电压(2.0~5.5 V[5])能够符合DDS芯片I/O端口额定电压要求;内部丰富的硬件资源和36个I/O引脚可实现对DDS芯片的灵活控制;最高40 MHz的时钟频率[5]使得系统具有较快的数据处理速度;支持在线串行编程(ICSP)和在线调试,节省了软件设计和调试时间。

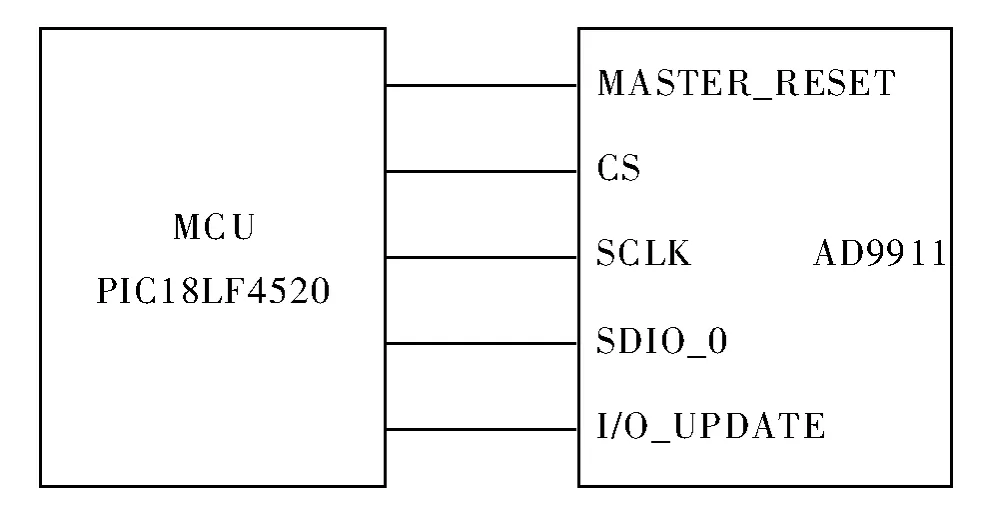

PIC18LF4520与AD9911的外围电路简单,节省了硬件电路设计和调试时间,如图1所示。使用PIC18LF4520的GPIO为AD9911提供控制信号以及模拟两者之间的SPI通信。MASTER_RESET用于复位AD9911,CS为片选信号,SDIO_0是数据传输,SCLK为数据传输控制时钟,I/O_UPDATE为AD9911片内寄存器状态更新使能。系统设计未使用多个AD9911芯片,所以将多器件同步引脚Pin1和Pin2悬空。

图1 MCU与AD9911的硬件连接框图

配置AD9911片内寄存器,AD9911内部共有25个寄存器,地址为0X00~0X18。用户通过配置寄存器的值选择AD9911的工作模式,设置输出信号的频率、相位和幅度等。

首先需要设置系统时钟模式,AD9911外部采用100 MHz恒温晶振输出作为参考信号,使用芯片内PLL将参考信号倍频到500 MHz作为系统时钟,与PLL相关的控制位在寄存器FR1(0X01)。单音工作模式下,需要使能DDS主通道而禁用DDS副通道,相关控制位在寄存器CSR(0X00),I/O端口工作模式也在该寄存器设置。单音模式下频率控制字、相位控制字分别由寄存器CTW0(0X04)和 CPOW0(0X05)控制。CTW0是一个32位的寄存器,当系统时钟频率为500 MHz时,该寄存器可控制频率范围为0~250 MHz,可实现最小分辨率为0.116 Hz。由于对输出信号相位无特殊要求,寄存器CPOW0保持默认值即可。输出信号幅度控制主要在寄存器ACR(0X06)设置,在此也保持默认值。

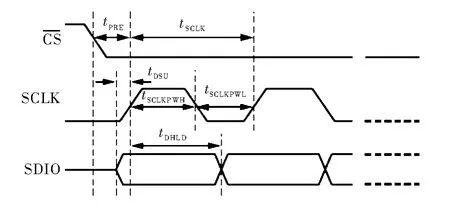

AD9911内部参考时钟输入电路、DAC和DDS主副通道数字逻辑电路可以通过配置相应的控制位分别关断,AD9911将进入低功耗工作模式,相关控制位在寄存器FR1(0X01)和CFR(0X03)。单片机对AD9911进行写操作时,需要注意芯片I/O端口通信的时序要求,如图 2[3]和表 1 所示[3]。在所有写寄存器操作完成后,需要在I/O_UPDATE引脚送入一个高电平以使寄存器内容更新,最小脉冲宽度为系统时钟周期的4 倍[3]。

图2 AD9911串行端口写入时序

表1 I/O端口各状态的建立与保持时间

3 单片机控制AD9911软件设计

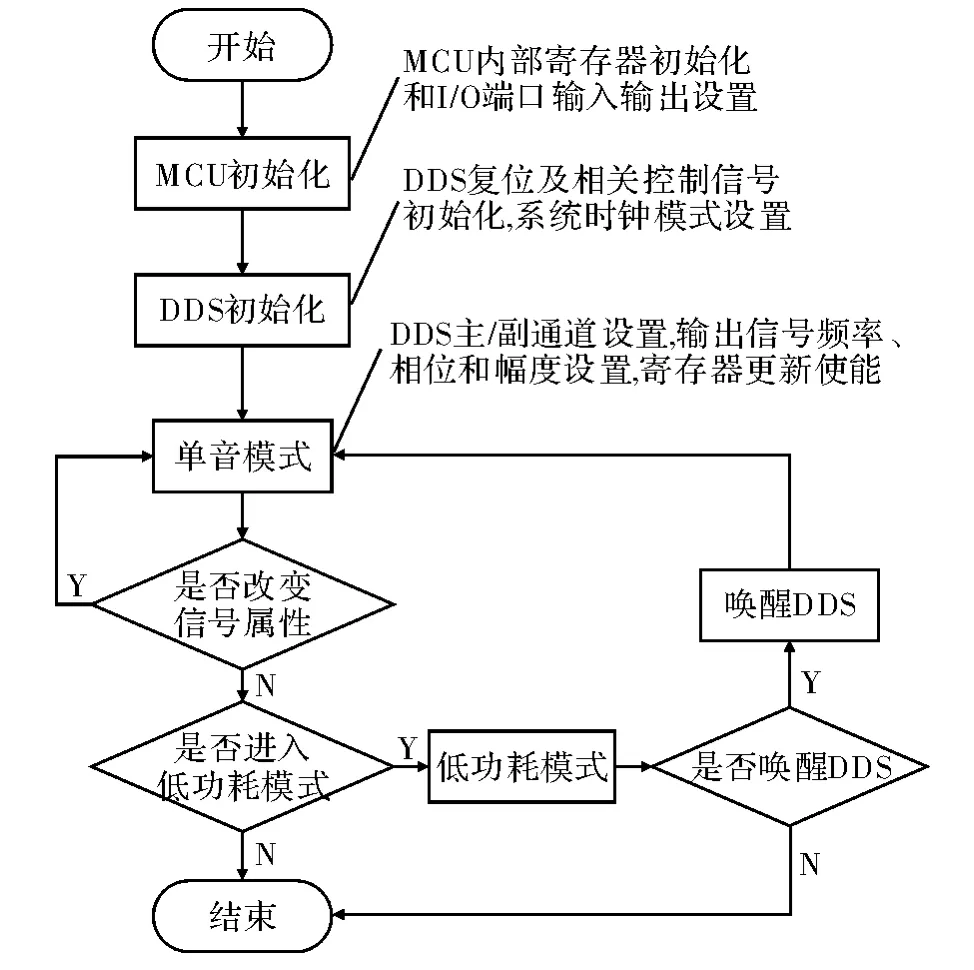

在MPLAB X IDE下建立工程,编译器选择MPLAB C18 C语言编译器,使用PICkit 2编程器对单片机进行编程和在线调试,软件设计流程如图3所示。

图3 软件设计流程

由软件设计流程可以看出,AD9911主要工作在单音模式和低功耗模式。AD9911初始化后,芯片默认进入单音模式并输出一个默认频率信号,AD9911接下来的工作模式由单片机从上位机接收的数据决定。软件设计中的不同功能模块均定义了相关函数来实现,单片机与上位机之间采用UART通信,单片机使用中断处理接收到的数据。

软件设计的重点在于写寄存器函数的编写,即使用PIC18LF4520的GPIO通过软件模拟出SPI串口。如图2所示,串行数据在SCLK上升沿写入,另外单片机和AD9911之间数据通信采用两线模式,CS为片选,所以定义单片机GPIO引脚RC3为串行数据输出SDO,RD0为控制时钟SCLK,RD1为片选信号CS。模拟SPI过程如下:首先拉低CS,在SCLK产生一个上升沿,SDO输出串行数据最高位bit7,然后拉低SCLK,串行数据左移一位,再拉高SCLK,SDO输出串行数据次高位bit6,如此重复8次即完成1 Byte的输出,传输过程中要注意端口状态建立和保持时间。

完成软件模拟SPI端口函数SPISim()后,写寄存器函数的编写采用若干次调用SPISim()的方式完成。单片机与上位机之间通信需要有相关的协议,单片机中断服务程序根据协议对接收的数据进行判断,从而完成相关的操作。本方案中,在拟发送数据前加了一个标志字节,单片机通过判断接收数据的第一个字节而进行相应的操作。

4 DAC重构滤波器设计

使用DDS产生低抖动时钟信号的主要挑战,在于降低DDS输出信号中存在的离散杂散成分所引起的确定性时间抖动[6]。重构滤波器是从DDS产生干净的低抖动时钟信号的重要部件。重构滤波器用于在DAC的输出端衰减镜像频率[7]。通常使用椭圆滤波器作为低通重构滤波器,与其他类型滤波器相比,在给定复杂度的情况下,椭圆滤波器可提供最快的通带至阻带转换。

理论上DDS的频率调谐范围可以从DC到系统时钟频率的一半,然而随着目标输出频率的升高,DDS输出频谱中第一个镜像频率将越来越接近目标频率。在实际操作中,将DDS输出频率限制为小于系统时钟频率的40%[8]。这种做法既充分利用了DDS调谐带宽,又适应了外部滤波要求,降低了重构滤波器的复杂度并节省了成本。因此,设计重构滤波器截止频率为200 MHz。

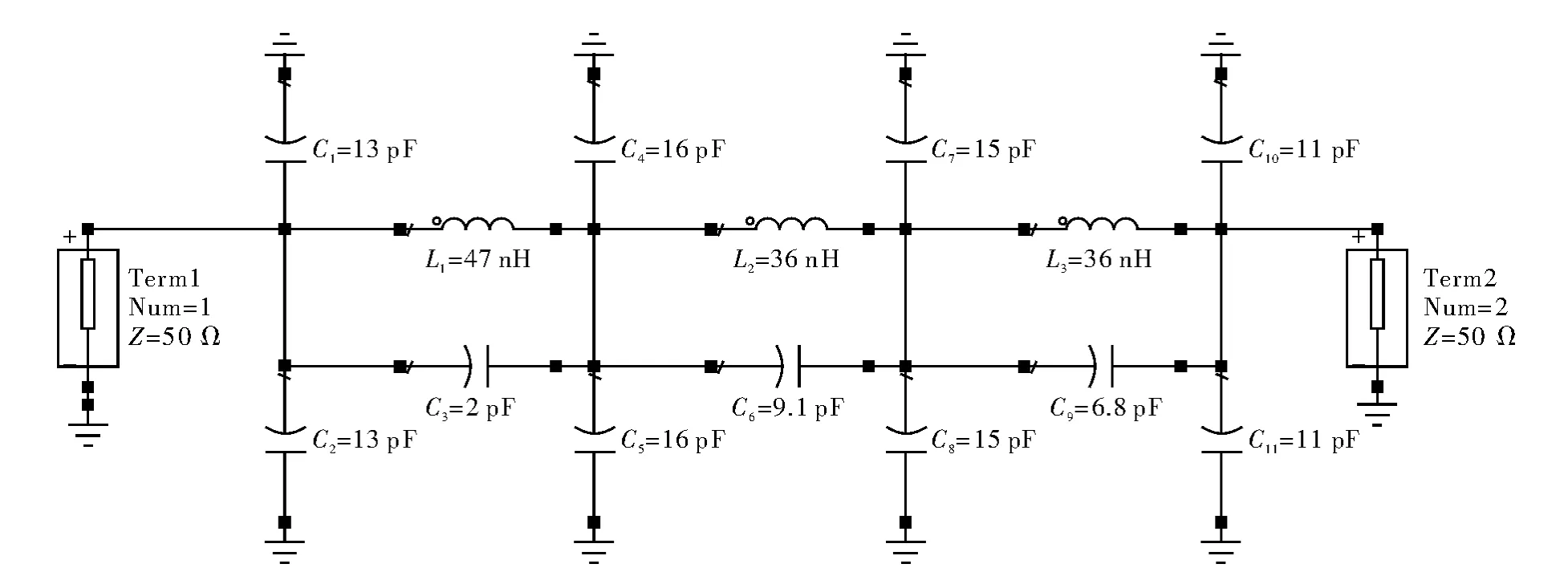

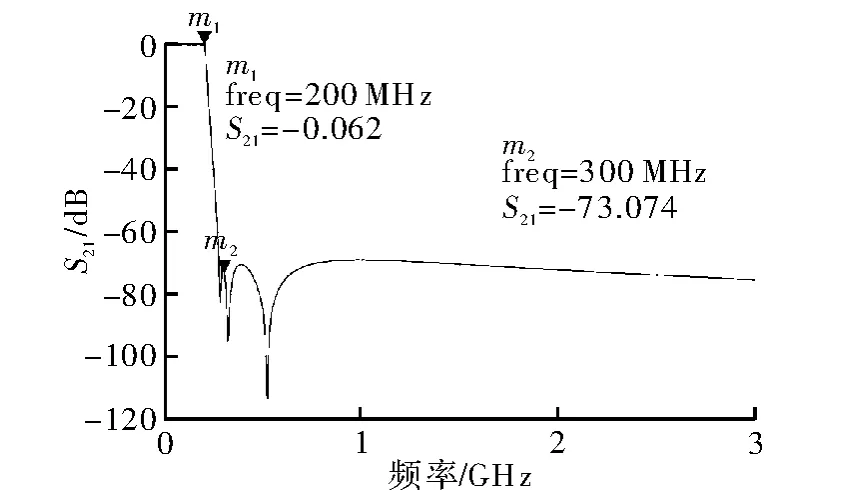

使用ADS软件自带集总参数滤波器设计向导完成椭圆低通滤波器设计,设计指标如下:通带频率200 MHz;阻带频率300 MHz;通带衰减0.5 dB;阻带衰减70 dB;源和负载阻抗均为50Ω。设计出满足指标的7阶椭圆低通滤波器,将设计软件综合出的元件值换为与之最接近的标准值,所得电路原理图如图4所示,仿真结果如图5所示。

图4 DAC重构滤波器电路原理图

图5 DAC重构滤波器仿真结果

如图4所示,S21曲线在200 MHz和300 MHz处的数值分别为-0.062 dB和-73.074 dB,满足设计指标要求。

5 测试结果

系统时钟频率fs=500 MHz,给定输出信号频率fo,则相应的频率控制字FTW可由式(1)计算得到。

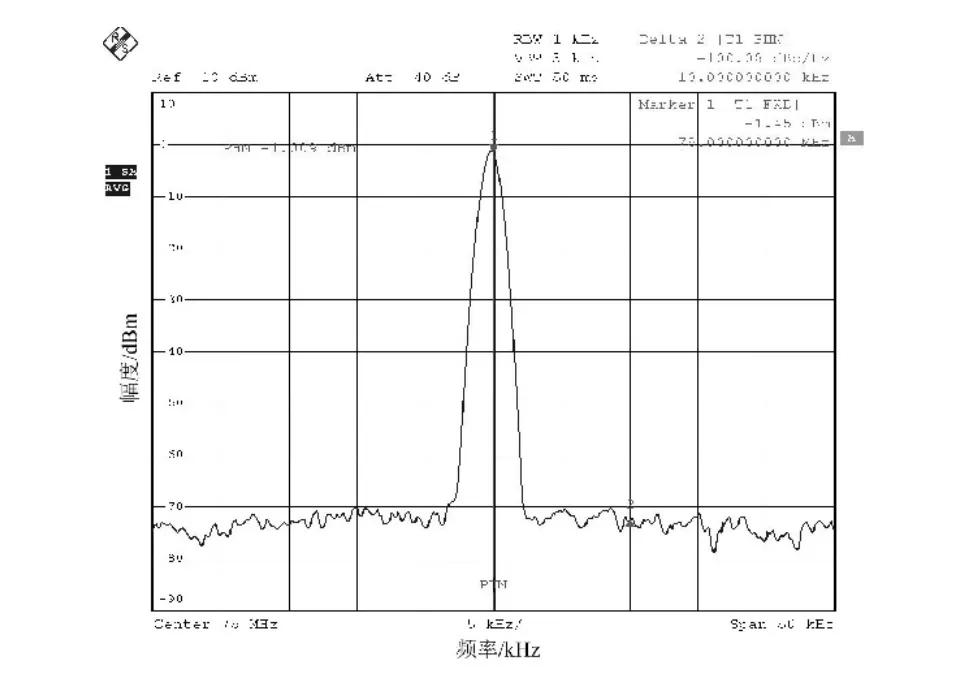

当 fo=75 MHz,FTW=0X26_66_66_66。将 FTW写入寄存器CTW0(0X04),使用罗德与施瓦茨频谱分析仪R&S FSP40实测AD9911输出信号,结果如图6所示。从图中可以看出,输出信号相位噪声达到-100.08 dBc/Hz@10 kHz,且输出信号频率精确。

图6 75 MHz输出信号截图

6 结束语

介绍了基于AD9911的频率源的实现方法,完成了使用PIC单片机控制DDS的频率源。通过利用单片机配置AD9911片内寄存器来实现对DDS芯片的控制,且在AD9911输出端设计重构滤波器以改善信号质量。实测结果表明,该方案输出信号相位噪声小、频率值精确,通过快速配置寄存器即可实现快速频率切换。

[1]Vadim Manassewitsch.Frequency synthesizer theory and design[M].何松柏,宋亚梅,鲍景富,等,译.3 版.北京:电子工业出版社,2008.

[2]Analog Devices,Inc.A technical tutorial on digital signal synthesis[M].USA:Analog Devices,Inc.,1999.

[3]Analog Devices,Inc.AD9911:500 MSPS direct digital synthesizer with 10 - bit DAC datasheet,Rev.0[M].USA:Analog Devices,Inc,2006.

[4]Walt Kester.High speed system applications[M].USA:Analog Devices,Inc,2006.

[5]Microchip Technology Inc.PIC18F2420/2520/4420/4520 datasheet,Rev.E [M].USA:Microchip Technology Inc,2008.

[6]Analog Devices,Inc.AN-823:基于直接数字频率合成器的时钟系统的时间抖动,Rev.0[M].USA:Analog Devices,Inc.,2006.

[7]Analog Devices,Inc.AN -837:基于 DDS的时钟抖动性能与DAC重构滤波器性能的关系,Rev.0[M].USA:Analog Devices,Inc.,2006.

[8]刘抒珍,童子权,任丽军,等.DDS波形合成技术中低通椭圆滤波器的设计[J].哈尔滨理工大学学报,2004,9(5):22-24.