AVS编码器中变换量化和扫描的FPGA设计

2014-12-07杨洪敏王祖强

杨洪敏,王祖强,徐 辉

(山东大学 信息科学与工程学院,山东 济南 250100)

AVS(Audio Video coding Standard)标准是由我国独立制定的具有自主知识产权的视频编码标准[1],采用了与H.264类似的技术框架[2],但其编码效率比国际标准MPEG-2高 2~3倍,与 H.264相当,但存储要求和算法复杂度比H.264低,更便于硬件实现[3]。

变换、量化和扫描在AVS视频编码过程中占有很重要的地位,它是AVS编码中数据处理的中间部分,即将残差数据经过变换、量化和扫描后传到熵编码部分,所以算法的优劣和实现架构对AVS视频编码器的性能有很大的影响。本文为了提高AVS视频编码器的处理速度,结合了国内外学者的设计思想提出了一种变换、量化与扫描模块结构,在消耗逻辑资源允许的情况下提高了处理速度,达到了速度和面积的平衡。

本文以实现1 080i、30 f/s格式视频实时高清编码为目标,结合AVS标准中变换、量化和扫描的特点,设计了一种高速并行流水线结构。通过对整数变换模块内部结构的优化和一维整数变换模块的复用,节省了硬件资源。量化和一维变换模块内部均采用3级流水线处理。扫描模块采用从首尾两端同时开始扫描的方法,完成一个8×8块的扫描仅需要33个时钟周期,节约了扫描的时间。

1 整数变换和扫描算法分析

1.1 整数变换

早期的视频编码标准往往采用浮点DCT来去除视频图像的空间冗余,而浮点变换不适合在数字硬件环境中实现。在实际中,常采用整数近似的DCT代替浮点DCT来编码视频图像,不仅可以保持浮点变换的编码性能,而且能够大大减少计算复杂度。但是整数DCT近似有可能出现编解码器采用不同的DCT和IDCT的情况,这种情况会导致解码图像的误差漂移[1]。为了避免这个问题,AVS采用 8×8的二维整数变换,变换公式如下[1]:

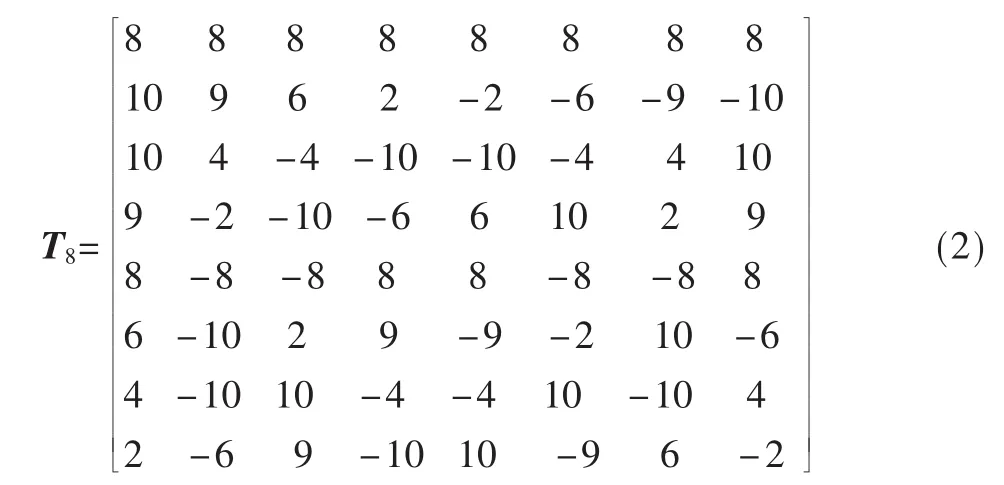

其中,X为残差系数矩阵,T8为 8×8变换矩阵,有:

可见,变换矩阵T8具有奇数行奇对称和偶数行偶对称的特性,这为后文整数变换模块的优化提供了条件。

1.2 扫描

1976年,Tescher在他的自适应变换编码方案中首次提出DCT系数的高效组织方式——Zig-Zag扫描。此扫描方式成为DCT系数高效熵编码前所常用的预处理技术,并一直沿用至今。通常把扫描中遇到的非零系数记为level,一个非零系数前的连续零系数游程记为 run[1]。扫描后的系数被组织成(run,level)对。传统的 Zig-Zag扫描从低频系数开始逐个扫描,扫描一次需要64个时钟周期,如图1所示。

图1 传统Zig-Zag扫描

2 硬件结构

系统工作频率为100 MHz时,实现 AVS高清1 920×1 088、30 f/s格式视频的实时编码,一个宏块的处理时间为4 085 ns,即不超过408个时钟周期,否则就不满足高清编码的要求。

本文提出了一种高效简洁的变换、量化和扫描系统结构,硬件结构及数据流如图2所示。控制模块依据缓存寄存器组的状态产生输入残差数据命令,每个周期读入一列残差数据。残差数据经过变换后送入量化模块进行量化。量化数据保存到缓存寄存器组,由扫描模块控制并进行扫描,扫描模块输出(run,level)对。变换和量化模块内部都采用流水线结构。

图2 整体硬件结构及数据流图

2.1 变换模块

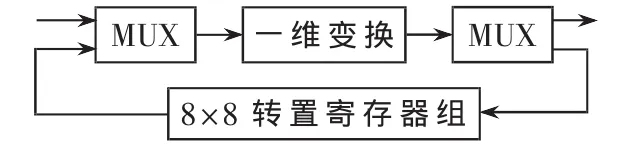

变换模块是将当前块的残差系数矩阵转换为变换系数矩阵的一个过程,其结构框图如图3所示。此设计采用一维变换和转置矩阵实现二维变换,与参考文献[4]中的设计相比节约了硬件资源。参考文献[5]中转置操作由RAM实现,本文中转置操作由8×8的寄存器组实现,避免了访问RAM造成的延时,便于后续的并行流水线处理。参考文献[6]中整数变换采用了蝶形算法,其缺点是需要对变换后的结果进行重排序。参考文献[7]提出了一种快速有效的变换方法,但是资源消耗大。本文对整数变换的方法进行了优化,节约了不必要的硬件资源和时钟。

图3 整数变换结构框图

下面主要介绍一维整数变换过程。设AVS的一维整数变换的输入、输出变量分别为:

根据Y=T8×X,把8个输出元素展开成以下组合,其中 T8为8×8的变换矩阵:

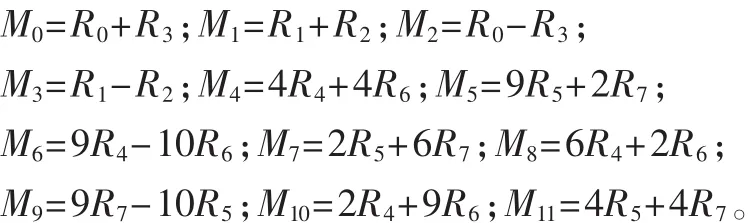

再定义 12个中间变量 M0~M11:

其中所有的乘法均可化为移位操作,重新整理后得到输出:

由以上算法可以看出,一维变换模块只需要移位和加法操作,既方便硬件实现,还节省了硬件资源。经计算,此一维变化模块共需要40个加法器,比参考文献[7]中的一维变换节省了加法器和移位器。

设计中对变换采用流水线的处理方法[7],先进行列变换,然后进行行变换,单步变换为3级流水线结构。变换模块中,第 1时钟周期进行并行读取数据,第 2、3个时钟周期进行一维反变换,第4个时钟周期开始向转置矩阵中存入一维反变换后的数据,第12个时钟周期开始读取转置矩阵中的数据,第14个时钟周期开始输出数据,第21个时钟周期结果输出完毕。

2.2 量化

量化模块采用并行流水线进行设计,每个周期处理一行数据。该模块采用了3级流水线,第一级流水线通过查表得到伸缩参数scalm和量化参数qp_tab;第二级流水线计算 Y=(transcoeff*scalm+218)>>19, 其中,transcoeff为变换系数;第三级流水线计算quantcoeff=(Y*qp_tab+214)>>15,其中,quantcoeff为量化系数。该模块的结构框图如图4所示。

图4 量化模块结构框图

2.3 扫描

经过整数变换和量化后,需要对变换后的系数进行Zig-Zag扫描。传统扫描是将64个系数从首端开始逐个进行扫描,因此传统扫描方法会占用大量的时钟周期,降低了编码的速度,不利于高清实时编码。

图5 改进的Zig-Zag扫描方法示意图

本文改进了传统的Zig-Zag扫描方法,对变换后的系数从首尾两端同时开始扫描,节约了扫描的时间。其实现方法示意图如图5所示。首先,在量化后的系数矩阵的中间插入一个非零常数,然后从该系数矩阵的首尾两端同时开始扫描,一共扫描33个周期。扫描路径1统计非零系数前零的个数run0和非零系数值level0,扫描路径2统计非零系数后零的个数run1和非零系数的值level1,并逐个输(run0,level0)和(run1,level1)。 最后,将第 33个扫描周期输出的run0和run1相加,并将结果赋给run1,即得到插入常数后面的第一个非零系数前零的个数,而插入常数后面的第一个非零系数的值为第33个扫描周期输出的level1。至此扫描完成。

改进的扫描方法完成扫描过程只需要33个时钟周期,比传统的扫描方法节省31个时钟周期。扫描模块的结构框图如图6所示。与传统的扫描方法相比,只增加了一个选择器和加法器,却节约了将近一半的扫描时间。

图6 扫描模块的结构框图

3 仿真综合结果及分析

根据上述思想,采用Verilog HDL语言完成硬件的编写,选用Altera公司的软件Quartus II 11.0和ModelSim 6.6d进行了实现和仿真。部分仿真结果如图7所示。从仿真图中可以看出,本设计中第1~21个周期完成一个块的变换,第 17~24个周期完成量化,第 25~26个周期进行扫描数据的准备,第27~59个周期完成数据的扫描并输出扫描的结果,整个扫描过程只用了33个周期,各个模块输出结果正确,达到了预期的设计要求。本设计完成一个块的变换、量化和扫描需要59个时钟周期,因此,处理一个宏块的时间为236个时钟,满足编码要求。

本设计采用的FPGA为Altera公司的EP2C35F672C6。综合占用的资源如图8所示。由图8可见,使用LE的总数为4 157个。综合布局布线后的结果表明,该结构的最高频率为120 MHz,满足设计的要求。参考文献

图7 仿真结果

图8 综合占用资源图

[1]高文,赵德斌,马思伟.数字视频编码技术原理[M].北京:科学出版社,2010.

[2]李文军,王祖强,徐辉,等.基于 FPGA的 AVS帧内预测电路设计[J].电子技术应用,2013,39(8):50-53.

[3]AVS工作组.信息技术先进音视频编码:视频[M].北京:中国标准出版社,2006.

[4]刘海鹰,张兆杨,沈礼权.基于FPGA的 H.264变换量化的高性能的硬件实现[J].中国图象图形学报,2006,11(11):1636-1639.

[5]黄学超,张卫宁.AVS编码变换量化和扫描硬件设计与实现[J].电气电子教学学报,2011,33(2):34-37.

[6]白玉婷.AVS编码器关键模块的硬件设计[D].太原:太原理工大学,2012.

[7]Wang Leirui,Zhang Zhaoyang,Teng Guowei,et al.Hardware implementation of transform and quantization for AVS encoder[C].ICALP 2008,2008:843-847.