基于wb_conmax的Wishbone二级总线设计与应用

2014-12-07朱秀斌

朱秀斌

(淄博职业学院 电子电气工程系,山东 淄博 255314)

近年来,FPGA器件设计生产制造技术的不断成熟极大地降低了使用FPGA进行产品设计的成本,半导体工艺技术的进步与 EDA(Electronic Design Automation)技术的发展也降低了ASIC(Application Specific Integrated Circuit)设计的门槛,再加上系统设计技术日新月异,使得基于 SoC(System on Chip)原理的 FPGA设计及 ASIC设计如多年前的单片机设计一样在嵌入式系统设计领域得到了广泛的应用。

SoC技术是一种高度集成化、固件化的系统集成技术。使用SoC技术设计系统的核心思想就是把整个应用电子系统全部集成在一个芯片中。SoC的设计过程中,最具特色的就是基于片上总线OCB(On-Chip Bus)的IP(Intellectual Property)复用技术。系统的各个IP模块与其他系统功能模块通过片上总线进行互联通信,因此片上总线的正确选择和合理设计对嵌入式系统应用具有重大的影响。

1 片上总线概述

目前较有影响力的总线标准主要有:IBM公司的CoreConnect总线、ARM公司的 AMBA总线、Silicore公司的Wishbone总线和Altera公司的Avalon总线。这4种总线技术的最大区别在于各自提供的技术特性及其规范的完整性方面的差异。

在这4种总线中,Wishbone总线是唯一一种免费的片上总线标准 并且OpenCores组织选用Wishbone作为片上总线标准,提供了大量的基于Wishbone总线开放IP核。因此,采用Wishbone片上总线进行SoC设计,可以利用大量的免费资源,从而可以节省开发成本,加快系统开发进程。

1.1 Wishbone 总线概述

Wishbone总线规范定义了一种IP核之间互连的通用接口,可用于软核、固核和硬核之间的互连,并且对开发工具和目标硬件没有特殊要求,几乎兼容目前存在的所有主流EDA综合工具,可以用多种硬件描述语言来实现[1]。

Wishbone总线结构比较简单,仅仅定义了一条高速总线,并提供了4种不同的IP互连结构:

(1)点到点(point-to-point):用于两IP核直接互连。

(2)数据流(data flow):用于多个串行IP核之间的数据并发传输。

(3)共享总线(shared bus):多个IP核共享一条总线。

(4)交叉开关(crossbar switch):同时连接多个主从部件,提高系统吞吐量。

点到点互连允许1台主设备与1台从设备相互通信;数据流互联是点到点互联的特例;共享总线互联允许2台及以上的主设备与1台及以上的从设备进行通信,但在任意时刻只能有一对主/从设备相互通信;交叉互联允许多对主/从设备相互通信,数据传输率高。Wishbone总线的4种互联结构如图1所示。

在这4种互连结构中,目前使用较多的是交叉开关结构。在这种结构中,多个主设备可以并行访问从设备。虽然这样会增加硬件逻辑资源,但是在多主设备的系统中能够明显提高系统数据吞吐量。

1.2 应用分析

目前OpenCores组织发布了一些采用交叉互联结构的Wishbone总线IP核,如 wb_conmax、wb_conbus以及针对Openrisc处理器参考平台orp中的tcp_top。大部分的设计者在完成设计时采用了以上的IP,但基于这种结构所设计的SoC系统,所有的主设备与从设备均通过单一总线进行互联。对于低速设备而言,为达到时序设计要求,必须通过硬件逻辑降频处理。但是总线上硬件电路一直工作在高速时钟,从而增加了系统总体功耗。鉴于此,在进行SoC设计时,针对外设速度不同,采用二级Wishbone总线的机制实现IP互联。这样不但可以为系统的后续开发与设计优化提供支持,而且能够方便地扩展与互连更多外设。

图1 Wishbone总线的4种IP互联结构

2 Wishbone二级总线的设计与实现

本文所设计的Wishbone二级总线基于wb_conmax IP核,首先简单介绍wb_conmax核。

2.1 wb_conmax的实现结构

wb_conmax是基于Wishbone总线规范的互连矩阵,采用交叉方式互连结构,可以直接用于基于Wishbone总线规范设计的IP的集成[2]。它主要有以下特点:

(1)最多支持8个主设备;

(2)最多支持16个从设备;

(3)支持 1、2或者4级优先级。

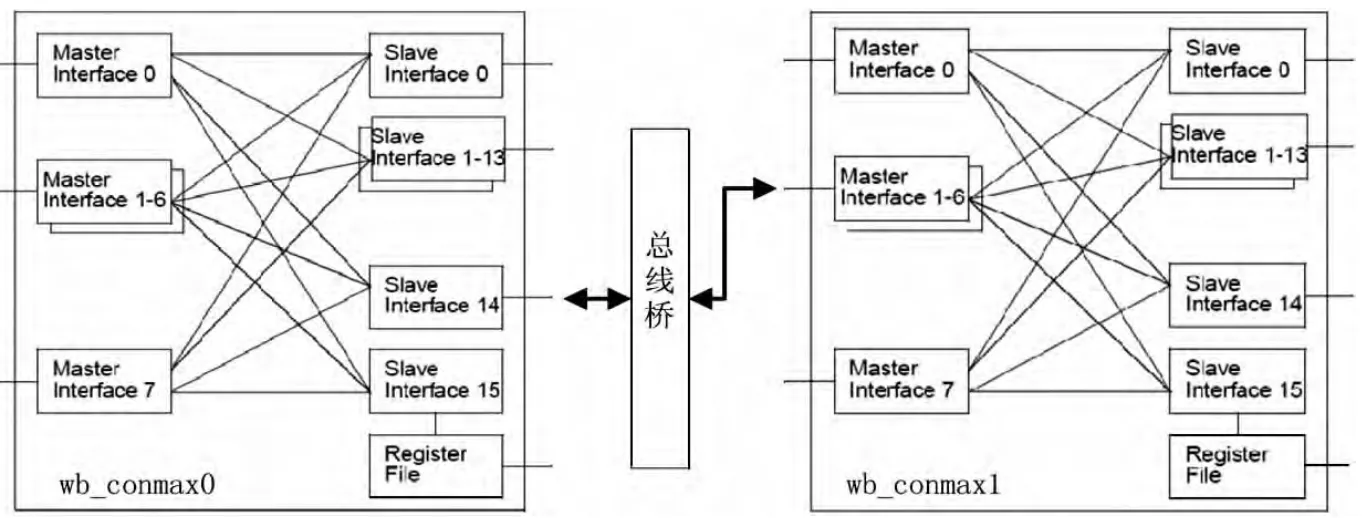

其基本结构可以参考图2。由图可知,wb_conmax为8×16的结构,一般情况下能够满足 SoC系统的要求,而且完全可以实现不同主设备与不同从设备的并行通信。所以该IP在很多设计中得到了应用。

2.2 Wishbone 二级总线的具体实现

本文所设计的Wishbone二级总线基于wb_conmax完成,基本的结构如图2所示。

图2 wishbone二级总线基本结构

在上图结构的具体实现中,wb_conmax0直接采用OpenCores上提供的wb_conmax,地址空间的分配足以满足常用的SoC系统的各种地址空间的分配。wb_conmax1在wb_conmax0的基础上对地址译码部分做了处理。其中总线桥主要实现wb_conmax0与wb_conmax1之间的数据地址信号的互连与同步处理[3]。

2.2.1 wb_conmax地址空间分配

wb_conmax支持16个Slave设备,默认的地址 空 间 为 0x0000_000,0x1000_0000,0x2000_0000…0xf000_0000,每个Slave设备的地址空间高达256 MB。在一般的嵌入式系统设计中,不管对于寻址空间比较大的SDRAM还是Flash,均能够满足设计要求。因此,在本系统中,将二级总线的寻址空间定义在256 MB范围内。

2.2.2 总线桥的设计

对于Wishbone二级总线设计的具体应用,因为与之进行互联的设备均采用标准Wishbone总线的信号,而不像AMBA中有AHB与APB之分,所以总线桥的设计中不涉及总线信号转换问题,主要实现地址编码的实现与不同时钟域信号的同步操作。

(1)总线桥中的地址编码

wb_conmax1的地址独立于wb_conmax进行编码,为了设计的方便与满足系统应用,在这里简单地将wb_conmax1的相对地址分配为0x0000_0000,0x0100_0000,0x0200_0000,0x0300_000…0x0f00_0000。 每个 Slave设备可分配的地址空间为16 MB,这在嵌入式系统的低速外设寻址中基本都可以满足。由图2所示的总线桥进行连接。如果接在wb_conmax0的slave14上,则实际系统中低速外设的访问地址为0xe000_0000,0xe100_0000,0xe200_000,0xe300_0000…0xef00_0000。

(2)总线桥中的同步逻辑设计

在Wishbone二级总线的设计中,两级总线工作在不同时钟频率下,以满足不同设备应用的需求,所以在总线桥中必须做好同步逻辑的设计。对于一些数据量比较大或者突发传输的操作,同步逻辑设计常采用FIFO来实现;而对于其他数据量比较小的传输,多采用简单的双D触发器寄存并由响应信号等待机制进行实现。

在本设计中,第二级总线的工作频率只是第一级总线工作频率的偶数分频,所以同步逻辑采用响应信号的等待机制。一般情况下,在多级总线系统中,高速总线与低速总线的工作频率常为4倍或者2倍的关系[4]。考虑到二级总线所连接外设的工作频率,总线桥将两级总线工作频率定为4:1的关系。对于响应等待信号的处理,通过判断硬件计数器的相应位实现。

3 基于二级总线结构的最小SoC系统应用分析

本文以Wishbone总线接口的开源微处理器AEMB[5]、片上存储on-chip-ram、gpio及UART控制器构成最小SoC系统[6]。SoC系统分别采用单一Wishbone总线与二级Wish-bone总线两种结构进行互联。从SoC系统的外部接口来看,两种结构的SoC系统分别配备两组GPIO及UART控制器。其中采用单一Wishbone总线结构互联的SoC系统结构如图3所示。

图3 基于单一总线结构的SoC系统互联

SoC系统基于二级总线的互联结构,如图4所示。作为分析原型,gpio0与uart0在系统中作为高速设备连接在第一级总线上,对应的gpio1与uart1作为低速外设连接在第二级总线上。其中第一级总线的频率设定为60 MHz,而二级总线频率与之为四分频关系,定为15 MHz。

图4 基于二级总线结构的SoC系统互联

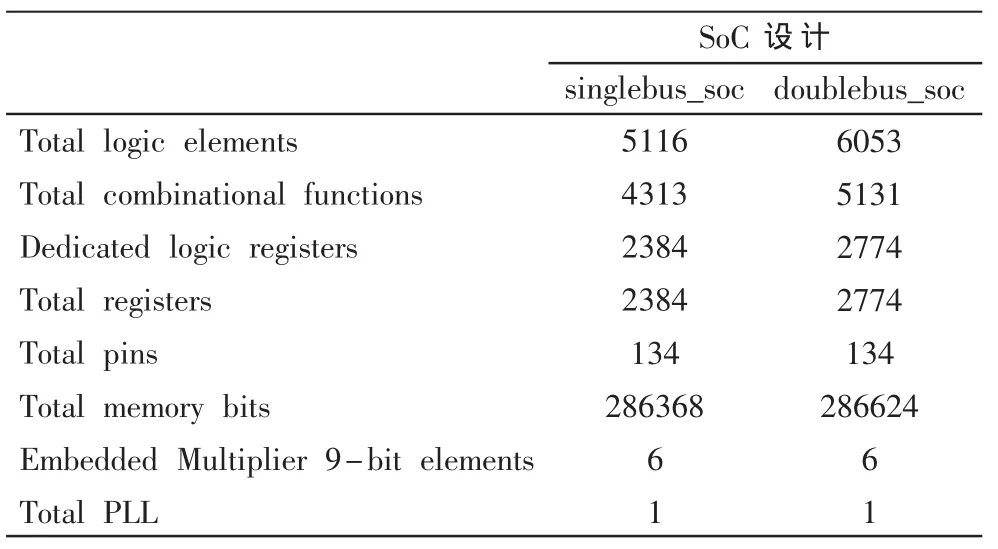

对于上述不同系统结构的SoC系统,基于Altera的EP2C50系列FPGA使用QuartusII进行综合适配得到基于FPGA实现时的资源占用情况报告,如表1所示。

表1 单一总线与二级总线SoC系统的FPGA资源占用

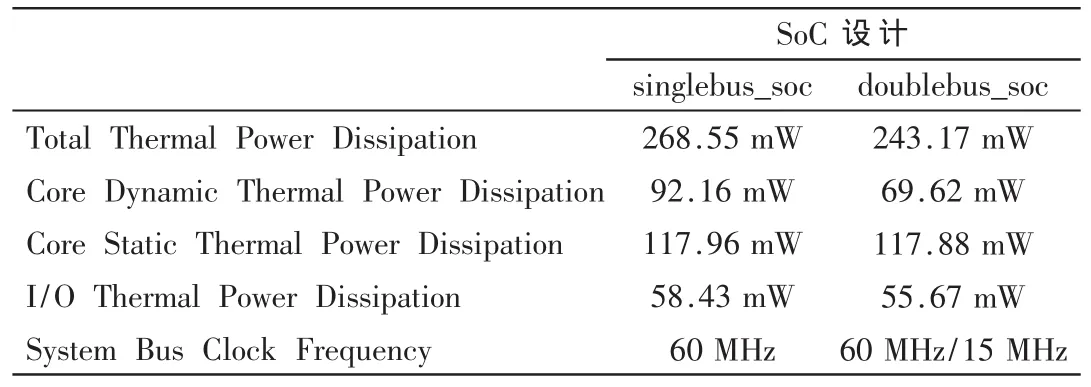

使用QuartusII中所集成的功耗分析工具Powerplay Power Analyzer Tool进行简单的功耗分析。其中singlebus_soc的总线频率为单一的 60 MHz,doublebus_soc的第一级总线频率为60 MHz,第二级总线频率为15 MHz。两种系统结构的简单功耗分析报告如表2所示。

表2 单一总线与二级总线SoC系统的FPGA实现的功耗分析

通过表1所列数据的对比分析可知,相比于单一总线结构,二级总线结构因为总线桥等相关逻辑的使用,使得SoC系统的硬件实现面积有所增加。从表2的数据对比可知,使用二级总线结构的SoC系统的核心动态功耗相比单一总线结构的SoC系统有明显的降低。

本文选用Wishbone总线进行SoC系统设计。通过对Wishbone总线规范的分析,发现了基于Wishbone总线规范进行系统设计互连的局限。针对此,本文提出了基于wb_conmax的二级Wishbone总线设计方法。通过对Wishbone二级总线的扩展,使得在系统设计中可以方便地根据系统IP类型进行划分互连,提高了设计的重用,同时为低功耗要求比较严格的设计提供了优化策略。最后通过搭建简化SoC系统,对基于两种不同总线结构互联实现的SoC系统进行综合与功耗分析,验证了二级总线结构在低功耗设计中应用的可行性。

[1]OpenCores Organization.Wishbone System-on-Chip(SoC)inter connection architecture for portable IP cores[S].Revision:B.3,2002-09-07:4-32.

[2]RUDOLF U.Wishbone interconnect matrix IPcore[S].Rev.1.1 3,2002-10-03:5-12.

[3]宋云扬,罗仁贵,侯立刚,等.片上系统中Wishbone/AMBA AHB总线桥的前端设计[J].电子工程师,2007(33):18-20.

[4]开元海,汪超,郑勇.基于S3C2440与WinCE平台上的FIQ驱动程序的实现[J].微型机与应用,2012,31(24):89-91.

[5]桑圣锋,张德学,于国苹.AEMB软核处理器的SoC系统验证平台[J].单片机与嵌入式系统应用,2010(4):43-45.

[6]鄢永明,刘轶民,曾云,等.基于8051软核的 SOPC系统设计与实现[J].电子技术应用,2005,31(10):72-75.