一种基于DDFS技术的曼彻斯特码时钟提取及解码电路

2014-12-03

(怀化学院 物理与信息工程系,湖南 怀化 418008)

1 引言

曼彻斯特码又称数字双相码,是一种时钟自同步的编码技术.与其它的编码相比,曼彻斯特码可以消除直流成分,具有时钟恢复和抗干扰性能力强的特点,更适合于在传输性能较差的信道中进行信息的传输[1].曼彻斯特码广泛应用于测量[2]、电源通信[3]、车辆信号传输[4]、数据采集[5,6]和物联网RFID[7]等应用领域.

曼彻斯特码编码比较简单,但是时钟提取和解码比较困难,特别是在高速信号传输和噪声较大的应用场合.FPGA 器件的出现能较好的解决现有使用单片机和传统芯片进行编解码码速率低的问题,一定程度上适应中低速应用场合[8-10].但是,由于目前广泛采用的同步是在发生数据信号之前附加额外的同步头技术.这存在两方面的缺陷,一是曼彻斯特码中本身就有时钟信息,额外的同步头会带来信道的负担,特别是在高速数据传输中必须避免;二是同步头技术只能保证在接收帧内数据时钟和同步头的时钟完全一致时才能正确解码,一旦发端的时钟随着时钟出现抖动时,接收端就会由于相位抖动问题而产生错误解码.越来越多的科技人员利用FPGA技术来实现曼彻斯特的解码.本文提出一种利用FPGA 高速并行处理特性和直接数字频率合成技术的曼彻斯特时钟提取和编码器电路,克服曼彻斯特解码电路中需要加同步头和时钟抖动带来的相位模糊问题.

2 曼彻斯特编码器

曼彻斯特码Manchester code (又称裂相码、双相码)是一种用电平跳变来表示1 或0的编码.曼彻斯特编码是一种自同步的编码方式,即时钟同步信号就隐藏在数据波形中:每一位的中间有一跳变,位中间的跳变既作时钟信号,又作数据信号.其编码规则很简单:从高到低跳变表示“1”,从低到高跳变表示“0”.每个码元均用两个不同相位的电平信号表示,也就是一个周期的方波,但0 码和1 码的相位正好相反.

在FPGA 中实现曼彻斯特编码非常方便,只需将数据信号与时钟信号异或即可.

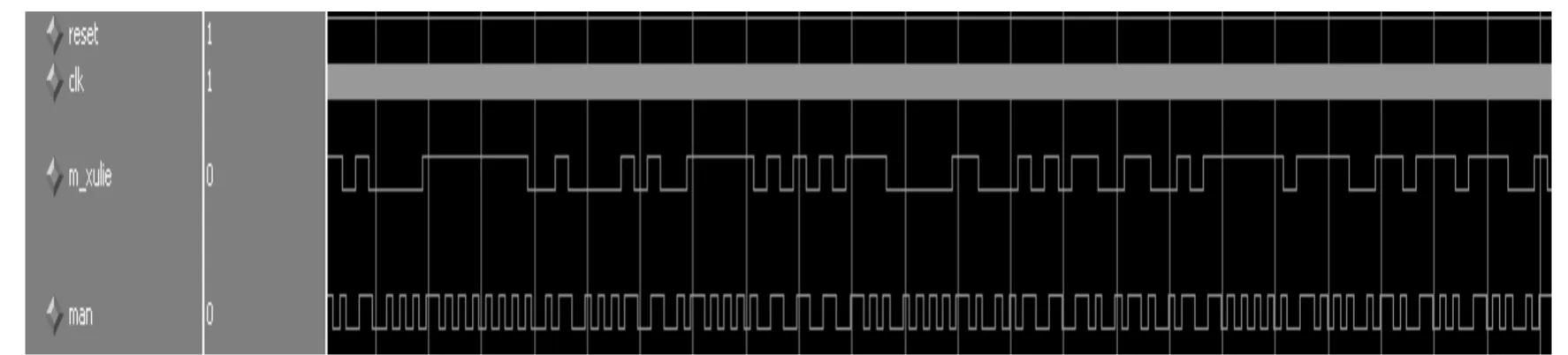

图1 曼切斯特编码仿真图

如图1所示的曼切斯特编码仿真图中,信号m_xulie为8 阶的伪随机序列作为待编码的二进制数据信号,信号man为m_xulie 对应的曼切斯特编码结果.

3 曼彻斯特解码与时钟提取

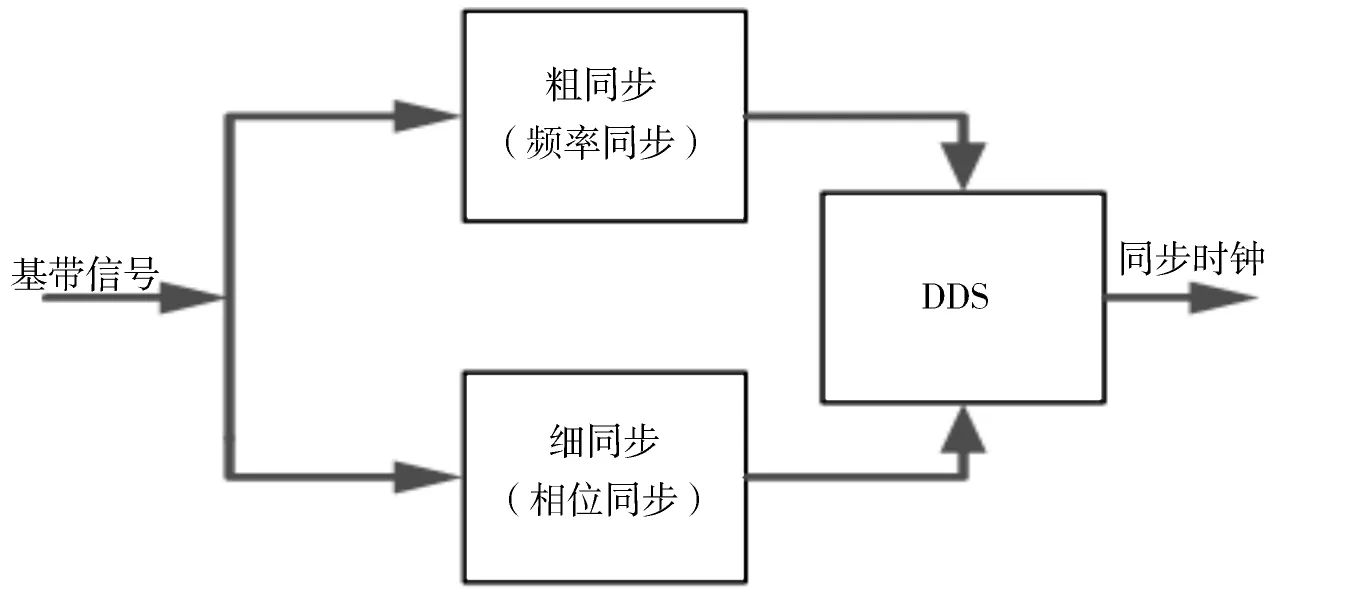

如图2所示,曼彻斯特解码系统主要包括粗同步、细同步和DDS 三个模块.粗同步主要用于从输入的曼彻斯特编码信号中提取同步信号频率,然后将频率控制字给DDS 模块;细同步模块则根据输入的曼彻斯特编码信号进行相位跟踪,并输出相位控制字给DDS 模块;最后,DDS 模块根据粗同步模块的频率控制字和细同步模块的相位控制字输出基带信号的同步信号并实现对曼彻斯特码的解码.

图2 曼彻斯特解码系统框图

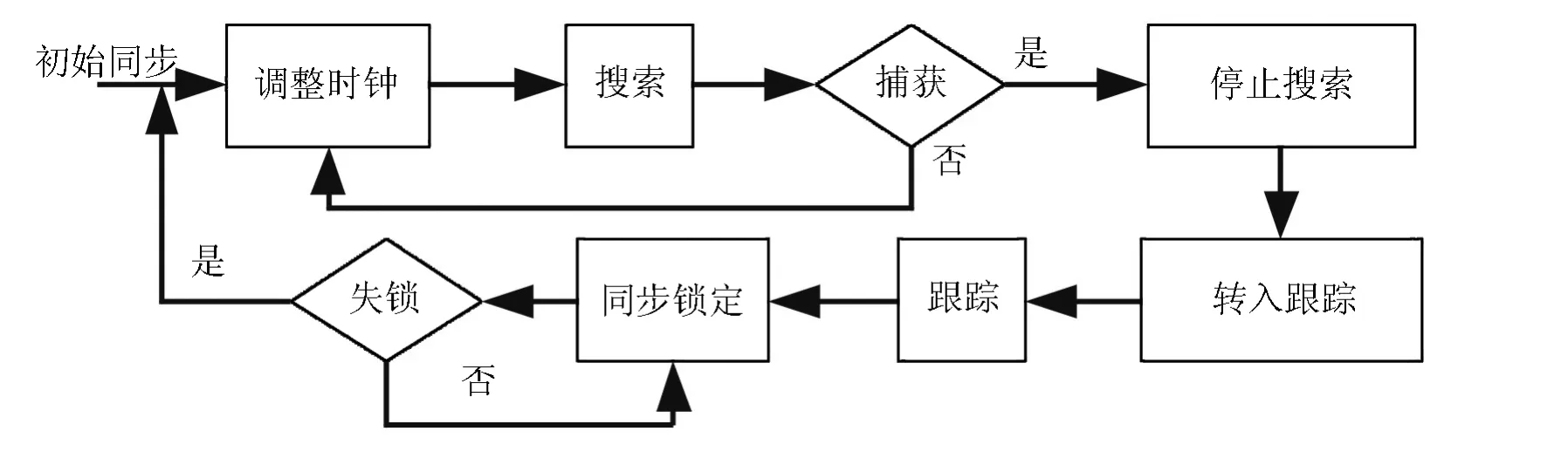

同步信号提取主要由码元速率的周期测量、同步时钟相位跟踪、同步时钟提取和解码几个部分组成,各部分的连接如图3所示.图4为FPGA 硬件建模流程框图.

图3 同步信号提取及解码连接框图

图4 FPGA 硬件建模流程图

码元速率周期测量模块是系统的核心模块之一,其精度决定了整个系统的解码性能.曼切斯特码的码速率为码源速率的两倍,所以只需测出曼切斯特码的编码时钟,即可得到信号的数据时钟.

由于曼彻斯特编码子系统和曼彻斯特解码子系统的时钟是非同源时钟,所以必须通过同步时钟相位跟踪模块来对提取出的同步信号相位进行调整和跟踪.

同步时钟提取模块是通过对同步时间进行多次采样,提取对同步时间采样计数的平均值,以提高系统的抗干扰能力.同步时钟提取模块的功能是产生与发送端一样频率和相位时钟.为了提高精度,这里采用DDFS技术产生同步时钟.

解码模块是曼彻斯特编码的反过程,即将原本的“01”解成‘0’,原来的“10”解成‘1’,从而恢复编码前的数据信息.

3.1 粗同步

粗同步过程,即为同步信号的频率同步过程.通过测曼切斯特码的码元宽度计算出同步信号时钟频率.码元宽度测量是通过码元的上升沿或者下降沿来启动计数器,在码元下降沿或者上升沿到来时停止计数.这样,计数器的值就为码元的宽度.

其中一个需要说明的是如图5所示的边沿检测技术.为了提高同步信号提取子系统的抗干扰性能,将曼切斯特码输入信号当作异步控制信号进行同步.这样,可以在避免亚稳态出现时对曼切斯特码输入信号进行简单的延时滤波,进而有效滤除信号中的毛刺.边沿检测是用于对输入信号或者FPGA 内部逻辑信号的跳变检测,即上升沿或者下降沿的检测.

图5 FPGA 实现的边沿检测电路

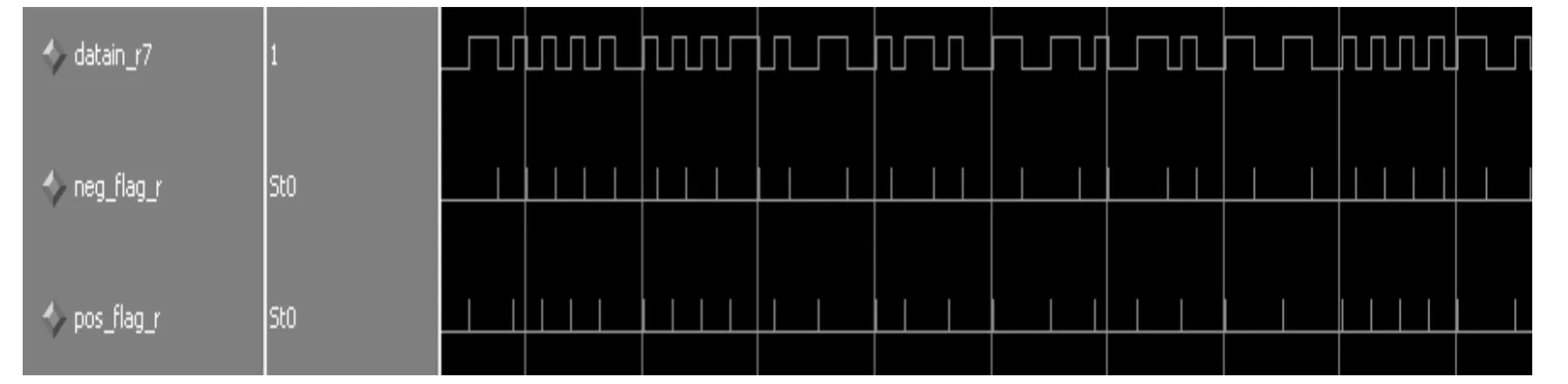

图6 边沿检测电路仿真图

图6是曼切斯特码的边沿检测仿真图,信号datain_r7为曼切斯特码,信号neg flag r为曼切斯特码的下降沿标志信号,信号pos flag r为曼切斯特码的上升沿标志信号.

为了防止因码间串扰造成的码元变形进而导致接收码元宽度与实际发送码元宽度不符合的问题.对每种码速率的码元宽度设定了上下阈值,只要测得码宽在这个阈值里就判定码元宽度为阈值内对应的码元宽度.实验结果表明,这种方法非常有效.即使在噪声很大的情况下,提取的同步信号依然相当稳定,抖动很小,而且误码率也极低.图7为粗同步的模块图.图中的clk为50 MHz的系统主时钟信号,reset为系统复位信号,datain为基带输入信号,dataout为解码输出信号,clk_out为测试信号,dds_addr[31..0]为DDS模块频率控制字,dds_addr1为测试信号,clear为相位跟踪信号.图8为该模块仿真图.

图7 粗同步的模块图

图8 粗同步模块仿真图

3.2 细同步

通过粗同步只能将同步信号的频率计算出来,而同步信号的相位还没有确定.细同步的主要工作为相位跟踪.传统的细同步方法是将码元信号进行微分,然后将微分器输出的信号通过滤波,滤波器输出的信号即为细同步的相位同步信号.设计中为了减轻软件负担,只通过码元的边沿信号来不断的对同步信号进行相位跟踪和调整.产生的相位调整信号连接到DDS相位控制累加器的清零端.

3.3 仿真

为了检测Verilog 描述的硬件电路正确性,搭建了testbench,编写测试激励在modelsim 环境下对设计电路进行软件仿真.图9为曼切斯特译码电路仿真图,图中信号reset为系统复位信号,clk为50MHz 系统时钟.信号m_xulie 8 阶伪随机序列,信号man 伪随机的曼切斯特编码,dataout为解码输出信号,clk_dds_out为信号分析子系统提取的同步时钟,clk v2为曼切斯特编码时钟.从仿真图中可以看出提取出的同步时钟和编码时钟的相位和频率都是一样.从图中可以看出,实现了同步信号的提取.

图9 曼切斯特译码电路仿真图

4 测试结果

(1)曼切斯特编码

如图10所示为用示波器实测的曼彻斯特编码,上面的波形为待编码的m 序列,下面的波形为对应的曼彻斯特编码输出.

图10 m 序列的曼切斯特编码实测图

图11 编码速率为100 KHz 时的同步信号提取

图12 曼切斯特解码测试图

(2)同步信号提取

如图11所示为m 码编码速率为100 KHz 时提取的其曼切斯特编码同步信号.示波器的CH1为提取的同步信号.

(3)曼切斯特解码

如图12所示为曼切斯特解码输出测试图,CH2为输入的m 序列,CH1为经过曼彻斯特解码后输出的m序列,显然解码输出完全正确.

5 结论

本文所提出的曼彻斯特时钟提取和解码电路利用FPGA的并行高速处理特性和准数字锁相技术直接对曼彻斯特编码信号进行时钟提取和解码,克服了传统的外加同步头技术进行同步的效率低下和相位抖动引起的相位模糊问题.解码电路采用DDFS技术,通过粗同步、细同步两个过程分别进行码率测量和相位跟踪锁定.仿真和实验结果表明,该解码电路在信噪比大于2.4 dB 下可以准确的提取时钟和正确解码.电路性能可靠、优良,具有一定的科研和应用价值.

[1]付林,任志平,刘承杰.基于FPGA技术的曼彻斯特编码器设计[J].现代电子技术,2007,256 (17):55-59.

[2]张淑玲,沈田.曼彻斯特编码技术在测井数据传输中的应用研究[J].计算机与数字工程,2009 (9):187-189.

[3]陈焕光,许瑞年,沈天健,等.基于FPGA的Manchester 编解码及快速数字化电源通信的实现[J].核电子学与探测技术,2008 (5):637-639.

[4]江文丹,董昱,薛红岩,等.基于VHDL 语言的多功能车辆总线编码器设计与分析[J].铁路通信信号工程技术,2008 (10):9-12.

[5]刘延飞,程攀攀,郭锁利,等.无线电引信实时数据采集发送模块设计[J].电子技术应用,2012 (7):81-83.

[6]陈志颖.曼彻斯特编码在列控中心数据传输中的研究——解码器设计[J].铁道通信信号,2008 (12):8-10.

[7]周清,蔡明.改进的RFID 混合查询树防碰撞算法[J].计算机工程与设计,2012 (1):209-213.

[8]刘艳,王洪成.曼彻斯特编解码的VHDL 实现[J].微计算机应用,2003 (2):120-120.

[9]林艺文,方展伟.用FPGA 实现曼彻斯特编解码[J].汕头大学学报(自然科学版),2004 (5):63-67.

[10]史敬灼,徐美玉,徐殿国.基于CPLD的Manchester编码器与解码器[J].电气应用,2006 (5):62-64.