基于Gardner位定时同步算法的实验教学设计

2014-11-23欧静兰吴皓威邹玉涛

欧静兰,印 勇,吴皓威,邹玉涛

(重庆大学 a.通信工程学院,国家级电工电子实验教学示范中心;b.飞行器测控与通信教育部重点实验室,重庆 400044)

电子综合设计是高校电子信息类本科专业的一个重要的教学实践环节。重庆大学的电子综合设计持续时间为4周,每4名学生组成一组,每位指导老师一次指导3~4个组。电子综合设计的课题可利用单片机、FPGA或者DSP完成一个特定功能的硬件设备,对培养学生的实践能力、分析和解决问题的能力等都起着非常重要的作用[1]。

笔者结合数字通信的基本原理,设计了基于Gardner位定时同步算法及其FPGA实现的综合设计项目。

1 系统设计方案

同步技术是数字通信系统中的关键技术,同步性能的好坏直接影响数字通信系统的传输质量[2-4]。Gardner位定时同步算法是一种不受载波同步影响的定时误差估计算法,由著名学者F.M.Gardner提出[5-6],该算法无需先验数据信息,并且实际应用中采样速率只需要大于两倍的符号速率,有利于简化设计。

Gardner同步环路的硬件组成包括以下四个部分:定时误差检测器、环路滤波器、控制电路和插值滤波器,如图1所示。对输入信号进行采样,将抽样值送入内插器进行插值运算,内插器的输出则为位定时同步调整后的信号。在反馈回路中,采用定时误差检测算法估计出最佳采样时刻与当前采样时刻直接的偏差值,通过环路滤波器对该插值信号进行高频滤波和去噪处理。环路滤波器输出信号送入控制电路,控制电路产生相应的控制信号对插值器的插入时刻进行调整以便达到定时同步。

图1 Gardner同步环路

1)定时误差检测器。项目采用的Gardner定时误差检测器通常用于同步的二进制基带信号或者BPSK,QPSK和OQPSK信号。该算法每个符号周期计算一次,计算表达式如下:

2)环路滤波器。它的作用是为了有效滤除误差信号中的高频成分,使定时误差更加稳定。这里采用理想积分滤波器实现。

3)控制电路。它由数控振荡器(NCO)和分数间隔计算器组成。NCO主要负责产生溢出时钟,以供插值滤波器使用。

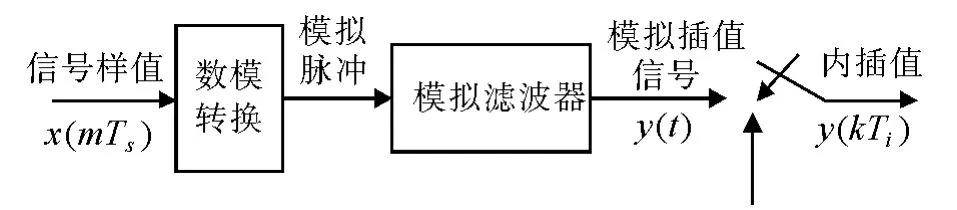

4)插值滤波器。项目采用Gardner插值滤波器[5-6],其速率转换模型如图2所示。插值器的输入信号为采样值x(mTs),输出信号为y(kTi),输出信号周期是Ti的函数。

图2 Gardner插值滤波器速率转换模型

2 算法仿真结果与分析

设计采用Matlab软件随机产生基带信号,并利用自带的调制函数产生一个已调的QPSK信号,同时,利用该信号进行相关的算法验证。其中的仿真参数包括:符号速率为 512 Kbp/s,信噪比(SNR)为60 dB,载波频率为中频140 MHz,模数采样速率为80 MHz。

图3给出了存在加性高斯白噪声(AWGN)和定时相位误差时的QPSK信号星座图。由图可知,在未同步之前,实际采样点与最佳采样点之间存在偏差,信号的星座图分布比较散乱。

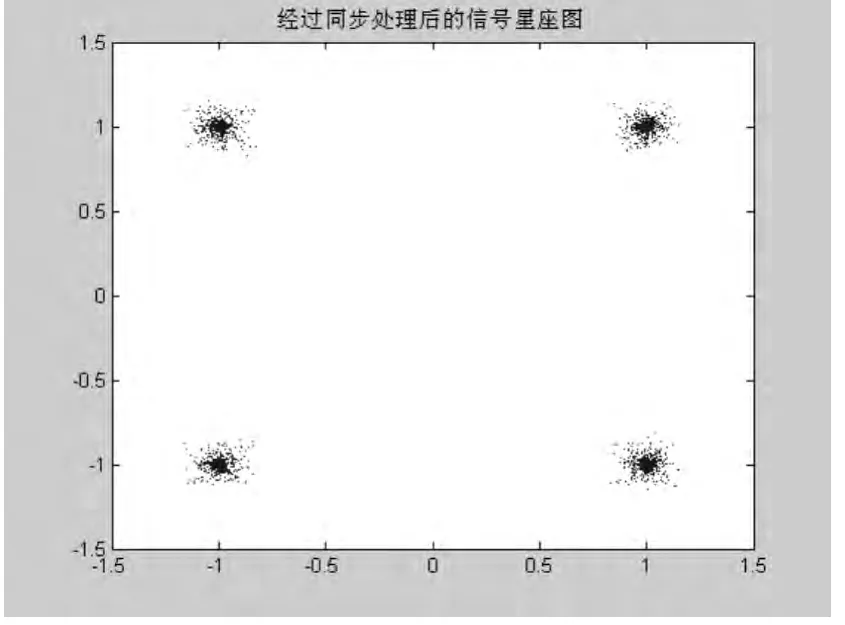

图4展示了经过位同步后的信号星座图,与图3相比,星座图明显比较集中于四个点,即(1,1)、(1,-1)、(-1,1)、(-1,-1)四个点,图中除开这四个点之外的点是在采样未同步之前的。

图3 未进行同步的QPSK信号星座图

图4 经同步后的QPSK信号星座图

3 算法的FPGA实现

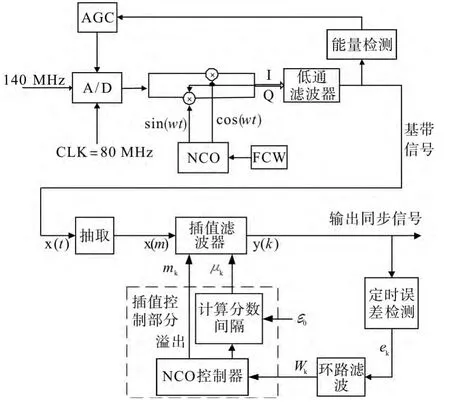

该项目最终在FPGA上实现。根据如图5所示的系统总体设计图,在变频模块中,输入信号频率为140 MHz,模数转换器(A/D)的采样时钟为80 MHz,其中A/D模块是模拟电路,不属于项目的FPGA设计内容。在FPGA软件设计部分,利用频率控制字(FCW)调制NCO产生正弦和余弦信号,对待处理信号作相乘处理,处理后得到的是I、Q两路信号。由于信号比特率为512 Kbp/s,因此,可以利用带宽为1 MHz的低通滤波器同时对I、Q两路信号进行滤波处理。另外,由于这两路信号的能量是不稳定的,需要进行能量检测,利用能量检测的结果控制自动增益控制电路(AGC),以控制A/D器件的增益。变频后的信号进入位同步模块进行后续处理。

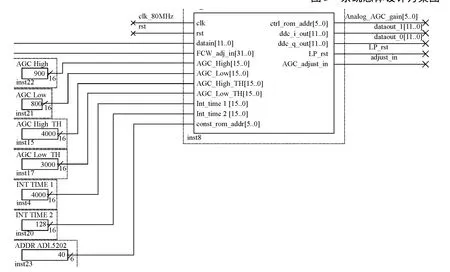

在Quartus II中利用Verilog HDL程序[7]生成的位同步模块如图6所示。关于本设计所使用的FPGA硬件调试平台,考虑到Cyclone系列芯片的低成本和高性能,因此,FPGA芯片采用Cyclone III系列的 EP3C120F780C8,A/D 芯片型号为AD9218。

图5 系统总体设计方案图

图6 位同步模块设计框图

4 结束语

近年来,现代EDA技术发展十分迅速,很多企业和科研院所对能熟练掌握EDA技术的人才需求很大,因此,在高校的电子综合设计中加强EDA设计环节的训练非常必要。本文结合数字通信技术的基本原理,设计了基于Gardner位定时同步算法及其FPGA实现的综合设计项目,对学生的系统设计能力培养起到了积极的作用,收到了很好的教学效果。

[1] 蒋阳,韩庆文,冯文江,等.基于ADμC 812的生理参数测试仪设计与实践[J].实验科学与技术,2012,10(1):10-13.

[2] 樊昌信,詹道庸,徐炳祥,等.通信原理[M].北京:国防工业出版社,1995:349-386.

[3] Proakis J G.数字通信[M].张立军,张宗橙,郑宝玉,等译.北京:电子工业出版社,2001:241-268.

[4] 杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001:197-201.

[5] Gardner F M.Interpolation in digital modems part I:fundamentals[J].IEEE Trans.Comm.1993,41(3):501-507.

[6] Erup L,Gardner F M,Harris R A.Interpolation in digital modems part II:implementation and performance[J].IEEE Trans.Comm.1993,41(6):998-1008.

[7] Sanir Palnitkar.Verilog HDL数字设计与综合[M].夏宇闻,胡燕祥,刁岚松,译.北京:电子工业出版社,2009:40-139.