一种CMOS相机测量系统的设计

2014-11-09陈春宁孙海超

田 睿,陈春宁,邸 男,孙海超

(中国科学院 长春光学精密机械与物理研究所,吉林 长春 130033)

1 引 言

在空间项目中,CMOS图像传感器相对于CCD有许多优势,如功耗小、成本低、供电电压种类少、成像电路集成度高等。尤其是在一些在轨工作时间长的项目中,CMOS图像传感器在抗辐射能力方面的优势更加明显。在E2V公司定制的有增强抗辐射特性的EV76C560AR图像传感器在1280(H)×1024(V)分辨率下最高帧频可达60fps,并且具有低功耗、动态范围大、低光照环境下灵敏度高、控制时序简单的特点。

本文利用EV76C560AR为图像传感器,以FPGA和DSP为图像处理核心设计一种CMOS相机测量系统[1]。

2 系统设计方案

相机测量系统需要完成对合作目标及其背景进行成像,然后对目标相对于相机系统的姿态进行测量运算,最后将图像数据下传到飞行器内的局域网上,姿态测量结果通过1553B总线传输到上一级控制系统。

相机测量系统由2块电路板组成,一块电路板是CMOS传感器板,将CMOS图像传感器EV76C560AR焊接到此电路板上,然后将电路板和前端镜头加以固定;另一块电路板是图像处理板,其上主要器件包括Xilinx公司的V4系列抗辐照FPGA(XQR4VSX55),TI公司的6000系列DSP芯片(SMJ320C6701-SP),Aeroflex公司的SRAM芯片(UT8Q512K32E),Micrel公司的网口PHY芯片(KSZ8041NLJ),DDC公司生产的1553B总线控制芯片(BU-61580S3)。

图1 相机系统原理图Fig.1 Architecture of camera system

FPGA(Field Programmable Gate Arrays)可以进行高速数据处理和逻辑运算。FPGA芯片使用Xilinx公司生产的V4系列的航天级FPGA芯片XQR4VSX55。它具有很好的温度特性和抗辐射的能力,并且有多达640个IO管脚,8个DCM(时钟管理器),最多可以设定的片内RAM达5760Kb,可以满足系统设计要求。SMJ320C6701是TI公司研发的有抗辐照性能的DSP芯片,最大工作时钟频率140MHz,1Mbit的片上RAM,32位数据总线。

图像处理板上的FPGA产生能使CMOS图像传感器能输出24fps的图像的驱动时序,驱动时序经过板间连接器接到CMOS传感器板上;由CMOS图像传感器进行光电转换,将投射到CMOS靶面上的光信息转换成数字图像信号;图像信号再经由板间连接器输入至图像处理板上的FPGA。FPGA将图像数据流分成2个,一个是供DSP芯片进行计算的图像数据流,FPGA将此数据流存储到SRAM中,并且设计有限状态机设置SRAM的工作模式,工作模式包括SRAM完成图像存储、DSP的读取图像数据和DSP写入图像数据。计算结果由FPGA作转换,由1553B总线发送出去。另一个图像数据流为完整的24fps图像数据流,相机系统需要将此数据流通过网口收发芯片PHY下传到飞行器局域网络。

3 图像压缩下传

根据任务需求,相机系统需要将图像数据传输到局域网络供宇航员进行监控。飞行器的局域网络速度设定为百兆,而24fps、8bit、分辨率为1024(H)×1024(V)的图像数据传输的最小带宽要求为192Mb/s。可见由于网络传输带宽的限制不能将原始图像数据从相机系统直接下传。故此,图像数据流需要经过图像处理板中的图像压缩部分进行压缩,将图像压缩成H.264的数字视频压缩格式,再进行下传。

虽然传统DSP架构的顺序执行的压缩算法程序编写比较简单,但是由于航天级DSP芯片运算速度极为有限,并且顺序执行的算法也有很大的局限性导致其难以满足项目中关于实时性的要求。所以,相机系统使用FPGA实现图像数据流的H.264格式的压缩。由于篇幅的关系,使用FPGA图像压缩部分不再详细叙述,其编程原理可参照参考文献[2]和文献[3]。

使用FPGA压缩后图像数据压缩比达50~300倍,带宽需求下降到0.64~3.84Mb/s,可以用百兆局域网下传。在接收端加入H.264解码VC程序,可以实现图像连续播放。

4 SRAM数据操作

DSP的最大工作时钟频率140MHz,考虑到空间系统的频率降额要求,它的工作频率设定到100MHz。可见,DSP的运算速度是相当有限的。上一级控制系统对此相机系统的计算速度要求并不高,125ms左右输出一次测量结果即可,所以DSP只对CMOS成像的数据(24fps,1024 H×1024V)的每三帧抽取一帧进行计算。DSP需要完成的工作有:对合作目标的距离和相对姿态进行六自由度测量;针对图像背景和目标灰度进行分析计算;解析通讯信息;控制CMOS图像传感器的积分时间;最后将计算结果通过1553B总线发送到上级控制系统。

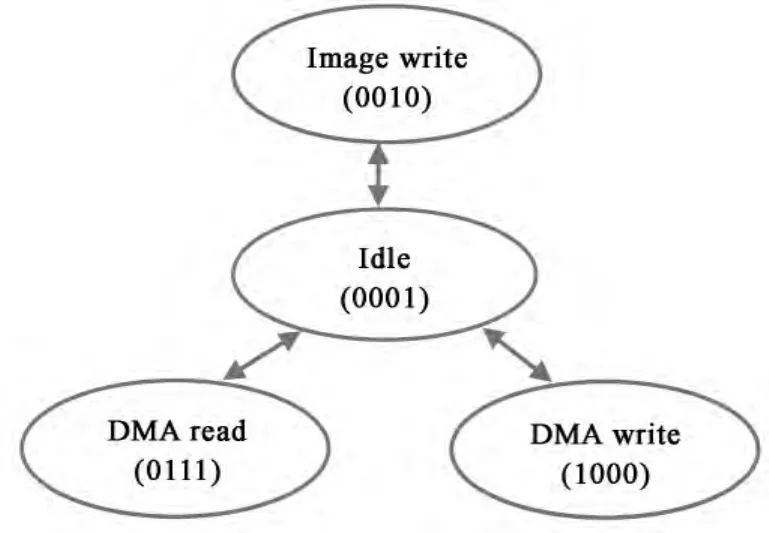

UT8Q512K32E是一款最小读写周期为25ns的32位SRAM,所以将读写频率定在36MHz,这样它的最大数据带宽为144Mb/s。SRAM数据流有3个,分别是8fps的图像数据输入,DSP通过DMA方式读出图像数据和DSP通过DMA方式写入其预处理后的二值图像[4-5]。设定SRAM控制状态机一共有4个运行状态,分别是空闲状态(状态标志码0001B)、图像写入状态(状态标志码0010B)、DMA读图像状态(状态标志码0111B)和DMA写图像状态(状态标志码1000B)。

图2 SRAM控制状态机Fig.2 SRAM control state machine

由于DSP的EMIF总线上只能进行读操作或者写操作,所以在计算系统工作带宽的时候只要考虑一个DMA工作模式即可。如果设定DSP芯片SMJ320C6701-SP在DMA(直接存储器访问)模式下速度为16.7MHz,DSP的数据总线为32bit,所以DSP的数据吞吐带宽为66.8Mb/s。CMOS图像传感器的输出像素时钟为36MHz,如果只取图像数据的高8位参与DSP运算,数据吞吐带宽为36Mb/s。所以,控制SRAM的有限状态机的利用率不能低于(36MHz+66.8 MHz)/144MHz=71.4%。

在一个完整的有限状态机状态转换周期中,最少需要的变换需求时钟周期数包括:状态结束延迟等待时钟周期数T1;状态结束申请信号的持续时钟周期数T2;状态结束申请信号使状态机回到“空闲”状态所需的时钟周期数T3;状态申请信号持续时钟周期数T4;进入状态后设置状态内参数所需时钟周期数T5;状态处理时钟周期数T6。

图3 状态机时序图Fig.3 Timing of state machine

通过编程,本系统中设定各个最小需求周期数T1为2,T2为1,T3为1,T4为1,T5为2,综合上一段对SRAM带宽的分析应有:

公式的意义为,在一个完整的有限状态机状态转换周期中,操作数据读写的时间至少占整个转换周期的71.4%才能保证状态响应的实时性,才能保证数据没有因为状态机没有响应状态申请而发生错误。得到T6应大于17.5,取2的整幂数有利于FPGA逻辑运算和内部FIFO读写判定,这里取32。以状态机主工作时钟为计数基准时,每个状态操作循环中至少有32个周期用来进行SRAM读写操作。

在Modelsim6.5上进行状态机仿真结果如图4所示。

图4 时序仿真结果Fig.4 Timing simulation result

5 1553b总线控制

相机系统作为整个控制系统的一部分,其数据交换通过BU-61580芯片在1553b总线上实现的。相机系统在1553b线上作为一个RT端(远置终端)存在,控制信息通过同级别总线上的BC端(总线控制器)发送到相机系统;相机系统把对合作目标的姿态计算结果传递到同级别的BC端[6-7]。

对BU-61580的寄存器和数据区进行读写需求时间比较长。如BU-61580的输入时钟周期为16MHz,写入一个寄存器或者缓存数据需要用时最少为10个总线周期,时间约为625μs。应用中,每次需要读写的子地址数为30个,每个子地址需要操作32次,一共需要操作的时间为:

使用DSP直接控制BU-61580需要修改DSP的外部总线频率,并且初始化BU-61580和操作BU-61580所需的时间也比较长。使用FPGA控制BU-61580,不但降低了DSP操作外部总线的复杂度,初始化和读写数据的时间也减少了很多,所以使用FPGA作为BU-61580的控制芯片。DSP在每一帧图像计算完成后把数据信号通过DMA方式传递到FPGA,由FPGA完成对BU-61580芯片上数据区的填充。DSP传递数据到FPGA时间为:

所用时间只需要直接操作子地址的二十分之一左右。

在接收BC传递的数据时,FPGA利用消息结束产生的中断读取数据的模式,即FPGA接收到BU-61580芯片的中断管脚INT的低电平脉冲信号后,再对消息进行判定和操作。FPGA读取命令控制字所在的RAM地址中的数据,得到中断的命令控制字。如果这些命令控制字都符合通讯协议中的设定,FPGA根据子地址查找表查找此次操作的子地址所对应的RAM起始地址,最后根据数据字数读取RAM中的数据。最后,DSP根据计算需求定时读取FPGA中的控制信息[8]。

6 结 论

使用V4系列FPGA和C67x系列DSP为图像处理核心设计一种CMOS相机测量系统。在ISE12.4和CCS3.1的开发环境下,使用VHDL和C语言进行编程实现和综合编译,并且用Modelsim6.5对逻辑描述语言做了充分的仿真。在系统资源和器件选用非常有限的情况下完成了相机测量系统设计,此系统已经在初样载荷上使用,可靠性高,成像清晰,姿态数据准确。

[1]贺柏根,刘剑,马天玮.基于 DSP+FPGA的实时图像去雾增强系统设计[J].液晶与显示,2013,28(6):968-972.He B G,Liu J,Ma T W.Real-time image defogging and enhanced system design based on DSP+FPGA [J].Chinese Journal of Liquid Crystal and Displays,2013,28(6):968-972.(in Chinese)

[2]李飞鹏.基于FPGA的H.264视频压缩编码系统研究与实现[D].南京:南京航空航天大学,2012.Li F P.Research and realization of H.264Video compression coding system based on FPGA [D].Nanjing:Nanjing University of Aeronautics and Astronautics,2012,(in Chinese)

[3]荣超群.基于FPGA的 H.264编码系统设计与实现[D].沈阳:东北大学,2013.Rong C Q,Design and implementation of H.264encoding system based on FPGA [D].Shenyang:Northeastern U-niversity,2013,(in Chinese)

[4]王明富,杨世洪,吴钦章.大面阵CCD图像实时显示系统的设计[J].光学精密工程,2010,18(9):2053-2059.Wang M F,Yang S H,Wu Q Z.Design of large-array CCD real-time display system [J].Optics and Precision Engineering,2010,18(9):2053-2059.(in Chinese)

[5]樊博,王延杰,孙宏海,等.FPGA实现高速实时多端口图像处理系统的研究[J].液晶与显示,2013,28(4):620-625.Fan B,Wang Y J,Sun H,et al.High speed real-time multiport image algorithm in FPGA real-time system [J].Chinese Journal of Liquid Crystal and Displays,2013,28(4):620-625.(in Chinese)

[6]尹占芳,曹宇,杨福广,等.基于FPGA的1553B总线终端设计[J].计算机测量与控制,2013,5:1288-1290.Yin Z F,Cao Y,Yang F G,et al.Design of MIL-STD-1553Bterminal based on FPGA [J].Computer Measurement&Control,2013,5:1288-1290.(in Chinese)

[7]李志刚,盖宇.基于FPGA的1553B总线编码解码器的设计[J].计测技术,2006:26:45-48.Li Z G,Gai Y.The design of the manchester II coders and decoders for the 1553Bbus based on FPGA [J].Metrology & Measurement Technology,2006,26 :45-48.(in Chinese)

[8]张飞,王焕玉,徐玉朋等.基于FPGA控制实现的1553B总线通讯设计[J].航天控制,2010,28(6):67-71.Zhang F,Wang H Y,Xu Y P.1553B_Bus communication design based on FPGA control[J].Aerospace Control,2010,28(6):67-71.(in Chinese)