面向混合内存体系结构的模拟器

2014-10-31张进宝廖小飞

刘 东, 张进宝, 廖小飞, 金 海

(华中科技大学 计算机学院,服务计算技术与系统教育部重点实验室,集群与网格计算湖北省重点实验室,武汉430074)

0 引 言

内存是所有计算机系统的关键部件,内存技术的发展近年来面临着新的严峻考验:一方面,多核/众核处理器技术的飞速发展使得系统对大容量、高带宽内存的需求不断增大;另一方面,大数据时代下大量数据密集型应用的涌现也对内存的容量、性能、功耗都提出了新的更高的要求.与此相对,以动态随机存储器(DRAM)为代表的传统内存技术的发展却遇到了瓶颈:受限于制造工艺,在较低的成本上获得更大容量的DRAM内存变得越发困难[1];且随着容量的不断增大,DRAM内存的高能耗问题也日益凸显,内存的能耗在整个系统能耗中的占比非常大,在一些服务器系统中,内存的能耗已经接近甚至超过了处理器的能耗[2-5].

所幸的是,新型非易失性存储(Non-Volatile Memory,NVM)技术的兴起与发展为打破传统DRAM内存这一系统性能与能耗瓶颈提供了契机.以相变存储器(Phase Change Memory,PCM)为代表的非易失性存储器件有着良好地可扩展性,比闪存(Flash Memory),更加接近DRAM的时延与带宽特性,非易失性,以及极低的静态功耗等一系列优良的特性.遗憾的是,它们同样也有着使用寿命短、写时延与功耗过高等一些尚未克服的缺陷.因此,尚不具备利用非易失性存储完全替代DRAM作为主存的技术条件.目前比较通行的做法是利用新型非易失性存储器件与传统DRAM构建混合内存(Hybrid Memory),以期达到充分发挥两者自身优势同时避免各自缺陷这一目的[3-6].

1 相关模拟器

由于目前还没有真实的混合内存物理器件,因此学术界在这一领域的研究工作都是基于模拟器平台来开展的.硬件模拟技术分为局部和全系统模拟两种类型,目前较为常用的模拟内存的局部模拟器有NVMain、DRAMSim2等.NVMain[7]是一个在内存结构层面模拟新型非易失性存储器材的内存模拟器,同时也能模拟传统DRAM的内存结构.DRAMSim2[8]也是一个时钟精确的高度可配置的内存系统模拟器,它针对多种类型的DRAM内存做了详细的时钟模拟,但目前尚不支持非易失性存储模型.NVMain和DRAMSim2既可以作为局部模拟器独立运行,也能集成进其他全系统模拟器作为内存部件模拟内存行为.

较为流行的全系统模拟器包括MARSSx86、gem5等.MARSSx86[9]是一个模拟x86架构的全系统多核模拟器,它在评估系统设计方案以及研究处理器微体系结构方面有着出色的表现.gem5[10]是由 M5[11]和 GEMS[12]紧耦合而成的全系统模拟器,其中 M5提供高度可配置的模拟框架、多种指令集架构和多种CPU模型,gems提供精细灵活的内存系统,包括多种缓存一致性协议和互联模型.

上述全系统模拟器虽然都能比较完整地模拟全系统行为,但均不支持混合内存体系结构;局部硬件模拟器虽然精细灵活,但却不能完整地揭示新型体系结构对系统的全局影响.为了更好地对新型体系结构开展研究,集成使用全系统模拟器和局部硬件模拟器构建新的支持混合内存体系结构的模拟器平台是一个不错的技术思路,选择使用gem5和NVMain构建所需的模拟器平台.两种模拟器的内存时序逻辑严格按照硬件生产厂商所发布的数据表(Data sheet)来设置,且在全系统模拟器gem5上可以运行真实的程序,这就为所构建模拟器的可靠性提供了有力保障.

2 面向混合内存体系结构的模拟器

为了实现gem5模拟器平台对混合内存体系结构的支持,并进一步开展对新型混合内存的研究,在gem5上开展如下工作.

2.1 混合内存体系结构框架

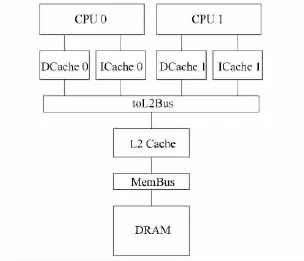

gem5作为一个可以运行原生Linux内核的全系统模拟器,本身可以比较完整地模拟全系统行为,图1所示为gem5可以模拟的原生系统体系结构.CPU0和CPU1分别拥有私有的一级数据缓存和一级指令缓存,两个CPU的一级缓存通过L2Bus总线与共享的二级缓存相连,二级缓存再通过内存总线(Memory Bus)与内存模块相连.其中,可选的内存模块主要是几种传统的DDR动态随机存储器(DDR3、LPDDR3等),gem5缺乏模拟新型非易失性存储器件的功能,且同一时刻有且只能有一种内存模块在工作,亦即原生的gem5模拟器并不支持混合内存体系结构.

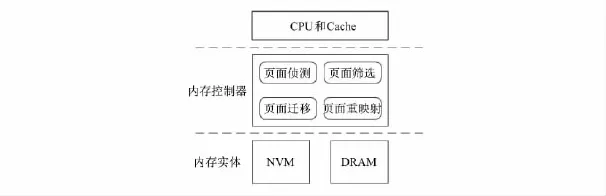

为了扩展gem5的功能,使其支持混合内存体系结构,对其做相应的修改.图2所示为修改后的gem5混合内存系统结构图,即在内存总线和内存模块之间添加一层混合内存控制器(Hybrid Memory Controller)结构,再将DRAM内存模块和新型非易失性内存模块与混合内存控制器相连.DARM模块沿用gem5中的原生模块,NVM模块引入NVMain中的NVM内存模型.

2.2 多种内存混合策略

首先,新型非易失性存储器件的种类繁多,除了前文提到的相变存储器PCM之外,还有阻变存储器RRAM、铁电存储器FeRAM等.为了更好地研究不同非易失性存储与DRAM内存混合所带来的性能与能耗变化,需要构建多种非易失性存储模型作为图2中的NVM与DRAM内存混合使用.

其次,混合内存体系结构中两种不同存储介质之间的结构关系也将对混合内存系统的实验效果产生影响,层次结构[3]和平行结构[5]是两种主流的混合结构,具体到在gem5中的实现,主要的任务就是针对两种结构关系分别设计混合内存控制器,并且要能通过配置文件来选择所需的混合策略.

图1 gem5系统体系结构Fig.1 System structure of gem5

图2 gem5混合内存体系结构Fig.2 System structure of gem5 with hybrid memory

2.3 Cache优化管理机制

高速缓存(Cache)在整个存储体系中占有极其重要的地位,设计精良、管理得当的cache可以极大地弥补慢速主存与高速CPU之间的速度差异,使整个计算机系统获得近乎于cache的访存性能.为了尽可能地减小NVM介质的长读写时延对系统性能带来的不利影响,充分发挥混合内存中传统DRAM的性能优势,需要针对混合内存环境下的cache替换策略进行优化.

(1)cache不命中的性能开销.传统DRAM内存环境下,cache不命中之后的访存行为不管是读操作还是写操作,其性能开销都近乎一致.在混合内存环境下,cache不命中之后的访存行为可分为两类,一类是访问DRAM,一类是访问NVM,它们的性能开销差异很大.此外,跟DRAM内存读写时延近乎一致所不同的是,NVM内存的读时延和写时延也有着数倍的差距[5].

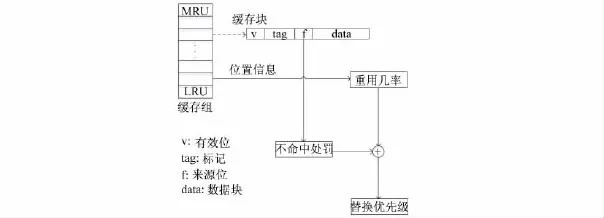

(2)cache替换时victim块的判定.传统DRAM内存环境下,广泛使用的类LRU替换算法根据访存的时空局部性或cache重用距离等因素来选择cache替换时的victim块,根据上一小节的分析讨论,这种判定机制在混合内存环境下并不完全适用,选择victim缓存块时还需要综合考虑cache块的不命中处罚.图3所示为混合内存环境下的cache替换决策机制:一方面,利用类LRU算法中缓存块在缓存组中的位置信息来计算缓存块的重用几率;另一方面,在缓存块中添加来源位以标识缓存块是来自DRAM内存还是NVM内存,并用此来源位信息评估该缓存块的不命中处罚.重用几率与不命中处罚两个因素最终共同决定各缓存块的替换优先级.

图3 混合内存环境下cache替换决策机制Fig.3 Decision-making mechanism of cache replacement in the hybrid memory system

2.4 基于页面热度的页面迁移策略

为了充分发挥非易失性存储器低功耗以及DRAM高性能的优势,在gem5模拟器的混合内存控制器中添加基于页面热度的混合内存页面迁移策略,如图4所示.该策略主要包含如下4部分内容.

(1)页面侦测.在混合内存控制器中添加新的数据结构,利用该数据结构分别记录内存页面在局部时间和全局时间内的读写频次,这些采集到的访存信息将被用来判定页面的冷热.

(2)页面筛选.在混合内存控制器中统计了页面的热度信息,根据这些信息综合考虑局部时间和全局时间,将那些从开始到当前时间写次数多,并且局部时间也被频繁访问的页面定为热页面,将那些一开始就较少访问,并且最近也很少用到的页面定为冷页面.冷热页面划分时,要考虑热页面可能会有局部冷访问时段,而冷页面也会有局部热访问时段.

(3)页面迁移.确定了冷热页面后,计算迁移带来的性能开销和迁移带来的性能提升,选取迁移收益大的页面进行迁移.与此同时,为了充分利用DRAM,根据DRAM的利用率,有保守和激进两种迁移模式,在激进模式下尽最大可能向DRAM空位置迁移,而保守模式下也要从DRAM中换出冷页面到非易失性存储器中.

(4)页面重映射.迁移的页面需要进行重映射来保障程序的正确运行,这就需要在混合内存控制器中维护一个从源页面到目的页面的重映射表.每次迁移都要维护这个重映射表,每次的操作或者是更新表项或者是添加新的条目.

图4 混合内存控制器结构Fig.4 Structure of the hybrid memory controller

3 模拟实验

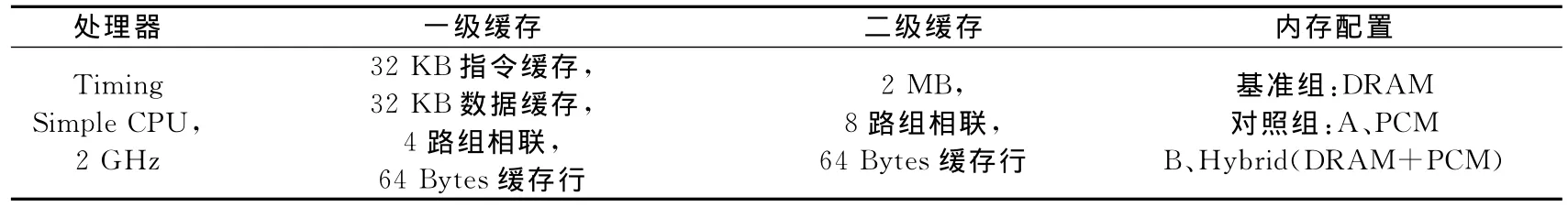

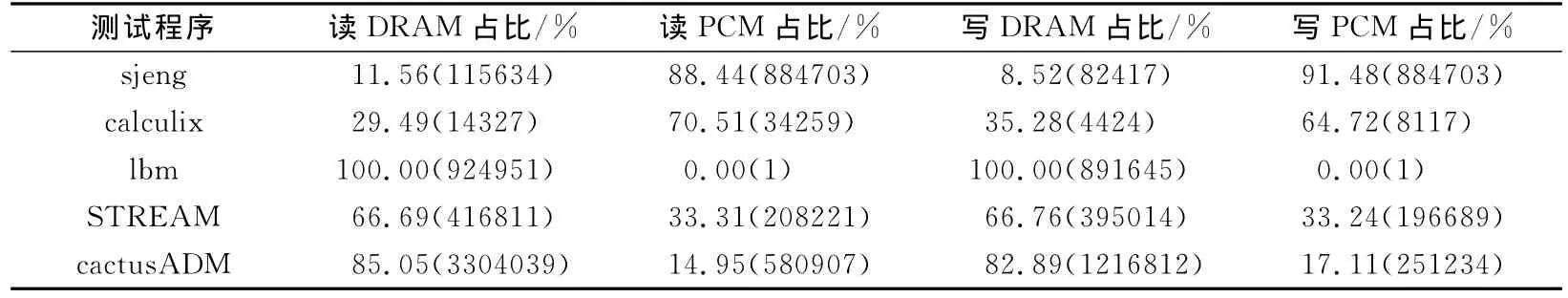

为了证明上述构建混合内存模拟器平台方法的可行性,在gem5上进行对照实验,系统配置参数如表1所示.其中,CPU类型指定参数timing,亦即选定gem5中的Timing Simple CPU,这样相应的访存将根据时序模型模拟运行.设置两级缓存,包括4路组相联的32 KB一级指令缓存和32 KB一级数据缓存以及8路组相联的2 MB二级缓存,两级缓存的缓存行(Cache Line)大小同为64B.

内存配置方面,设一组传统DDR3 SDRAM内存作为基准组,选取变存储器(PCM)以及由以上两种介质构建而成的混合内存作为对照组.所选DDR3 SDRAM和PCM的时延参数如表2所示.总的来说,PCM的读性能虽然比DRAM差,但还算比较接近,而PCM的写性能比DARM的写性能差得多,它们已不在一个数量级[5].

表1 模拟器系统配置Tab.1 System configuration of the simulator

表2 内存时延参数Tab.2 Delay of the memory

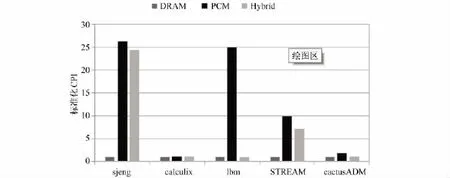

选取SPEC CPU2006基准测试集中的sjeng、calculix、lbm、cactusADM以及专门测试内存性能的STREAM[13]作为测试程序.由于每个测试程序运行时所消耗的内存大小各不相同,针对不同程序所设置的模拟器系统内存大小也并不统一.如表3所示,为了使混合内存环境下程序的访存均匀地分布在两种不同的存储介质上,针对不同程序的内存混合方案也做了精心设计.

表3 测试程序内存配置Tab.3 Memory configuration of the benchmark

模拟器本身即为大型程序,在它上面运行测试程序的速度比在真实物理机上的速度要慢得多,为了将测试程序的运行时间控制在一个可以接受的范围之内,选择手动指定各测试程序在模拟器上运行的指令数而不是将它们全部运行完毕.与此同时,为了尽可能地减小由此而带来的对实验结果准确性的不良影响,亦即尽可能运行较多的指令,我们进行了反复的测试运行,最终确定了如表3所示的各测试程序的模拟运行指令数.特别地,calculix由于程序本身运行较快,其所有指令都运行完毕.

4 实验结果与分析

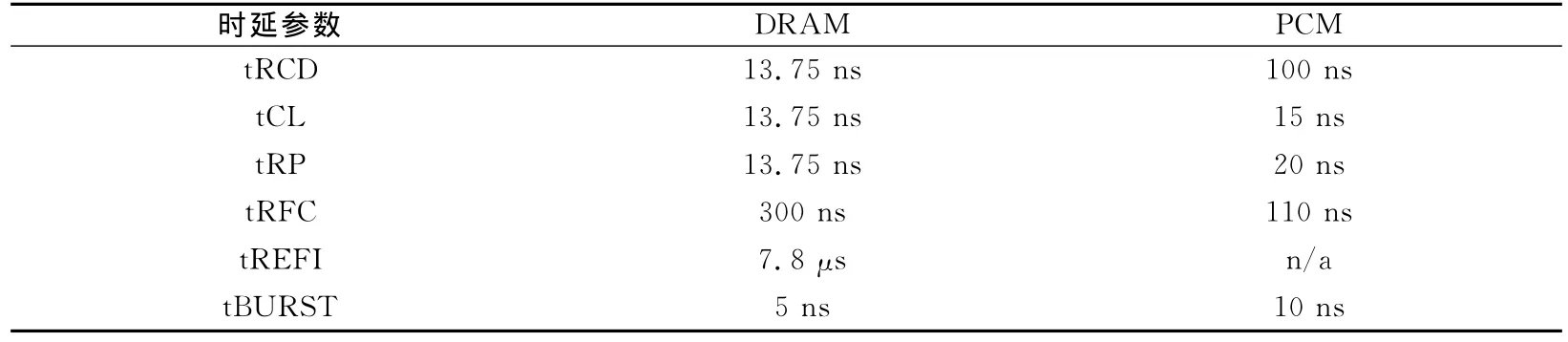

图5所示的是以纯DRAM内存为基准,3种内存环境下运行各测试程序时标准化的系统CPI(Cycles Per Instruction).

图5 不同内存环境下标准化的CPI(以纯DRAM内存为基准)Fig.5 Normalized CPI in different memory systems(Normalized to DRAM)

不难发现,纯DRAM内存的性能最好,混合内存其次,纯PCM内存在性能上表现最差,这完全符合实验预期.5组实验结果的不同之处在于,有的测试程序,如sjeng,在3种不同内存环境下的性能差异很大;而有的测试程序,如calculix,其性能似乎对内存环境并不敏感.通过分析程序访存的统计信息可以很好地解释这一现象.

表4是混合内存环境下测试程序内存读写的分布表,从表中可以清楚地看出,在混合内存环境下,sjeng的内存读、写总量都很大且90%左右的读写操作都发生在PCM中,而PCM的访存性能(尤其是写)比DRAM差,这就导致程序运行时的访存总时延被大大延长,进而导致sjeng运行时系统CPI大幅度提高.calculix对内存环境不敏感的原因是虽然其读写操作大部分发生在低性能的PCM中,但是访存总量小,例如写PCM操作只在千次数量级,而该操作最能影响系统CPI.表4中需要特别说明的是lbm行,并非数据出错,而是其程序本身的访存特性就是如此,绝大部分内存读写操作的位置相对集中,只有极少数的访存行为越过集中内存区域,这也可能跟有限的执行指令数相关.

表4 混合内存环境下测试程序访存分布(括号内为读写次数)Tab.4 Distribution of memory access of the benchmark in the hybrid memory system (between the brackets are memory access counts)

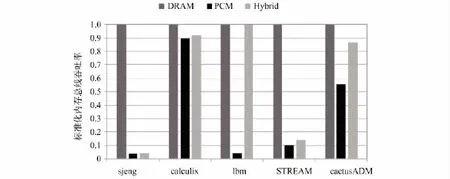

图6所示是不同内存环境下标准化的内存总线吞吐率,依然可以清晰地看出DRAM内存的总线吞吐率最大,Hybrid其次,PCM最低这一趋势.图中形状的差异同样可以从表4中不同测试程序的访存统计信息中分析出结果,在此不再赘述.

图6 不同内存环境下标准化的内存总线吞吐率(以纯DRAM内存为基准)Fig.6 Normalized throughput of the memory bus in different memory systems(Normalized to DRAM)

5 结 论

实验结果与理论预期完全吻合,充分说明了利用gem5和NVMain来构建混合内存系统模拟器是一种可行的技术方案.

众所周知,混合内存是非常有前景的技术领域,新型非易失性存储器件的兴起与发展为提高内存扩展性、降低内存能耗等技术难题的解决带来了新的希望;同时,它也带来了控制混合内存性能损失、延长非易失性存储使用寿命等挑战.现阶段要想开展针对混合内存的研究工作,必须借助于模拟器,因此,一个面向混合内存体系结构的系统模拟器对于相关研究人员来说显得尤为重要.今后,我们将会沿着文中指出的技术路线进一步完善混合内存模拟器平台.

[1] MUTLU O.Memory scaling:A systems architecture perspective[C]//Memory Workshop (IMW),2013 5th IEEE International.IEEE,2013:21-25.

[2] ZHOU P,ZHAO B,YANG J,et al.A durable and energy efficient main memory using phase change memory technology[C]//ACM SIGARCH Computer Architecture News.ACM,2009,37(3):14-23.

[3] QURESHI M K,SRINIVASAN V,RIVERS J A.Scalable high performance main memory system using phasechange memory technology[J].ACM SIGARCH Computer Architecture News,2009,37(3):24-33.

[4] RAMOS L E,GORBATOV E,BIANCHINI R.Page placement in hybrid memory systems[C]//Proceedings of the international conference on Supercomputing.ACM,2011:85-95.

[5] DHIMAN G,AYOUB R,ROSING T.PDRAM:a hybrid PRAM and DRAM main memory system[C]//Proceedings of the 46th Design Automation Conference.ACM,2009:664-669.

[6] MOGUL J C,ARGOLLO E,SHAH M A,et al.Operating System Support for NVM+ DRAM Hybrid Main Memory[C]//HotOS.2009.

[7] POREMBA M,XIE Y.Nvmain:An architectural-level main memory simulator for emerging non-volatile memories[C]//VLSI(ISVLSI),2012 IEEE Computer Society Annual Symposium on.IEEE,2012:392-397.

[8] ROSENFELD P,COOPER-BALIS E,JACOB B.Dramsim2:A cycle accurate memory system simulator[J].Computer Architecture Letters,2011,10(1):16-19.

[9] PATEL A,AFRAM F,CHEN S,et al.MARSS:a full system simulator for multicore x86 CPUs[C]//Proceedings of the 48th Design Automation Conference.ACM,2011:1050-1055.

[10] BINKERT N,BECKMANN B,BLACK G,et al.The gem5 simulator[J].ACM SIGARCH Computer Architecture News,2011,39(2):1-7.

[11] BINKERT N L,DRESLINSKI R G,Hsu L R,et al.The M5 simulator:Modeling networked systems[J].IEEE Micro,2006,26(4):52-60.

[12] MARTIN M M K,SORIN D J,BECKMANN B M,et al.Multifacet's general execution-driven multiprocessor simulator(GEMS)toolset[J].ACM SIGARCH Computer Architecture News,2005,33(4):92-99.

[13] http://www.cs.virginia.edu/stream/.