基于ADV212的无人机实时视频解码系统设计

2014-10-18黄德祥汤爱武潘建兵林仕材胡爱民

黄德祥,汤爱武,徐 升,潘建兵,林仕材,胡爱民

(深圳航天科技创新研究院,深圳 518057)

0 引言

近年来,无人机在抢险救灾、反恐应急、交通巡查与疏导和地质勘探等领域得到广泛应用。无人机采集的实时视频是在上述应用领域中尤为重要的信息。图像的清晰度、实时性、高可靠性与连贯性等性能指标是影响地面人员进行决策的重要因素[1]。JPEG2000由于其压缩算法的特点,能弥补传统视频压缩算法(如H264、MPEG4等)在无线传输上的缺陷[2-5],受到了业界的关注。而由于 JPEG2000压缩算法的复杂性,使得其解压运算复杂、计算量大,对运算设备要求较高,传统采用PC进行软件解压缩或FPGA加专用解码芯片的应用模式很难保证其实时性,并且资源占用率高、功耗大、体积笨重和灵活性差[6],从而限制了JPEG2000压缩标准在无线传输领域的发展与应用,因此研究适合于基于JPEG2000的无人机实时视频图像解压系统具有重大的意义。

本文所述解码系统是手持式一体化测控站的一部分,无线链路系统在小于0.6 Mb/s的有限带宽条件下,传输一路分辨率为720×576,帧率为25 FPS的JPEG2000视频压缩数据,系统要求在保证对无人机的实时控制及遥测数据计算的基础上,视频信号的解码与回放控制在50 ms以内。

基于上述需求,设计了一种基于ADV212的无人机实时视频解压缩系统,运用于无人机手持式一体化测控站当中,使得JPEG2000视频图像的解压缩摆脱对计算设备的高要求,进而实现小型化、轻型化。

1 ADV212

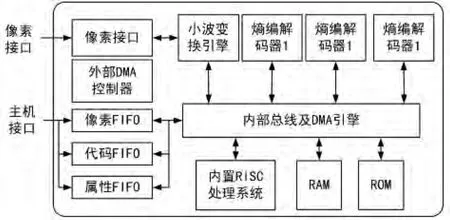

ADV212是 ADI公司推出的一款符合 ISO/IEC15444-1图像压缩标准的单芯片JPEG2000编解码芯片,采用小波变换和自适应算术编解码技术,具有高可靠性、配置灵活、支持多种视频格式和功耗低等特点[7]。

ADV212主要包括1个专门的小波变换引擎、3个熵编解码器、1个片内存储器和1个内置精简指令集(RISC)处理器,如图1所示。

图1 ADV212内部示意

小波变换引擎基于AD公司的SURF专利技术,可实现6级小波变换,在解码模式下,从内部存储器中读取小波变换系数,并通过解码计算,得到编码前的原始数据。熵编解码器用来对小波系数的编码块进行背景建模和算术编码。片内存储器用来存储小波系数数据和临时的代码块特征数据,以及用于RISC处理器的程序和数据存储。RISC处理器用来配置、控制和管理其他专用硬件模块以及分解和产生JPEG2000视频流。内部DMA引擎提供存储器之间的高带宽传输以及各模块和存储器之间的高性能传输[8]。

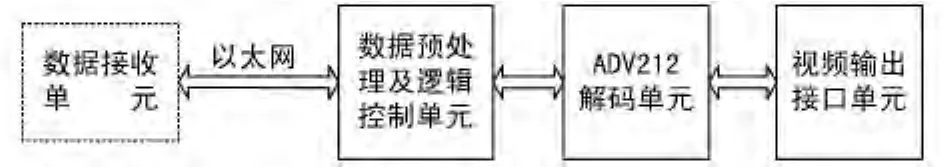

2 系统设计

系统主要由3部分组成:数据预处理及逻辑控制单元、ADV212解码单元及视频输出接口,如图2所示。数据预处理及逻辑控制单元通过以太网口与外部的数据接收单元连接,接收图像数据,解析通信协议得到有效的JPEG2000图像数据,送入ADV212解码单元,并控制ADV212解码单元。ADV212解码单元主要完成JPEG2000图像数据的解压缩工作,输出 BT.656信号。视频输出接口主要把ADV212解码输出的BT.656格式的视频经转换后送入显示器,或者直接接入到其他处理器当中[9]。

图2 JPEG2000解码系统

2.1 硬件设计

本解码系统作为无人机一体化测控站的主要功能子系统,从系统的功能性、易维护性及系统的功耗、体积等方面考虑,采用 32位处理器结合ADV212的方式来实现。

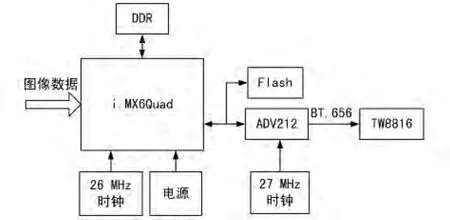

从上述手持式一体化测控站要完成的各种功能的要求,并考虑到性能、温度、功耗及兼容性等方面的设计要求,系统逻辑控制单元选择Freescale公司的i.MX6Quad芯片。这是一款基于ARM Cortex-A9核心的性能强大的低功耗32位4核处理器,主频高达1.2 GHz,内置 1 MB 的 L2 cache,支持浮点运算。i.MX6Quad芯片可直接与DDR SDRAM连接,内置功能强大的图像及视频处理引擎,内置多种接口,如ENET以太网接口和SPI接口等,在满足实时控制无人机及处理遥测数据的基础上,可以实现与ADV212的无缝连接。

由于无人机下传的视频为720×576的JPEG2000视频图像,所以本系统采用一片ADV212解压缩器件,输出的YCbCr数据采取4∶2∶2的格式。为了尽可能地降低功耗,依据ADV212输出BT.656标准的信号,外接27 MHz的有源晶振,输入到ADV212的 MCLK引脚,以供 ADV212内部的JPEG2000处理时钟及内嵌的MCU时钟使用。

C57/BL6小鼠成瘤率为100%。小鼠皮下接种LLC细胞后d10,皮下移植瘤直径长至约6 mm,质硬,活动度差,肿瘤呈膨胀性生长,呈类球形。

系统要求将视频直接显示在屏幕上,故需要将ADV212输出的数据进行转换,以直接显示在LCD面板上。TW8816是一款高集成度的LCD显示接口芯片,其内置8位的MCU及CCFL/LED控制器,支持CVBS、S-Video、YPbPr和RGB等模拟信号以及24位 RGB、8/16/24位 YCbCr数字信号[9]。

如图3所示,i.MX6Quad通过以太网接口与外部无线接收单元连接,通过扩展的16位总线与ADV212连接。i.MX6Quad完成通信协议的解析、图像数据的组帧及存储等任务,并通过16位HOST总线读写ADV212内部的相关寄存器的方式来完成ADV212初始化、代码装载、参数配置以及传递压缩和解压缩数据。

图3 硬件原理

解码工作时,i.MX6Quad通过 HOST接口把JPEG2000数据写入 ADV212的 CODE FIFO中,ADV212内嵌的RISC处理器把JPEG2000数据从CODE FIFO搬动到内部的RAM,待一帧JPEG2000图像数据接收完成后,数据被送入熵编解码器,还原小波系数数据,而后经过小波变换引擎,最后形成YUV图像数据放在PIXEL接口中,图像数据格式配置成BT.656格式,送入TW8816芯片中,视频数据最终在 LCD 面板上输出[10,11]。

2.2 软件设计

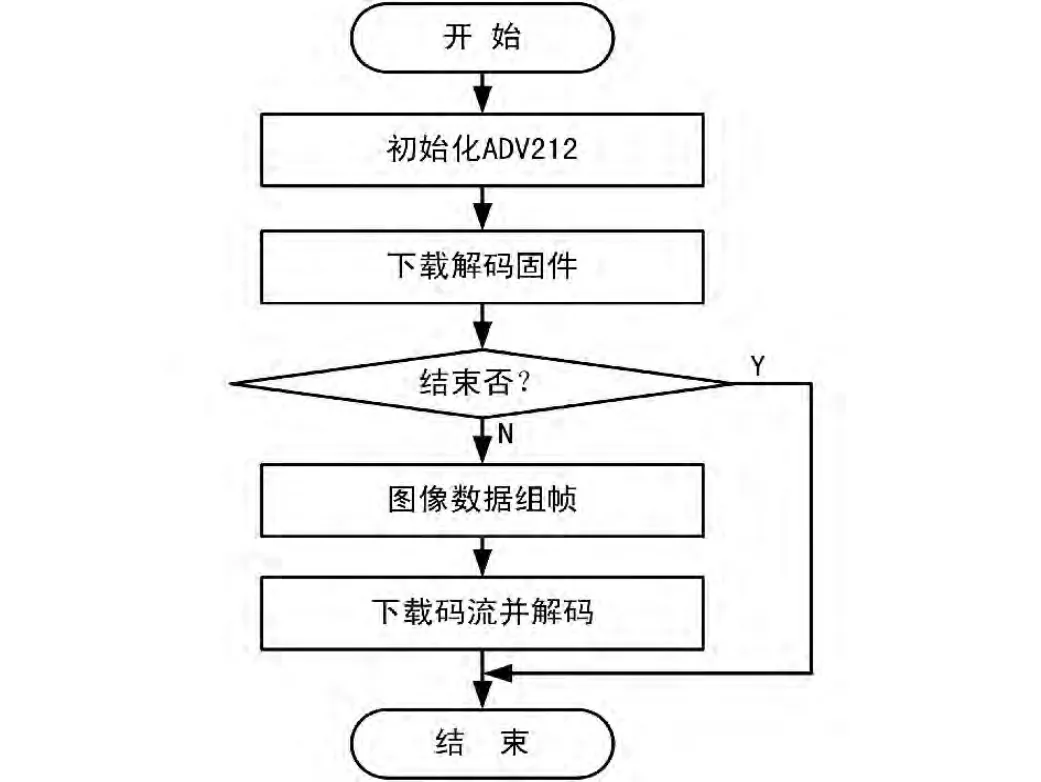

解码系统软件流程如图4所示。

图4 解码软件流程

根据硬件设计,解码系统采用16位HDATA输入、VDATA输出模式。ADV212内部有直接寄存器、间接寄存器、存放固件及其参数的内存区域。在对ADV212的操作过程中,会对内部直接或者间接寄存器进行访问。对直接寄存器的访问操作相对简单,通过总线直接访问对应的直接寄存器即可。而对间接寄存器的访问相对复杂,需要先将间接寄存器的地址分高低16位写入STAGE和IADDR寄存器当中,再访问IDATA寄存器,其流程如图5所示。

图5 ADV212读/写间接寄存器流程

i.MX6Quad操作ADV212的内部寄存器实现对ADV212的初始化、固件下载、码流下载和开始/结束解码等操作,其操作流程如图6所示。

图6 ADV212初始化、固件下载和解码流程

ADV212的初始化工作始于硬件复位,通过i.MX6Quad的GPIO,向ADV212的复位脚发送一个负脉冲信号即可完成硬件复位工作,在全程正常工作过程中,需保持ADV212的复位脚为高电平。将PLL_HI与PLL_LO两个直接寄存器分别设置为0x0008与0x0004来设置ADV212内部PLL时钟为27 MHz,并且设置完这2个寄存器之后,在后续初始化操作进行之前,必须有至少20 μs的延迟,否则会导致错误。接着设置BOOT寄存器为0x008A,设定为非主机模式。设置MMODE寄存器为0x05,设定间接寄存器访问模式为16位及地址自增宽度为16位模式。最后设置BUSMODE寄存器为0x05,设定内部总线宽度为16位。

ADV212的固件有编码用和解码用2种。下载解码固件时将STAGE寄存器设置为0x0005,IADDR寄存器设置为0x0000,然后将固件按顺序写入IDATA寄存器中即可,ADV212内部会自动将IDATA寄存器的数据搬运到内部的RAM当中。将全部固件数据写入IDATA之后,需要设置BOOT寄存器发起一个软复位操作,然后重新设置MMODE和BUSMODE寄存器。接着需要设置固件的运行参数,将STAGE和IADDR寄存器分别设置为0x0005和0x7F00,依次往IDATA寄存器写入从偏移量0x00~0x0B的参数设置值。接着设置EIRQIE寄存器为0x0400,以使能0号软件中断。在设置完固件参数之后需要对下载的固件进行校验,以检验是否正确,校验是通过读取应用程序ID来进行,查询EIRQFLG寄存器,查看0号软件中断是否发生,如果0号软件中断发生,则读取SWFLG寄存器的值,与解码应用程序ID(0xffa2)进行比较,如果两者一致,则说明固件及固件参数已经正确下载及设置,否则需要重新进行初始化及固件下载等操作[12]。

ADV212的解码工作,首先需要设置EIRQFLG寄存器,清除所有中断标志。然后按顺序往CODE寄存器中写入JPEG2000数据。因为在初始化及设置解码参数时已经设置了模式,所以只需不断地往CODE寄存器写入 JPEG2000数据,ADV212的VDATA接口会输出BT.656的信号。

3 实验结果与分析

设计的JPEG2000解码系统已经应用于自主研发的一体化手持测控站中。在模拟测试中,运用自制的测试设备,通过往本解码系统输入压缩的JPEG2000图像数据,计算不同复杂度的完整压缩图像输入到LCD显示屏上显示图像的时间差,多次测试结果表明,视频的延迟时间为40~48 ms。在实际使用中,视频图像延迟时间120~150 ms,由于无人机系统中图像采集设备的延迟以及无线图传的发射端和接收端对图像数据的处理造成的延迟为80~100 ms,由此可以得出本解码系统的视频延迟时间在50 ms以内。

通过测量解码系统的输入电压与电流,计算各个单元的功耗,数据预处理及逻辑控制单元的平均功耗为0.6 W,SDRAM存储器单元功耗为0.4 W,ADV212解码单元功耗为0.1 W,其他约为 0.2 W,总计1.3 W。

在对比实验中,采用了FPGA结合ADV212的方式及软件解码等另外2种方式进行对比。软件解码方式采用开源的Kakadu软件,硬件平台采用主频为2.67 GHZ的酷睿i5 CPU,内存为4 GB的主流硬件配置。实验中采用了Altera公司的EP3C55-F484C8。测试结果如表1所示。由于FPGA的逻辑单元及用户IO不同,会导致资源占用率有较大的不同,故表1未给出其CPU及内存的资源占用率。

表1 不同解码方法测试对比

4 结束语

基于i.MX6Quad与 ADV212的解码系统实现了JPEG2000视频图像的实时解压,系统资源占用率低,且实时性较好,能够解决传统JPEG2000解压缩方式中存在的可靠性差、体积大、功耗高和软件复杂等缺陷。该解码系统设计能够很好地应用于微小型无人机的测控站系统当中,以简化无人机的测控系统,使无人机的操控更加简单方便,最终将使得无人机更加普及。 ■

[1]李艳斌.通信电子战面临的挑战[J].无线电通信技术,2013,39(2):1 -3.

[2]高保生,朱良彬.无人机地空链路信道特性与宽带数据传输[J].无线电工程,2011,41(9):4 -6.

[3]崔弘珂.一种空间环境下的TCP传输技术研究[J].无线电通信技术,2011,37(4):21 -24.

[4]孙志刚,周 越,申冀湘.一种新型小型化宽带无人机机载智能天线研究[J].无线电工程,2013,43(5):42-44.

[5]汤一峰.h.264标准暂不适用于无人机实时视频数据传输[J].航空电子技术,2012,43(2):56 -58.

[6]张 铖,杨奎河,李雅丽,等.视频中运动目标的检测及数据安全传输[J].无线电通信技术,2012,38(2):55-58.

[7]王 丹,杨允基.ADV212编解码芯片原理及应用[J].舰船电子工程,2008,28(5):106 -109.

[8]王 珊.基于ARM9的近程无人机数据采集系统[J].无线电工程,2013,43(8):40 -43.

[9]王保杰,彭 力.嵌入式Linux车载智能中心的设计与实现[J].自动化仪表,2013,34(9):19 -22.

[10]丁建桥,周 磊,张正华.基于IMX53的视频编码的研究与应用[J].无线电通信技术,2014,40(2):86 -89.

[11]刘春风,王惠平,潘利明.基于ADV212的高清视频压缩系统设计[J].电子设计工程,2010,18(3):65 -67.

[12]邓寰伟,赵宝军.基于ADV212的实时图像压缩系统[J].电视技术,2008,32(12):35-37.