基于CPLD和AVR的图像采集系统设计

2014-09-26沈玉德韩桂英

沈玉德,韩桂英

(大连民族学院 信息与通信工程学院,辽宁 大连 116600)

随着社会的不断发展,工业生产和生活领域有许多图像采集和监控需求,并且要求也越来越高,大部分传统的图像监测装置已经不能满足现状而且有价格高、体积大、功耗大、速度慢、精度低等缺点,已不利于大范围的使用和推广。本方案正是以此为出发点,设计一种基于CPLD和AVR的高速、低功耗图像采集系统。目前图像采集常用的两种图像传感器为CCD传感器和CMOS传感器。CCD传感器一般输出模拟信号,需要经过视频解码器解码得到数字信号再传入CPU中处理,而CMOS图像传感器直接输出的是数字信号,可与CPU直接相连,且可直接通过IIC总线来设置图像分辨率大小、曝光、增益等参数,无需再用视频解码器。相对于CCD图像传感器而言,CMOS图像传感器具有功耗低,体积小,传输数据速度快且方便控制等优点。因此CMOS图像传感器更适合应用在微处理器中[1]。CPLD是复杂的可编程逻辑器件,规模大,适合在时序逻辑电路中的应用,在信号处理领域也有广泛的应用[2-4]。根据总体功能设计可用CPLD增加系统的集成性,扩展性等,本系统采用CPLD完成系统所需的逻辑功能以及和SRAM构成快速缓存装置,实现频率不同的AVR单片机和CMOS图像采集系统的连接,同时提高了整个系统模块的控制和开发空间。与传统模式的图像采集系统相比,该系统可以快速采集图像信息以及进行简单的分析处理,且体积小、成本低、功耗低、设计灵活等特点,便于大范围的推广。

1 系统工作原理概述

本采集系统包括了图像采集、逻辑控制、图像缓存与图像处理、传输等4个部分。对比CCD与CMOS图像传感器的各自优缺点,系统选择CMOS数字图像传感器来构建本系统的数字化采集单元;图像存储部分采用CPLD和SRAM相结合的方案对图像数据进行高速缓存;将AVR单片机作为图像采集系统的核心模块控制各个子模块,并对被采集图像数据进行简单处理和传输;利用RS232总线作为图像采集系统与任务机进行图像数据传输的接口,用按键及TFT彩屏实现人机交互,方便系统调试,用SD卡进行图像的外部存储。系统上电时,AVR单片机通过SCCB总线对CMOS图像传感器(OV7670)进行初始化[2],CMOS图像传感器通过CPLD将采集的图像数据写入SRAM中,AVR单片机通过对CPLD内部总线的控制,读取SRAM中的图像数据并进行简单的处理,随后可用TFT彩屏显示图像,并可通过按键模块选择将一帧图像数据存储在SD卡中或通过UART模块传输给上位机进行进一步处理,从而实现了图像采集系统的数字化采集、处理、传输和存储。整个系统由AVR单片机控制管理,大大提高了系统的实时性、稳定性和易维护性。系统总体框图如图1所示。

图1 系统总体框图Fig.1 System framework

本系统采用高性能、低功耗的AVR单片机ATmega128作为系统核心控制器[3-4],主要完成对CMOS图像传感器、TFT彩屏、SD卡的初始化以及控制CPLD内部总线等。CPLD使用Altera公司的EPM240T100C5芯片,生成系统所需的各种逻辑电路和快速读写SRAM功能,大大提高了图像的采集效率。图像采集部分使用CMOS图像传感器OV7670作为图像采集器, OV7670具有标准的SCCB接口,适合低压嵌入式应用,用户可以完全控制图像质量、数据格式和传输方式,并且价格低廉是本系统的不二选择。SRAM选用ISSI公司的IS61LV5128AL芯片,3.3V供电,存储容量为512K字节。本系统选用2.8英寸TFT带触摸屏的ILI9325模块,人机交互快捷方便。图像存储部分采用自弹式SD卡,具有通用性并且便于PC读取的特点。

2 系统硬件设计

2.1 系统主控电路设计

本系统从实际出发,采用性价比高的8位AVR微处理器ATmega128作为CPU来控制其他功能模块,主要功能模块有图像采集模块、CPLD模块、SRAM缓存模块、TFT显示模块、UART模块、SD卡存储模块等。硬件系统工作流程为:1)系统上电后AVR通过SCCB总线接口对图像传感器OV7670进行初始化;2)CPLD根据图像传感器的时序信号进行读写SRAM,将一帧完整的图像数据保存在SRAM中;3)一帧图像采集完成后,AVR通过CPLD读取SRAM中的数据,进行简单的图像处理并且用TFT显示,或者通过串口输出给上位机。

2.2 电源模块设计

本系统采用的Atmega128单片机、MAX II系列CPLD、ILI9325 TFT、SRAM以及SD卡都统一使用3.3 V电压,通过电源转换芯片AMS1117-3.3可将+5 V转换成+3.3 V电压,提供稳定的供电电压。OV7670所需电源模拟电压在2.45~3.0 V之间,可直接串接二极管压降0.7 V后获得2.6 V的电源模拟电压,十分简化了电源电路的复杂程度。

2.3 ATmega128外围电路设计

图2 系统主控电路Fig.2 Main system circuit

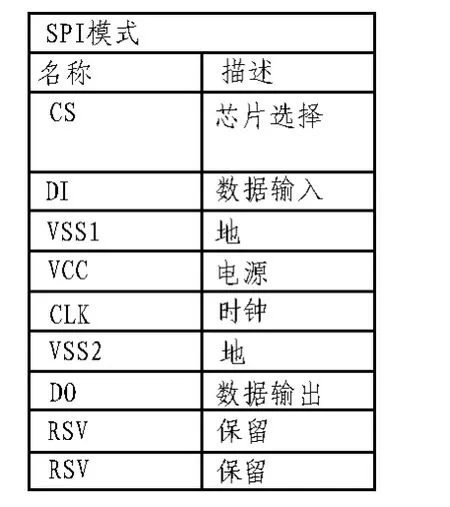

ATmega128的外围电路主要包括晶振模块、复位电路、JTAG在线调试下载接口、SPI模式的SD卡接口电路(可同时接ISP下载接口)、串口通信电路、SCCB总线、TFT控制电路以及数据传输电路等。各模块设计为:1)CPU晶振选用16 MHz;2)JTAG接口与IEEE.1149.1标准兼容,遵循JTAG标准的边界扫描功能;3)SD卡选择SPI模式,其接口定义如图3所示,可同时连接ISP模式的程序下载接口;4)大部分的AVR芯片都含有一个硬件串行通信接口UART,利用该接口可以实现控制系统与PC的通信构成RS-232 的网络,AVR系统输出图像就可以在PC机上显示;5)利用2个I/O口分别接OV7670图像传感器的SDA和SCL,生成SCCB总线,ATmega128直接完成对图像传感器的初始化;6)通过对TFT读写的控制,PC口经8位数据模式连接TFT数据接口,实现人机交互,方便系统调试。

图3 系统主控电路Fig.3 SPI mode of SD

2.4 CPLD外围电路设计

CPLD选 用 了Altera公 司MAX II系 列 中 的EPM240T100C5芯片,通过AVR单片机控制主要完成对SRAM的快速读写,以及生成系统所需逻辑单元;由AVR单片机控制其内部的总线开关确定把CMOS图像采集系统采集的数据是否继续发送,同时单片机控制CPLD内部总线,使CPLD快速对SRAM进行读写操作,并且通过外部中断的方式判断一帧数据的完整性。CPLD对应连接SRAM的地址总线、数据总线和控制总线,同时扩展了信号的输入总线和输出总线,并在CPLD内部构成系统所需逻辑单元,简化了电路的复杂度,提高可靠性[5-6]。SRAM选用ISSI公司的IS61LV5128AL,512k×8bit,总共有(A0...A18)共 19根地址线,8位数据线。图像传感器输出为8位数据,ATmega128位8位微处理器,选用8位SRAM降低了程序编写的难度。SRAM接口图如图4所示。

综上所述,系统在硬件结构设计方面完善合理,尽可能的降低成本,充分利用资源,同时也提高了系统的工作效率和可靠性。

3 系统软件设计

3.1 MCU的程序设计

AVR单片机程序的设计,选用了AVR_GCC编辑器,该编辑器更新速度快,代码效率高,可移植性强。并在AVR Studio中实现模拟仿真。PC机通过JTAG接口,对ATmega128单片机进行在线编程和调试。

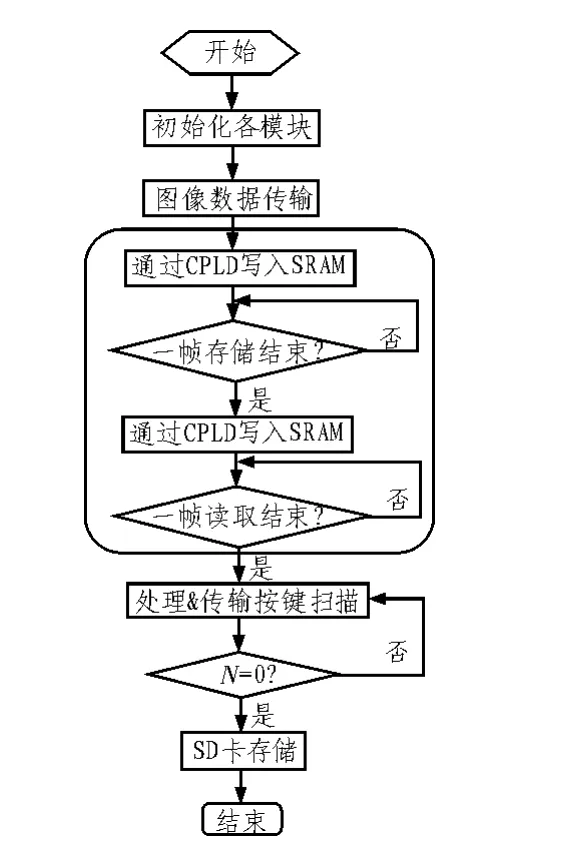

本系统的单片机程序由主程序和中断子程序构成。系统上电后,单片机的主程序对各模块进行初始化,并且完成对显示屏的写操作,等待中断响应通过CPLD从SRAM中读取一帧图像数据;主程序还有扫描判断语句,判断是否有外部触发,如果有外部触发通过CPLD内部总线,只读取SRAM中一帧图像数据,通过简单处理以图片形式存储在SD卡中或通过串口发送并在PC机上进行进一步处理。程序流程如图5所示。

图5 系统程序流程图Fig.5 System program flowchart

3.2 CPLD的程序设计

CPLD于单片机相比,一个非常重要的优势在于它的高速性。尤其在图像采集等需要高速传输数据时非常合适。本系统用的是VHDL语言在QUARTUS Ⅱ 平台进行了调试、仿真、下载。

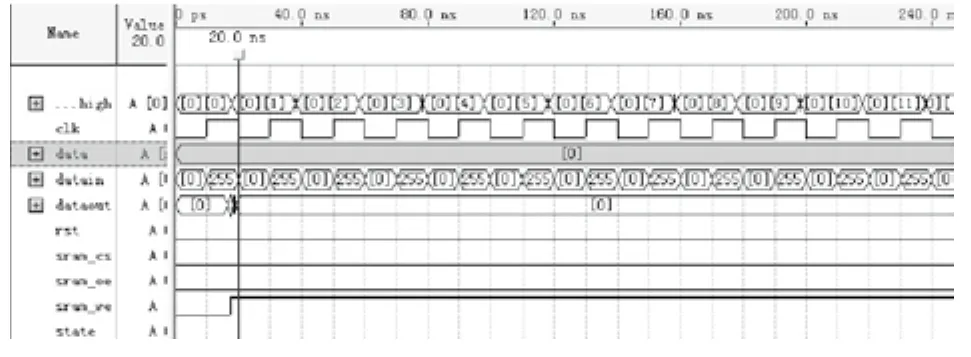

本系统中CPLD的核心作用是快速读写SRAM,主要通过CPLD的内部接口管理电路来实现。系统启动后:CPLD通过OV7670图像传感器为每一个像素数据产生的像素时钟PCLK、行有效时钟HREF和帧同步时钟VSYNC,用来生成读写SRAM相应的地址信号;根据地址信号和AVR单片机提供的读写信号来判断CPLD接口电路的工作状态;最后CPLD根据工作状态,控制数据/地址接口模块进行对应的操作。值得注意的是,CPLD内部各个程序单元都统一由OV7670的像素时钟PCLK驱动,达到整体系统同步的作用。SRAM的片选信号CE、写有效信号WE和读有效信号OE中,根据实践经验可以直接将片选信号CE和读有效信号OE接地,只根据写有效信号WE就可以控制CPLD对SRAM的读写操作,这样一来不仅节省了CPLD和SRAM连接的管脚数,同样也简化了软件的编写。在仿真软件中达到了预期的逻辑控制,确保了图像传感器的正常高速工作。仿真波形如图6所示。

图6 仿真波形Fig.6 SRAM simulation waveform

4 结 论

该系统基于CPLD与AVR构建了图像采集的硬件平台,软件设计采用模块化设计思想,提高了系统的可靠性和维护性。该系统在系统在QUARTUS II软件和AVR Studio中进行了仿真并达到了预期的控制和采集功能。该系统具有功耗低、体积小、传输数据速度快且控制方便等优点,在图像检测及相应的领域具有一定的推广价值。

[1]吴文忠.基于ARM9的CMOS图像采集系统的设计与实现[J].微型机与应用,2011,30:83-86.

WU Wen-zhong.Design and implementation of CMOS image acquisition system based on ARM9[J].Microcomputer & Its Applications,2011,30:83-86.

[2]AH_wangph.OV7670/0V7171CMOS VGA图像传感器[EB/OL].[2010-12-09]. http://wenku.baidu.com/view/796a397816888486 8762d671.html.pdf.

[3]金钟夫.AVR ATmega128单片机C程序设计与实践[M].北京:北京航空航天大学出版社, 2008.

[4]黄任.AVR单片机与CPLD/FPGA综合应用入门[M].北京航空航天大学出版社, 2004.

[5]王道宪.CPLD/FPGA编程逻辑器件应用与开发[M].国防工业出版社, 2004.

[6]孔德明.基于CPLD控制的实用数据采集系统[J].电子产品世界, 2005,19:101-103.

KONG De-ming.A practical data acquisition system based on CPLD[J].Electronic Engineering and Product World, 2005,19:101-103.